LCD控制器的FPGA實現

陳東成,胡敬營,曾范昌

(江蘇自動化研究,江蘇 連云港 222061)

LCD控制器的FPGA實現

陳東成*,胡敬營,曾范昌

(江蘇自動化研究,江蘇 連云港 222061)

為實現PC輸出在LCD原屏上的顯示,設計了一種基于FPGA的LCD控制器,采用IP核搭建系統的框架,系統核心控制CPU采用了Xilinx的MicroBlaze軟核,系統對外通信通過串口實現;通過Xilinx的集成邏輯分析儀IP核ILA在線采集輸入、中間以及輸出數據,驗證系統的可行性及數據處理的正確性;最終的實驗結果表明,所設計的控制器能夠驅動LCD原屏,并且支持多種接口的視頻輸入,顯示畫面穩定,同時實現了兩路視頻的畫中畫顯示,并可作為PC輸出設備及視頻監視設備。

FPGA;視頻接口;LCD控制器;IP核;ILA

計算機的顯示設備已經從傳統的CRT顯示器過度到當前的液晶顯示器,目前液晶顯示器已經是計算機顯示設備的主流,并且顯示器的分辨率正朝著越來越大的方向發展,顯示接口類型也越來越多樣化。常用的顯示器接口類型有VGA、DVI接口,較新型的顯示器具有HDMI或者DisplayPort顯示輸入接口,然而接口中用到的最多的依然是VGA接口,幾乎所有的顯示器均具有VGA接口,主流計算機通常都有VGA和DVI兩類輸出類型。目前生產顯示器的廠商眾多,各大PC廠商均有自己的顯示器品牌,其他公司如三星、AOC等廠商則專門研發生產顯示設備,并占有較大的視場。LCD控制器是顯示器的核心控制部分,用來控制顯示器的輸入類型、使顯示器適應輸入視頻的分辨率以及調整輸入視頻的亮度、對比度等參數。當前各大廠商的LCD控制器多采用專用芯片作為控制核心,芯片的核心技術被少數幾個廠商掌握,國內則在核心芯片方面受國外廠商制約;另外,國外廠商生產的LCD控制器芯片更新換代的周期極快,通常3年~5年就會停產,無法滿足一些國產顯示設備的保障需求。針對以上的問題,設計了一種基于FPGA的LCD控制器,該控制器核心框架由IP核搭建,通過Xilinx的軟核MicroBlaze控制IP和的工作;并且設計的控制器能夠支持多種類型接口的視頻輸入,LCD原屏驅動信號直接由FPGA的LVDS數據給出,對外通過串口實現對系統的控制,能夠滿足某些特殊應用的多功能綜合顯示的需求,并且顯示驅動控制器的核心技術采用IP核實現,將邏輯在FPGA芯片上實現,使得功能不受特定芯片的影響,滿足某些特殊產品保障周期長的要求[1-3]。

所設計的LCD控制器支持普通計算機的常用輸出接口,具有VGA、DVI、HDMI,并且本系統中還添加了PAL/NTSC接口,滿足了科研生產使用中監視器的功能。目前實現了單路多種接口視頻信號的輸入及顯示,已經兩種視頻的畫中畫顯示。在后續的工作中,將研究實現多路視頻的畫面分割顯示以及通過命令選擇任意路視頻的全屏顯示,更加豐富顯示設備的功能,滿足特殊領域的應用。

1 系統設計

設計的LCD控制器主要包括輸入接口、輸出接口、解碼模塊、數據緩存模塊、串口控制、電源模塊、外部存儲模塊以及FPGA核心處理模塊幾個部分,系統框圖如圖1所示,以下分別介紹各個部分的組成及功能。

圖1 系統功能框圖

圖2 LCD原屏驅動時序圖

1.1 輸出顯示接口設計

本文所采用的LCD原屏是SHARP的TFT-LCD模塊,該屏的分辨率為1 600×1 200,驅動數據為24 bit數據,分為R、G、B 3種數據,每種數據占8 bit。LCD的對外接口為兩場800×1 200的LVDS信號,每場信號有4對數據線和一對時鐘線[4]。圖2為LCD原屏的LVDS驅動數據協議時序,由圖可知LVDS信號中包含了所有的圖像數據信息以及視頻的同步信息。系統的圖像數據在FPGA內根據顯示屏的驅動接口協議進行編碼,通過LVDS信號引腳輸出,直接驅動LCD原屏[5-6]。

1.2 視頻輸入模塊

系統采用了ADV7842作為視頻解碼芯片,該芯片可解碼多種類型的視頻信號,包括HDMI、DVI、VGA以及PAL/NTSC接口類型的視頻,這包含了顯示器常用的接口類型。解碼芯片支持HDMI 1.4a協議,由于DVI與HDMI的兼容性,并且該芯片有兩組HDMI解碼接口,因此該芯片同時也能夠解碼DVI 1.0信號。該解碼芯片的模擬視頻接口支持VGA,最大支持1 920×1 200@75 frame/s的UXGA模擬視頻。視頻解碼后的輸出格式可選擇RGB或YCbCr格式,對于PAL/NTSC制的各行掃描視頻可轉換成逐行掃描視頻輸出。該解碼芯片的上述幾種數據接口并行存在,但是同一時刻只能有一種接口工作,滿足了顯示器多種接口類型的要求[7]。

1.3 數據緩存單元設計

由于所設計的LCD控制器支持多種分辨率的視頻輸入,將輸入的視頻都將在一塊1 600×1 200的LCD顯示屏上輸出,對于輸入分辨率不等于1 600×1 200的視頻,需要將視頻轉換成1 600×1 200的分辨率輸出顯示,然而所用的FPGA資源寶貴并且非常有限,并且系統需要緩存的數據量較大,片上資源無法滿足需求,因此這里采用外部DDR3存儲芯片作為數據處理的中間緩存芯片。系統目前的硬件設計是4路輸入視頻,為后續研究4路畫面分割器等其他功能做了準備,并且為以后3 840×2 160視頻的顯示設備的研發做準備,系統在設計時采用了4片DDR3芯片組成了64 bit的外部存儲空間,DDR3芯片的實際運行速度可達800 MHz,這里設DDR3的對寫效率為60%,那么系統的外部緩存帶寬可達800 MHz×2×64 bit×60%=7.68 Gbit/s,完全滿足系統的帶寬要求,也足以支持幀頻為60幀的3 840×2 160視頻的數據緩存需要。

1.4 FPGA處理單元設計

FPGA作為系統的核心處理單元承擔絕大部分數據處理任務,FPGA采用Xilinx的XC7V485T系列芯片,該芯片片上資源豐富,滿足系統當前的資源需求,同時也能夠滿足3 840×2 160視頻顯示控制系統開發的需求。開發環境采用Xilinx公司專門用來開發7系列FPGA的集成開發環境vivado,該開發環境可通過圖形化界面操作,用多種ip核模塊搭建復雜的數據處理系統[8]。

圖3 FPGA內部功能框圖

圖4 MicroBlaze軟核處理器結構

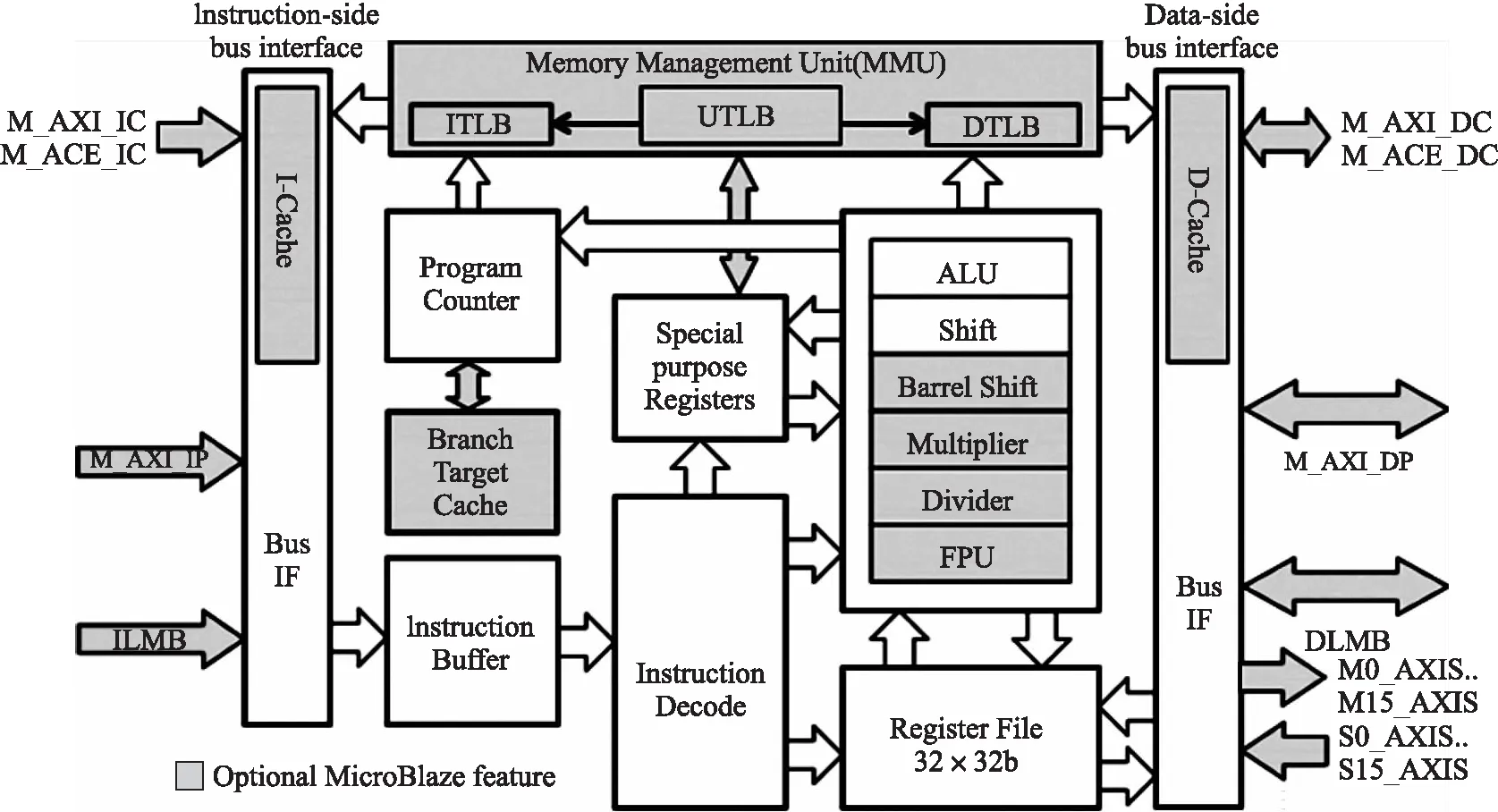

系統的核心處理工作均在FPGA中完成,數據在FPGA中的處理流程原理框圖如圖3所示,圖3所示為系統的關鍵IP核,MicroBlaze核是系統的控制核心,通過axi總線同LogiWin、LogiCVC以及MIG等IP核進行數據交換,控制IP核的工作模式。圖像數據通過解碼芯片解碼輸入到FPGA中的LogiWin核,該核的作用是對輸入的圖像做初步的處理,如輸入圖像和LCD的分辨率不匹配時,該IP核能夠將圖像縮放到LCD分辨率的尺寸,該IP核也能夠對輸入數據做顏色空間以及亮度、對比度等基本的圖像變換,由于系統將實現輸入視頻的畫中畫顯示,因而系統采用了兩個LogiWin核,每一個核對應了一個解碼芯片輸出;LogiWin處理過的圖像通過MIG核存儲到片外DDR3。以便LogiCVC核從中讀取數據,DDR3的另一個作用是輸入輸出幀率的轉換,系統中輸出LCD的幀率是60 frame/s,而當輸入數據為模擬視頻PAL時,其幀頻只有25幀,通過DDR3就能夠使輸出、輸入幀頻平緩過渡;LogiCVC核的作用是按照LCD的接口協議生成標準視頻時序,同時LogiCVC從DDR3中讀取視頻數據插入到生成的標準視頻時序中,如需將兩路輸入視頻合成一路畫中畫視頻輸出,LogiCVC則可將一路作為背景,另一路在圖像的任意位置輸出。由于本系統所用的LCD原屏的驅動數據有兩場LVDS信號,這里采用編寫的Single to Dual核將LogiCVC輸出的并行LCD驅動時序按奇偶時鐘分成兩組并行數據,分完的兩組并行數據通過parellel to LVDS核轉成LVDS信號輸出直接驅動LCD原屏。

另外,系統所采用的解碼芯片ADV7842需通過IIC總線配置工作模式,系統采用FPGA中的IIC核作為控制接口,控制核心MicroBlaze將IIC控制數據通過IP核發送到ADV7842;外部的控制命令通過串口發送到FPGA,使得系統能夠根據命令情況配置ADV7842的工作方式,同時也能夠將系統當前的狀態發送到外部控制單元,系統的外部控制接口采用串口IP核,該核作為外部控制核心與MicroBlaze的傳輸中介,使得系統能夠與外部友好交互;由于VGA視頻支持的分辨率有很多種,對于目前的VGA視頻解碼芯片,通常都不能自適應不同分辨率的VGA視頻,這里在LogiCVC輸出端添加了vag_adapt核來判斷是否有視頻輸入,如無視頻輸入,則vag_adapt核向GPIO核發送狀態信號,GPIO向控制核心發出中斷,使得系統能夠自適應VGA輸入;本LCD控制器系統的復雜性較高,綜合后生成的bit文件較大,如直接將其燒寫到Flash中,在系統上電啟動時,由于系統中存儲程序的ram存儲資源有限,導致程序無法自啟動,系統上電用Bootloader通過SPI將Flash中的程序引導到DDR3中,系統從DDR3執行程序,這樣可以實現程序上電的自啟動[9-10]。

2 MicroBlaze程序設計

所設計的LCD控制系統的FPGA設計部分包括硬件語言設計以及軟件語言設計兩部分,系統的硬件語言設計部分即上述通過IP核搭建系統的框架,所用的IP核為自己設計或Xilinx官方提供的IP核,框架搭建完成后即可生成相應的硬件描述語言。系統的核心控制工作有MicroBlaze軟核來完成,該軟核是一種針對Xilinx FPGA器件而優化的功能強大的32位處理器,是業界最快的軟處理器IP核解決方案,支持CoreConnect總線的標準外設合集,具有兼容性和重復利用性,最精簡的核只需將近400個Slice,軟件程序用C語言編寫[11]。圖4為MicroBlaze軟核處理器結構。

2.1 初始化設計

這里的核心控制MicroBlaze控制著整個系統中各個模塊的初始化、工作模式的配置以及對數據的處理,軟件控制程序占了整個系統工作量的一半以上。程序開始首先要初始化MicroBlaze軟核,使MicroBlaze能夠正常工作,然后通過IIC核初始化解碼芯片ADV7842,配置解碼芯片的工作模式;第3初始化視頻讀取IP核LogiCVC,配置IP核工作方式以及讀取數據映射的內存地址;第4配置圖像處理IP核LogiWin,配置IP核的工作方式以及處理完的數據存儲的地址;最后就是設置控制單元接口的中斷方式,即設置串口模塊的中斷觸發方式及GPIO中斷的出發方式[12]。

2.2 串口中斷設計

系統的串口中斷主要用來控制信號源的切換、輸入圖像的任意比例縮放處理等。當串口收發單元收到外部向系統發送命令時,串口單元立即向MicroBlaze核產生中斷信號,程序進入串口中斷處理部分,在中斷中首先判斷所接收到的命令,如接收到的是信號源的切換,則此時MicroBlaze核將ADV7842的控制命令通過IIC核發送到ADV7842,使得其切換解碼信號源及解碼方式,如接收到其他控制命令,則在中斷中進行相應的處理。

圖5 MicroBlaze軟件流程圖

2.3 VGA分辨率自適應設計

圖5為系統軟件流程圖。當輸入的VGA視頻分辨率發生變化時,由于ADV7842并不能自適應輸入視頻分辨率的變化,此時解碼芯片輸出的數據為0,通過設計的vga_adapt核對解碼芯片輸出的數據進行統計分析,如判斷此時無輸入數據,則vga_adapt核將狀態發送到GPIO核,此時GPIO核向MicroBlaze核發出中斷,MicroBlaze核通過IIC核將ADV7842的配置參數發送到ADV7842,使得ADV7842的支持分辨率切換,如此輪詢所有分辨率,直到ADV7842能夠輸出有效數據,此時vga_adapt核則不再向GPIO核發送切換分辨率狀態。

3 實驗及討論

所設計的基于FPGA的LCD控制器支持VGA、DVI、HDMI以及PAL/NTSC幾種接口,能夠驅動分辨率為1 600×1 200的LCD原屏。由于系統的主要功能均是在FPGA中以IP核的形式實現的,因而設計過程中的結果驗證能夠影響本系統設計的效率,Xilinx的Vivado為基于IP核的設計過程中的行為驗證提供了很好的解決方案,Vivado的集成邏輯分析儀(ILA)IP核能夠測量任意IP核的任意信號的波形,可根據實際需求設定采集波形的深度,是系統設計過程中驗證各個功能模塊邏輯功能的有力工具[13-14]。

設計過程中,IP核LogiCVC的輸出結果是需要觀測的關鍵數據,而該數據是連接到其他IP核單元的,無法在外部直接通過示波器或邏輯分析儀測試,這里通過ILA核在線測試LogiCVC核輸出結果。圖6為通過ILA核采集的數據,圖中可見,數據的行、場同步、24位數據均正常,因此可判斷LogiCVC單元從內存中讀取的數據正常。在視頻數據處于行、場均有效時有圖像數據,消隱期則數據均為0。另一個核心IP核是LogiWin核,該核將輸入到FPGA的數據進行處理后寫入到DDR3中,這里將LogiWin的axi總線連接到ILA核,觀測axi總線的數據傳輸情況,如圖7所示。由圖7可見,在axi總線寫有效后,WDATA的數據同過MIG寫到DDR3,并且開始寫時,系統根據當前數據情況分配對應的寫地址。寫無效時則無數據輸出到MIG。

圖8(a)為系統的PCB實物圖,圖8(b)、圖8(c)為實驗結果。其中圖8(b)為計算機輸出的VGA圖像在系統驅動的LCD原屏上穩定的顯示,圖8(c)為VGA和PAL兩路視頻同時輸入,其中PAL視頻在VGA視頻中畫中畫顯示效果圖,PAL視頻為外部攝像機實時采集的視頻。

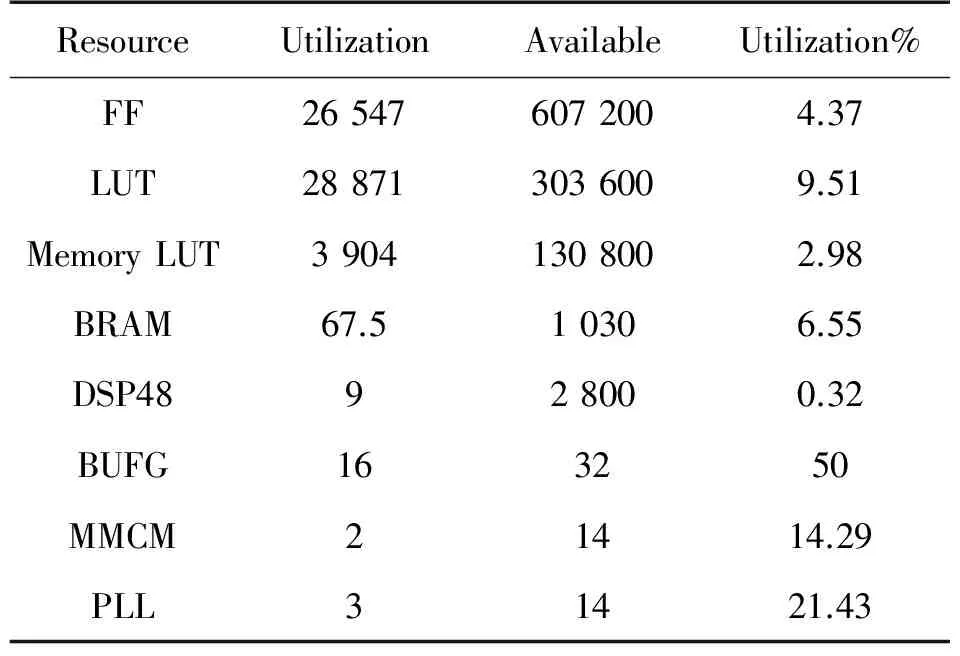

系統選用的V7片上資源豐富,當前設計為功能驗證系統,用來驗證多種類型視頻輸入接口的解碼及在LCD原屏上的顯示,開發畫中畫功能,后面將開發思路視頻的畫面分割顯示功能。以上實驗中實現的功能所消耗的FPGA資源情況如表1所示,從表中可以看出,當前設計消耗了較少的偏上邏輯資源,并且系統中所涉及的信號速度最高為DDR3,遠未達到當前所用FPGA的速度極限,速度級別低于V7的FPGA也可滿足要求,因而后續設計轉化成產品時可以采用邏輯資源較少的芯片,如K7系列FPGA,這樣既保證了所要求的功能,同時又能夠降低生產成本。

圖6 LogiCVC輸出的數據時序

圖7 LogiWin寫入DDR3的時序

圖8 實驗結果圖

ResourceUtilizationAvailableUtilization%FF265476072004.37LUT288713036009.51MemoryLUT39041308002.98BRAM67.510306.55DSP48928000.32BUFG163250MMCM21414.29PLL31421.43

4 結論

所設計的基于FPGA的LCD控制器通過解碼芯片ADV7842將視頻數據輸入到Virterx7 FPGA,在FPGA中通過軟核CPU控制整個系統的工作。核心圖像處理工作由LogiWin核實現,主要實現了圖像尺寸的縮放、顏色空間的轉換以及亮度對比度等基本圖像處理;處理完成的圖像通過MIG核存儲到DDR3存儲器進行緩存;然后通過LogiCVC核從DDR3中將待顯示的數據讀出,通過Single to Dual核將數據分成兩路輸出到LVDS轉換模塊,最終實現驅動LCD。系統的控制功能通過外部串口實現。最終結果表明,本LCD控制器能夠實現多種輸入接口類型視頻的處理及穩定顯示,并且實現了兩路視頻的畫中畫顯示。

[1] 任勇峰,王大偉,石永亮,等. 基于FPGA的視頻轉換系統設計[J]. 電子器件,2016,39(3):655-661.

[2] 王鳴浩,吳小霞. 基于FPGA的通用液晶顯示控制器的設計和實現[J]. 液晶與顯示,2012,27(1):87-92.

[3] 張宇嘉,楊曉非,姚行中. 基于AXI4的衛星接收機DDR3多端口存儲的設計[J]. 電子器件,2016,39(3):617-622.

[4] 梅楠楠. 基于FPGA的特種TV-LCD顯示驅動板的設計與實現[D]. 合肥:合肥工業大學,2007.

[5] 莊聰聰,王大明,李寒. 基于ARM與FPGA的LCD控制器設計[J]. 電子設計工程,2010(6):14-16.

[6] 劉建平,曾文海,黎福海,等. 采用FPGA的LCD轉VGA控制器的設計[J]. 計算機系統應用,2011,20(10):71-73.

[7] Analog Devices. ADV7842 Dual HDMI 1.4 Fast Switching Receiver with 12-Bit,170 MHz Video and Graphics Digitizer and 3D Comb Filter Decoder[G]. 2011.

[8] 孔德彭,陳安妮,周一飛,等. 基于FPGA技術的WSN節點混沌保密通信設計[J]. 傳感技術學報,2015,28(4):557-562.

[9] 俸文炯. 基于FPGA的TFT-LCD視頻驅動系統設計[D]. 北京:北京化工大學,2013.

[10] 王慶春,何曉燕,崔智軍. 基于FPGA的多功能LCD顯示控制器設計[J]. 電子設計工程,2012(23):150-152.

[11] 巫忠正. 基于MicroBlaze的嵌入式系統設計[D]. 南京:南京理工大學,2014.

[12] 龍霞飛,李仁發. Microblaze微處理器IP Core的結構及應用[J]. 微處理機,2004,25(6):6-9.

[13] 李璐,余英. 基于FPGA的LCD動態顯示控制系統設計與實現[J]. 信息系統工程,2016(1):96-97.

[14] 黃玉崗,李杰,秦麗,等. 基于FPGA和ADS8568的彈載實時記錄系統設計[J]. 傳感技術學報,2016,29(4):506-511.

TheImplementationoftheLCDControllerUsingFPGA

CHENDongcheng*,HUJingying,ZENGFanchang

(Jiangsu Automation Research Institute,Lianyungang Jiangsu 222061,China)

In order to display computer video on LCD,a LCD controller based on FPGA is designed. The system is formed of IP cores. The controlling CPU is Xilinx Microblaze soft core. The communication between PC and microblaze is the UART port. In order to survey the signals in the FPGA to identify the logic,the Xilinx integrated logic analyser IP core ILA is used to survey the critical signals. The result shows that the designed controller based on FPGA can drive the LCD,the system supports several kinds of video ports. The picture in picture displaying has been achived. The displaying picture is stable,which can be used as PC displaying device or displaying other videos.

FPGA;video port;LCD controller;IP core;ILA

10.3969/j.issn.1005-9490.2017.05.013

2016-08-29修改日期2016-11-21

TN941.1

A

1005-9490(2017)05-1115-06

陳東成(1987-),男,江蘇連云港人,博士,江蘇自動化研究所高級工程師,主要顯示設備的研發,DSP、FPGA的應用研究,chendongcheng8710@163.com。