氣 動 機 械 手 控 制 實 驗 系 統 設 計

董 勝, 武廣斌, 耿德旭, 王佳南, 王夢龍

(北華大學 a. 電氣信息工程學院; b. 工程訓練中心, 吉林 吉林 132021)

氣動機械手控制實驗系統設計

董 勝a, 武廣斌b, 耿德旭b, 王佳南a, 王夢龍a

(北華大學 a. 電氣信息工程學院; b. 工程訓練中心, 吉林 吉林 132021)

利用TMS320VC5509A和EP2C8Q208設計實現了一個氣動機械手實驗控制系統,通過DSP C和FPGA VerilogHDL語言編程取代了體積龐大的PLC控制系統,實現了20路電磁換向閥控制。16路10 bit DAC精確控制比例閥電壓從而控制氣動機械手指的動作力度,利用8路10 bit ADC采集指端觸感壓力傳感器壓力信號并且完成波形顯示,提供機械手指的握力反饋信息,提高了機械手的控制精度和控制速度。

TMS320VC5509A; EP2C8Q208; 氣動機械手

0 引 言

工業機械手是一種在程序指令控制下,模擬人手的抓取、搬運等動作而設計的機電一體化設備[1]。氣動機械手具有操作方便、拆卸簡單,適用于學生教學的特點[2]。近年來研究表明,采用氣動柔性關節研制的機械手具有較好的綜合柔性,從仿生角度具備了人手的結構和功能特點[3],但是氣動技術本身存在一些難以克服的缺點,所以采用一般的控制方式,很難實現氣動機械手高精度控制[4]。

TMS320VC5509A (DSP)指令周期可達到5 ns,200 MHz的時鐘頻率,3個多通道緩沖串口,采用指令流水線以及片內乘法累加器技術[5]適用于信號的高速分析與處理,但是I/O端口數量有限;EP2C8Q208(FPGA)具有36個M4K存儲塊,總RAM bits達到165 888,可以實現包括:單端口、雙端口存儲器,FIFO等多種存儲器架構,芯片外圍引腳多達208個,除了時鐘、電源等專用引腳外,仍具有相當豐富的I/O資源[6-7]。本文將DSP和FPGA兩者有機結合,運用在氣動機械手實驗控制系統的設計中,可以提高控制精度,減小設備體積。

1 氣動機械手控制系統工作原理及設計指標

氣動機械手控制系統工作原理是通過電磁閥控制機械手氣動回路,實現機械手指的動作,通過控制比例閥控制氣壓的大小,通過指端的壓力傳感器實時采集手指壓力信息,從而控制手指執行動作的力度。指端壓力傳感器采用Honeywell FS系列惠斯頓電橋壓力傳感器FSG015WN[8],通過深圳市捷晟達科技有限公司生產的JSD系列壓力應變橋隔離變送器[9],將壓力信號轉換成電壓信號。電磁閥采用SMC公司生產的SYJ系列3通先導式電磁閥,電源電壓直流24 V,功率0.4 W。比例閥采用SMC公司生產的ITV0000系列比例閥ITV0050,電源電壓直流24 V / 0.12 A,輸入控制信號電壓0~5 V。

本文的氣動機械手控制系統設計指標要求如下:① 輸出20路電磁換向閥控制開關量。每路輸出+24 V / >20 mA;② 輸出16通道的比例閥控制電壓。比例閥控制電壓0~3 V,比例閥輸入阻抗10 kΩ,要求控制電壓精度不低于10 mV;③ 8個輸入A/D通道。采集8個壓力傳感器輸出的模擬電信號,每個壓力傳感器輸出電壓經過處理后為0~3 V/<10 mA,要求A/D電壓分辨率不低于10 mV。

2 系統硬件設計

2.1 DSP平臺選擇

由于機械手控制關系復雜,實時性要求較高,本文選擇北京精儀達盛科技有限公司生產的以TMS320VC5509A定點數字信號處理器(DSP)為核心的Techv-5509 DSP開發板,完成氣動機械手控制系統的信息采集與控制指令的發出[10]。氣動機械手控制系統硬件結構框圖見圖1。

圖1 氣動機械手控制系統硬件結構框圖

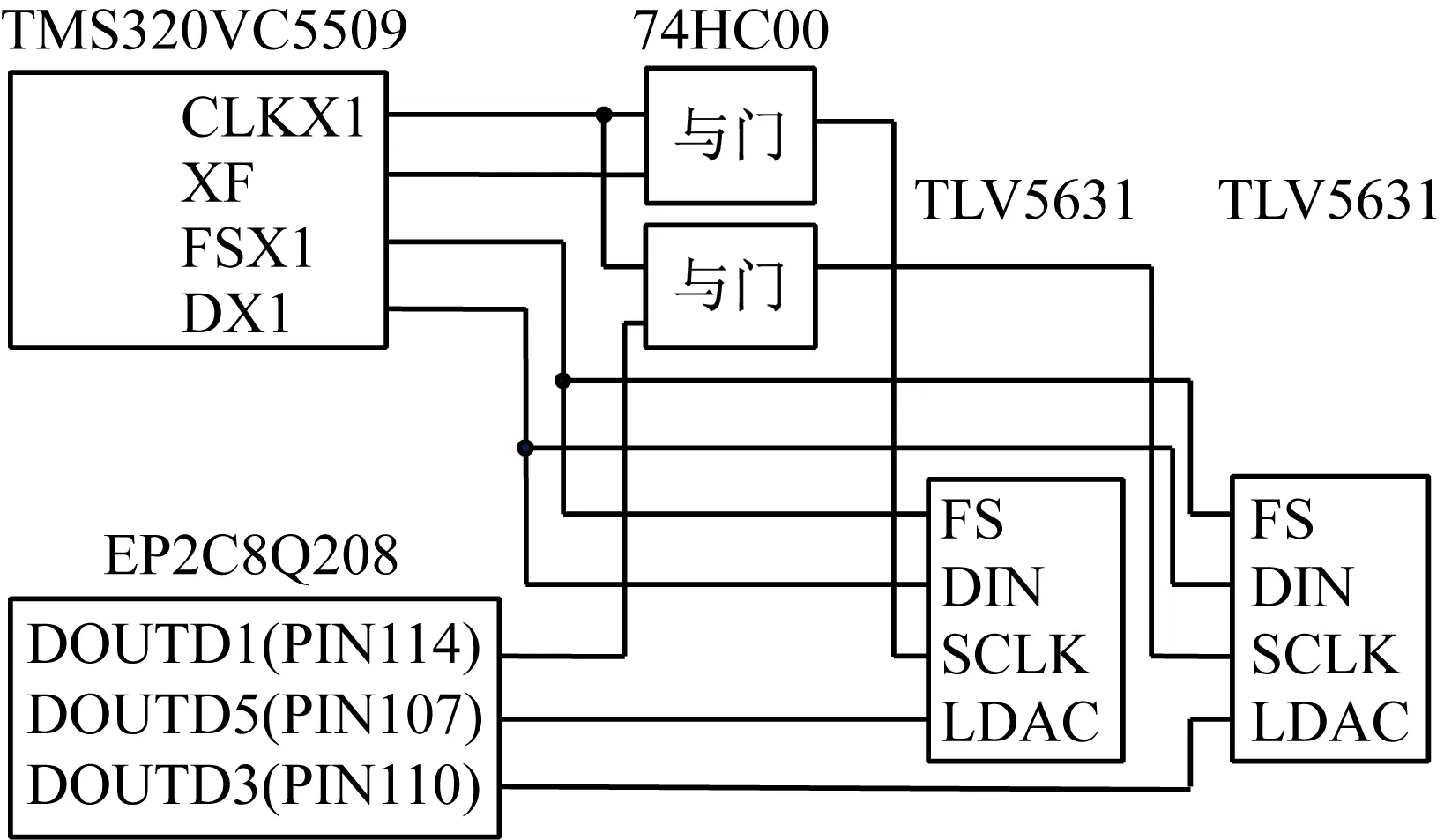

2.2 D / A模塊與DSP接口電路設計

TLV5631是一個8通道,帶有內部電壓基準的10 bit數模轉換器,可通過編程選擇基準電壓為1.024 V或者2.048 V,滿量程動態輸出設定時間可達到1 μs,電壓分辨率可達到2 mV[11],滿足設計要求,本文通過2片TLV5631實現16通道D/A。如圖2所示,利用DSP的MCBSP串口1驅動2片并聯的TLV5631的幀同步和串行數據收發,利用FPGA的DOUTD3、DOUTD5端口通過VerilogHDL編程實現2個芯片輸出地址區分,這樣做要比級聯模式具有更快的控制速度,同時為了防止時鐘輸出相互干擾,通過DSP的XF引腳和FPGA的DOUTD1端口分時關斷2個D/A轉換器的時鐘信號。

圖2 TLV5631與DSP接口電路

2.3 A/D模塊與DSP接口電路設計

TLV1570是一個8通道10 bitA/D轉換器,采樣速率 1.25 MS/s,可以通過編程選擇內部基準電壓為:2.3 V或3.8 V[12],電壓分辨率滿足不低于10 mV要求。

本文利用DSP的MCBSP串口0驅動1片TLV1570,利用FPGA的DOUTD7端口通過VerilogHDL編程實現芯片的片選地址CS輸出,具體接口電路見圖3。

圖3 TLV1570與DSP的接口電路圖

2.4 FPGA芯片選型及其與DSP接口電路設計

為了擴展8通道10 bit A/D輸入,16路10 bitD/A輸出,以及20路電磁閥控制輸出,本文采用芯驛電子科技(上海)有限公司生產的以CycloneII 系列EP2C8Q208芯片作為主芯片的FPGA核心板[13],其與DSP接口電路設計見圖4。圖中,DOUTA[7..0]、DOUTB[7..0]、DOUTC[7..0]用于輸出驅動20路電磁閥的開關量。

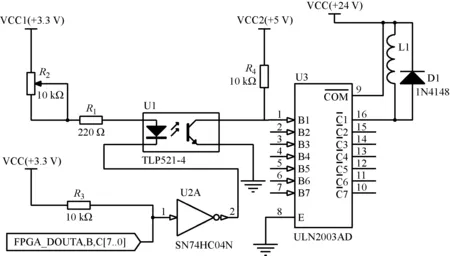

2.5 FPGA驅動20路電磁閥電路設計

DOUTA [7..0]、DOUTB[7..0]、DOUTC[7..0]用于輸出驅動20路電磁閥,FPGA驅動電磁閥電路設計如圖5所示。由于具有完全相同的電路結構,圖5僅畫出其中一路。

圖4 FPGA芯片與DSP接口電路

圖5 FPGA驅動20路電磁閥電路

根據設計要求中的負載負荷計算,本文采用高電壓(50 V)、大電流(單路輸出500 mA)7路輸出的達林頓晶體管陣列ULN2003A控制電磁閥L1[14],1N4148型二極管D1用于反電勢滅弧保護,TLP521-4型4通道光電耦合器U1負責隔離控制部分和執行部分[15]。

3 系統軟件程序設計

3.1 DSP程序設計

(1) A/D采集壓力與波形顯示程序設計。

#define A_D_CS_1((*(unsigned int *)(0x040100))|=0x0080)

#define A_D_CS_0((*(unsigned int *)(0x040100))&=0x007F)

#define DA_1_LDAC_1((*(unsigned int *)(0x040100))|=0x0008)

#define DA_1_LDAC_0((*(unsigned int *)(0x040100))&=0x00F7)

#define DA_2_LDAC_1((*(unsigned int *)(0x040100))|=0x0020)

#define DA_2_LDAC_0 ((*(unsigned int *)(0x040100))&=0x00DF)

#define DA_1_SCLK_EN ((*(unsigned int *)(0x040100))|=0x0002)

#define DA_1_SCLK_NO ((*(unsigned int *)(0x040100))&=0x00FD)

static volatile MCBSP_Handle MyMcbsp0;

static volatile ulint writeBuff[TLV1570_BUFF_SIZE];

static MCBSP_Config Tlv1570_Config={ 0x1000, 0x0000, 0x0040, 0x0001, 0x0040, 0x0001, 0x0230, 0x200F, 0x0000, 0x0000, 0x0A08, 0x0000,0x0000,0x0000,0x0000, 0x0000,0x0000,0x0000,0x0000, 0x0000,0x0000,0x0000,0x0000, 0x0000,0x0000, 0x0000,0x0000};

初始化串口程序:

void tlv_1570_init(void)

{ A_D_CS_1;

mcbsp0_init();}

void mcbsp0_init(void)

{ MyMcbsp0=MCBSP_open(MCBSP_PORT0,MCBSP_OPEN_RESET);

MCBSP_config (MyMcbsp0,&Tlv1570_Config); }[16]

void mcbsp0_start(void)

{ MCBSP_start(MyMcbsp0,MCBSP_SRGR_START, 0x1000);

MCBSP_start(MyMcbsp0,MCBSP_SRGR_FRAMESYNC,0x1000);

MCBSP_start(MyMcbsp0,MCBSP_XMIT_START|MCBSP_RCV_START,0x3000);}

void mcbsp0_close(void)

{ MCBSP_close(MyMcbsp0);}

void mcbsp0_write(uint data)

{ A_D_CS_1;

delayUs_SYS(5);

A_D_CS_0;

DXR1_0=data;

while ((SPCR2_0 &0x0002)==0);

delayUs_SYS(10);

A_D_CS_1;}

(2) D/A驅動比例閥程序。

void da_conv_1( unsigned int valueA,unsigned int valueB,unsigned int valueC,unsigned int valueD, unsigned int valueE,unsigned int valueF,unsigned int valueG,unsigned int valueH)

{ int i=0;

unsigned int da_1_value_tem[8];

DA_2_LDAC_1;

DA_1_SCLK_EN;

asm(" bit(st1, 13) = 0" );

delayUs_SYS(20);

da_1_value_tem[0]=valueA;

da_1_value_tem[1]=valueB;

da_1_value_tem[2]=valueC;

da_1_value_tem[3]=valueD;

da_1_value_tem[4]=valueE;

da_1_value_tem[5]=valueF;

da_1_value_tem[6]=valueG;

da_1_value_tem[7]=valueH;

for (i=0;i<8;i++)

{ da_1_value[i]=da_1_value_tem[i]; }

for(i=0;i<8;i++)

{ mcbsp1_write((i<<12)+ da_1_value_tem[i]);

delayUs_SYS(2); }

DA_1_LDAC_0;

delayUs_SYS(200);

DA_1_LDAC_1;

DA_1_SCLK_NO;}

(3) DSP 驅動FPGA程序。

#define DS_FPGA_WORDA (*(unsigned int *)(0x040800))

#define DS_FPGA_WORDB (*(unsigned int *)(0x040400))

#define DS_FPGA_WORDC (*(unsigned int *)(0x040200))

#define DS_FPGA_WORDD (*(unsigned int *)(0x040100))

extern unsigned int key_flag;

extern unsigned int read_key();

void fpga_io_out()

{ while(1)

{ DS_FPGA_WORDA=0x0080;

DS_FPGA_WORDB=0x0080;

delayMs_SYS(1500);

delayMs_SYS(1500);

DS_FPGA_WORDA=0x0000;

DS_FPGA_WORDB=0x0000;

delayMs_SYS(1500);

delayMs_SYS(1500);

if(key_flag!=0)

if(read_key() == KEY_CANCEL) break;}}

3.2 FPGA程序設計

(1) 頂層設計圖。利用VerilogHDL語句實現的頂層設計見圖6。

圖6 VerilogHDL語句實現的頂層設計

(2) 核心控制模塊的VerilogHDL程序設計。

module gongxun(CLK,DIN,AIN,CE0,ARE,AWE,DOUTA,DOUTB,DOUTC,DOUTD);

input[7:0]DIN;

input[4:0]AIN;

input CLK,CE0,ARE,AWE;

output reg [7:0]DOUTA,DOUTB,DOUTC,DOUTD;

reg[7:0]data_temp=0;

reg[4:0]ain_tem=0;

reg [1:0]curent_state,next_state;

parameter st0=0,st1=1,st2=2,st3=3;

always@(posedge CLK)

begin

curent_state=next_state;

end

always@(curent_state or AWE or CE0 )

begin

if((CE0==1)&&(AWE==1))next_state=st0;

else

begin

case (curent_state)

2'b00: begin if((CE0==0)&&(AWE==0))next_state=st1;

else next_state=st0;

end

2'b01: begin if((CE0==0)&&(AWE==1))next_state=st2;

else next_state=st1;

end

2'b10: begin ain_tem <=AIN;

data_temp <=DIN;

next_state=st3;

end

2'b11: begin case (ain_tem)

5'b01000: DOUTA<=data_temp;

5'b00100: DOUTB<=data_temp;

5'b00010: DOUTC<=data_temp;

5'b00001: DOUTD<=data_temp;

default:

begin

DOUTA<=0;

DOUTB<=0;

DOUTC<=0;

DOUTD<=0;

end

endcase

next_state=st0;

end

default: next_state=st0;

endcase

end

end

endmodule

4 系統調試與結果分析

4.1 16路D/A測試

(1) 利用DSP C語言編程驅動16路D/A輸出不同幅度的方波信號,利用示波器分別跟蹤各個通道的波形及幅度顯示均正常。

(2) 將D/A輸出端連接到比例閥控制輸入端口,在0~3 V范圍內改變D/A輸出電壓值,根據比例閥的參數,控制電壓:0~5 V,對應的輸出壓力范圍:0.001~0.9 MPa,D/A轉換器10位的分辨率,基準電壓Uref為2 V,D/A輸入數值0x200,比例閥輸出氣壓按下式計算:

實際測試比例閥輸出與給定值之間的誤差滿足設計要求。根據實際需要可以通過選用更高分辨率的D/A,以及調整基準電壓值,采取濾波等措施進一步提高控制精度。

4.2 8通道A/D采集測試

用手指按壓指端的壓力傳感器,利用示波器分別對每個通道的壓力變送器輸出信號進行檢測,波形跟蹤變化顯示正常,同時觀察176×220分辨率的TFT_LCD顯示的單個通道的壓力實時跟蹤波形正常。

利用DSPC語言編程驅動FPGA分別控制20路電磁換向閥工作正常。

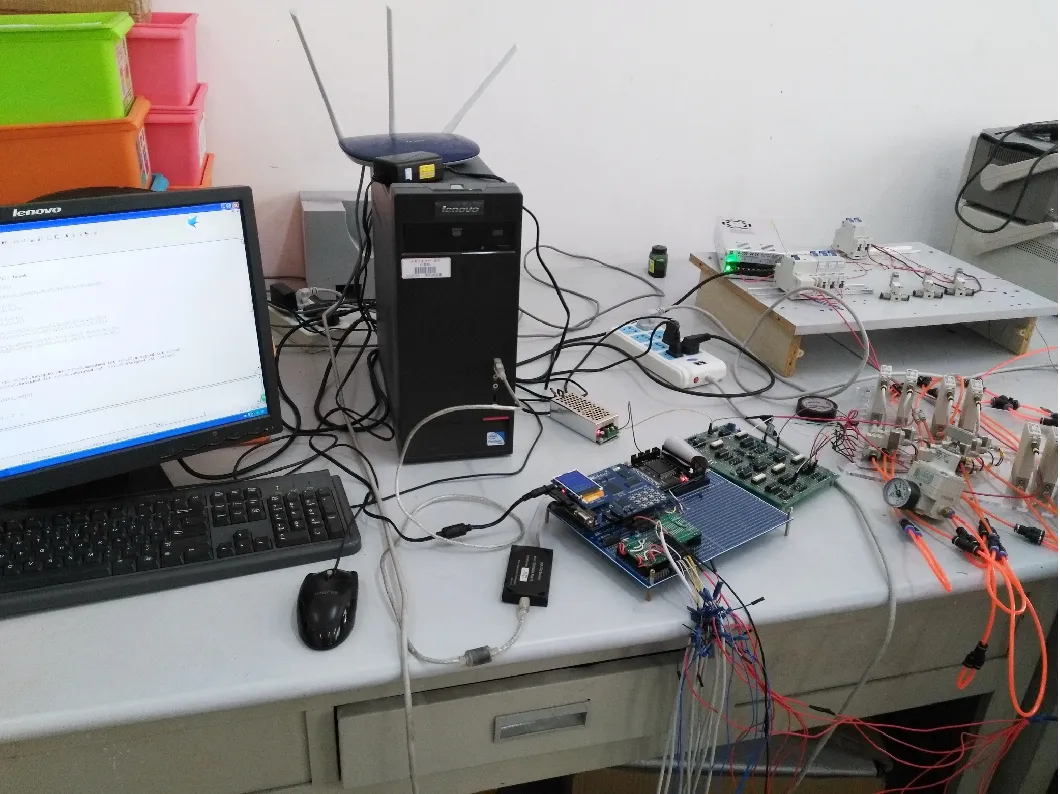

4.3 系統實物圖

控制部分實物見圖7,松手控制結果見圖8,握拳控制結果見圖9(說明:由于系統體積較大,實驗調試過程僅接入了部分電磁閥和比例閥)。

圖7 控制部分實物圖

圖8 松手控制結果圖9 握拳控制結果

5 結 語

本文綜合利用FPGA、DSP實現了氣動機械手控制系統教學案例設計,替代了體積龐大的PLC控制設備,提高了控制速度和控制精度,給學生提供了良好的創新鍛煉平臺,對電子系統設計、DSP技術及應用、EDA技術及應用、傳感器技術課程的綜合實踐教學起到了積極的促進作用。

不足之處,由于顯示屏尺寸較小無法同時顯示8個A/D通道波形,只能分開單獨顯示,需要將來通過換大屏幕顯示器來改進。

[1] 唐少琴. 基于PLC的氣動機械手控制系統設計[J]. 機械設計與制造工程,2016,45( 5):59-61.

[2] 李 碩,唐勤生,王朝兵. 教學用氣動機械手的研制[J]. 科技資訊,2016( 2):39-40.

[3] 劉曉敏,耿德旭,趙云偉,等. 氣動柔性五指機械手結構設計及其抓取實驗[J]. 機床與液壓,2015,43( 7):10-12,70.

[4] 王偉偉,陳冰冰,舒 嫚. 基于比例閥控缸的氣動機械手柔性定位[J]. 東華大學學報(自然科學版),2016,42( 2):248-252.

[5] TI.TMS320VC5509A Fixed-Point Digital Signal Processor Data Manual. EB/OL].[2008].http://www.ti.com.

[6] ALTERA. Cyclone II Device Handbook, Volume 1. [EB/OL].[2008].http://www.altera.com.

[7] ALTERA. Cyclone II EP2C8 & EP2C8A Device Pin-Out( PT-EP2C8-1.9). [EB/OL].[2008].http://www.ti.com.

[8] Honeywell. FSG系列觸力傳感器[EB/OL].[2016]. https://sensing.honeywell.com.cn/_onelink_/honeywell/en2zh/pdfs/Datasheet_%20FSG_CN.pdf.

[9] JSD. 隔離變送器產品說明.[ EB/OL].[2016]. http://www.jsd-iae.com/Isolation_Transmitter.htm.

[10] Techvshine. TechV-5509使用說明書[EB/OL].[2009].http://www.techshine.com.

[11] TI. SLAS269F -MAY 2000-REVISED NOVEMBER 2008.[ EB/OL].[2008].http://www.ti.com.

[12] TI. SLAS169B - DECEMBER 1997- REVISED OCTOBER 2000[EB/OL].[2000].www.ti.com.

[13] Alinx. FPGA核心模塊.[EB/OL].[2016]. http://www.alinx.cn.

[14] TI. SLRS027O -DECEMBER 1976-REVISED JANUARY 2016[EB/OL].[2016].www.ti.com.

[15] TOSHIBA. TLP521-4.PDF[EB/OL].[2000]. http://www.toshiba.com.cn.

[16] 華 晶,賈 晶,殷 華. 基于DSP的通用語音信號處理系統設計[J].電腦編程技巧與維護,2012 ( 5):58-59,73.

DesignofPneumaticManipulatorExperimentControlSystem

DONGShenga,WUGuangbinb,GENGDexub,WANGJianana,WANGMenglonga

(a. College of Electrical and Information Engineering; b. Engineering Training Center, Beihua University, Jilin 132021, Jilin, China)

TMS320VC5509A and EP2C8Q208 are used to design a pneumatic manipulator experiment control system. The system uses DSP C and FPGA VerilogHDL languages programing to take the place of big volume PLC control system, and accomplishes the control of 20 channels electromagnetic directional valves. It accurately controls 16 channels proportional valves by using 10 bit DACs, controls the action intensity of manipulators. It also completes acquisition of signals of the tactility pressure on finger tips of manipulators, by 8 channels of 10 bit ADCs and displays waveforms, and provides feedback information of the gripping force of manipulators, the control accuracy and speed are all improved.

TMS320VC5509A; EP2C8Q208; pneumatic manipulator

TP 241.3

A

1006-7167(2017)11-0077-05

2017-03-02

吉林省科技發展計劃項目(20160418024FG); 吉林省教育廳項目(吉教科合字[2015]第161號); 北華大學2016年校級教研立項課題 (XJYB2016003)

董 勝 (1972-),男,黑龍江嫩江人,碩士,副教授,研究方向:信號采集與處理。

Tel.:18604497893; E-mail: dswlpdsx@163.com