基于FPGA的千兆以太網(wǎng)接口應(yīng)用研究與實(shí)現(xiàn)

楊青山

(廣州海格通信集團(tuán)股份有限公司,廣東 廣州 510663)

千兆以太網(wǎng)具有大數(shù)據(jù)傳輸以及高速實(shí)時(shí)性的特征,因此在視頻以及音頻等領(lǐng)域具有廣闊的應(yīng)用前景。在進(jìn)行數(shù)據(jù)傳輸?shù)倪^程中越來越重視實(shí)時(shí)性問題,針對這一問題,用戶數(shù)據(jù)協(xié)議(User Data Protocol,UDP)作為一共新型數(shù)據(jù)傳輸協(xié)議被提出,具有很好的高效性以及低延遲性,這一傳輸協(xié)議的引入也很好地解決了數(shù)據(jù)實(shí)時(shí)傳輸?shù)膯栴}。目前在數(shù)據(jù)傳輸中比較常用的協(xié)議主要有兩種:TCP/1P協(xié)議和ASIC內(nèi)置協(xié)議,這兩大協(xié)議雖然比較成熟得到了發(fā)展,但是在可集成化、可移植性以及傳輸效率方面還存在極大的困難。在這樣的背景下,本文結(jié)合FPGA的優(yōu)勢,提出一種基于FPGA的UDP/IP協(xié)議,將該優(yōu)化設(shè)計(jì)應(yīng)用于千兆以太網(wǎng)的傳輸當(dāng)中,兼顧傳輸效率的同時(shí),還能夠保證數(shù)據(jù)傳輸?shù)膶?shí)時(shí)性等,隨著這一方案的優(yōu)化和完善,目前已經(jīng)在工程中得到應(yīng)用。

1 TCP/IP協(xié)議棧結(jié)構(gòu)及工作原理

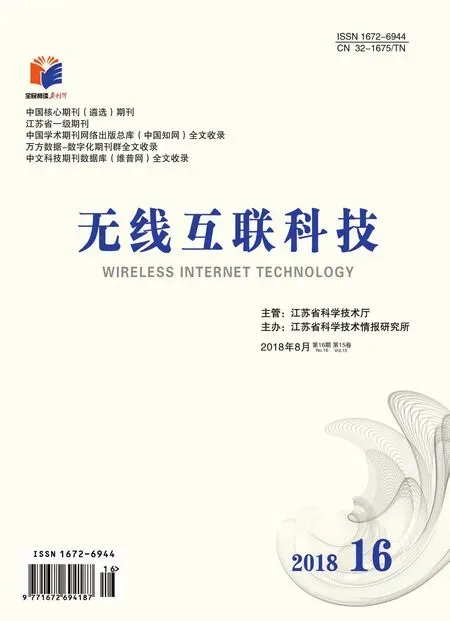

開放系統(tǒng)互聯(lián)(Open System Interconnection,OSI)參考模型作為一種比較成熟的網(wǎng)絡(luò)結(jié)構(gòu)標(biāo)準(zhǔn)模型,由國際互聯(lián)網(wǎng)標(biāo)準(zhǔn)化組織提出構(gòu)建。通過該模型的構(gòu)建與優(yōu)化能夠保證不同硬件的相互通信,但是這一模型往往比較復(fù)雜,因此在實(shí)際應(yīng)用中比較困難。為解決OSI參考模型復(fù)雜度問題,TCP/IP模型被提出并應(yīng)用,這一模型并不是簡單地將TCP和IP兩個(gè)協(xié)議進(jìn)行聯(lián)合,而是聯(lián)合Internet整個(gè)TCP/IP協(xié)議組。為進(jìn)一步確定TCP/IP的特點(diǎn)和優(yōu)越性,對TCP/IP模型與OSI模型進(jìn)行了比較,如圖1所示。

圖1 OSI與TCP/IP參考模型對照

1.1 主機(jī)到網(wǎng)絡(luò)層

在TCP/IP參考模型中沒有對這一層進(jìn)行細(xì)分,在OSI參考模型中將這一層分為物理層PHY和介質(zhì)訪間控制層MAC。這一層的主要目的是能夠?yàn)橄乱粚拥臄?shù)據(jù)傳輸提供接口,其中以太網(wǎng)就是一種重要的實(shí)現(xiàn)方式。

1.2 網(wǎng)絡(luò)互連層

對于TCP/IP協(xié)議參考模型而言,這一層是整個(gè)模型的核心,為實(shí)現(xiàn)功能進(jìn)行了細(xì)化,不僅僅定義了分組格式,而且明確了協(xié)議類型,能夠?qū)β酚伞砣冗M(jìn)行控制。

1.3 傳輸層

在傳輸層當(dāng)中為實(shí)現(xiàn)功能引入了TCP協(xié)議和UDP協(xié)議,TCP協(xié)議作為傳輸控制協(xié)議基于字節(jié)流進(jìn)行,具有極大可靠性;這一協(xié)議還是在利用IP層機(jī)制來進(jìn)一步提高連接可靠性,能夠引入窗口控制、分包控制等方法實(shí)現(xiàn)字節(jié)流的傳輸,不是一對一的傳輸,而是一對多的傳輸。

1.4 應(yīng)用層

這一層中含有大量用戶應(yīng)用協(xié)議來面向用戶。在本文的協(xié)議優(yōu)化當(dāng)中,還引入了UDP協(xié)議,主要在TCP/IP傳輸層中引入這一協(xié)議,面向報(bào)文傳送與傳輸,通過這一協(xié)議之后接收方并不會提供反饋機(jī)制,這樣導(dǎo)致其可靠性存在一定問題。UDP協(xié)議的這一特點(diǎn)也提高了其數(shù)據(jù)傳輸速率,同時(shí)和TCP協(xié)議相比實(shí)時(shí)性更強(qiáng),對于系統(tǒng)的要求和負(fù)載也相對較低。基于這些優(yōu)點(diǎn),本文在進(jìn)行優(yōu)化設(shè)計(jì)的過程中引入了UDP傳輸協(xié)議在傳輸層中進(jìn)行點(diǎn)對點(diǎn)的數(shù)據(jù)傳輸報(bào)送,同時(shí)還網(wǎng)絡(luò)層中采用最優(yōu)的IP協(xié)議,ARP協(xié)議和MAC協(xié)議主要應(yīng)用于數(shù)據(jù)鏈路層,在物理層中應(yīng)用自適應(yīng)技術(shù),應(yīng)用千兆網(wǎng)1 000 Base-T的連接通道。

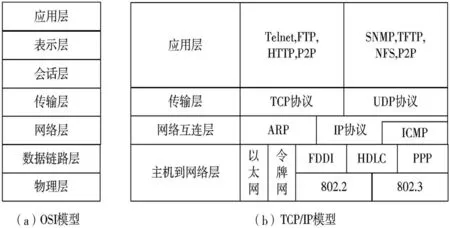

本文提出的接口優(yōu)化實(shí)際是UDP/IP協(xié)議,在這一優(yōu)化協(xié)議的實(shí)際運(yùn)行過程中包括封包和解包兩個(gè)過程,在兩個(gè)過程中分別采用不同的傳輸協(xié)議來進(jìn)行數(shù)據(jù)傳輸。進(jìn)行數(shù)據(jù)傳輸與發(fā)送的過程中首先將應(yīng)用層數(shù)據(jù)傳輸?shù)絽f(xié)議棧中,在經(jīng)過協(xié)議棧數(shù)據(jù)信息處理之后進(jìn)入網(wǎng)絡(luò)層進(jìn)行下一步處理。在每層數(shù)據(jù)傳輸?shù)倪^程中需要對數(shù)據(jù)和信號進(jìn)行首尾修飾,這一整個(gè)過程被稱作是封包過程。經(jīng)過封包處理之后能夠?qū)?shù)據(jù)傳輸給通信主機(jī)結(jié)構(gòu)從機(jī),接收到的以太網(wǎng)幀數(shù)據(jù)從物理層輸入進(jìn)行分層傳輸分析,和當(dāng)前層的協(xié)議幀首部信息進(jìn)行核對匹配,對于不匹配的幀數(shù)據(jù)進(jìn)行丟棄處理,實(shí)際這一過程就是解包的過程,整個(gè)傳輸封包和解包過程如圖2所示。

圖2 TCP/IP協(xié)議層用戶數(shù)據(jù)傳輸過程

在進(jìn)行數(shù)據(jù)傳輸?shù)倪^程中需要遵循一定的協(xié)議來進(jìn)行傳輸,本設(shè)計(jì)優(yōu)化中遵循協(xié)議透明原理進(jìn)行設(shè)計(jì),按照相應(yīng)標(biāo)準(zhǔn)來進(jìn)行數(shù)據(jù)封包和解封過程處理,完成之后傳輸?shù)较乱粚舆M(jìn)行處理。精簡后的協(xié)議棧具備以下功能:(1)實(shí)現(xiàn)基于UDP傳輸協(xié)議的數(shù)據(jù)傳輸。(2)按需求可以對目的IP地址和源IP地址進(jìn)行靈活配置,支持ARP地址解析,支持checksum幀校驗(yàn)。(3)支持?jǐn)?shù)據(jù)流控制。

2 總體設(shè)計(jì)

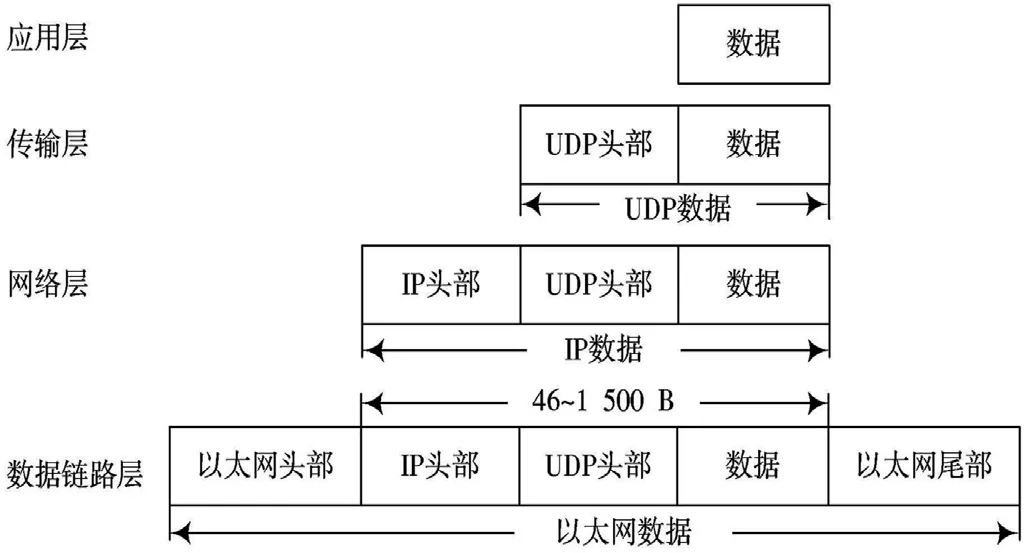

在千兆以太網(wǎng)的接口研究與發(fā)展中,也面臨一定的難題與困難,其中的典型代表就是如何實(shí)現(xiàn)以太網(wǎng)的MAC協(xié)議和以太網(wǎng)的接口功能。目前主要的以太網(wǎng)接口采用圖3所示的電路硬件結(jié)構(gòu)框圖,一般采用FPGA控制器、網(wǎng)絡(luò)處理芯片以及高性能操作系統(tǒng)處理器來進(jìn)行接口處理[1]。

圖3 以太網(wǎng)電路結(jié)構(gòu)框圖

在本總體設(shè)計(jì)中選用FPGA作為主控制器,并且在物理層中引入物理層協(xié)議芯片來實(shí)現(xiàn)其功能,在MAC層中引入MAC芯片來實(shí)現(xiàn)其功能。改設(shè)計(jì)中的硬件系統(tǒng)功能也主要在FPGA內(nèi)部以及FPGA控制器中實(shí)現(xiàn)。為進(jìn)一步簡化系統(tǒng)的硬件電路,還在FPGA中引入MAC IP核,主要應(yīng)用于MAC協(xié)議功能的實(shí)現(xiàn),可以節(jié)省MAC接口協(xié)議芯片的空間。

通過這樣的設(shè)計(jì),能夠滿足千兆以太網(wǎng)系統(tǒng)間的高速數(shù)據(jù)傳輸,而且基于這樣的設(shè)計(jì)能夠節(jié)省硬件資源與空間,在內(nèi)部即可實(shí)現(xiàn)MAC功能,這樣在節(jié)省硬件資源和空間的同時(shí)還節(jié)省了加工成本。另外充分利用FPGA的資源以及功能,能夠充分發(fā)揮硬件系統(tǒng)的作用,保證可靠性,另外由于FPGA具有很好的擴(kuò)展性,有利于后期的應(yīng)用功能擴(kuò)展。

3 硬件系統(tǒng)設(shè)計(jì)分析

在本設(shè)計(jì)的硬件系統(tǒng)設(shè)計(jì)中采用PHY芯片,并結(jié)合FPGA控制器作為核心控制來進(jìn)行千兆以太網(wǎng)的數(shù)據(jù)傳輸,綜合分析下確定采用UDP通信協(xié)議來作為整個(gè)系統(tǒng)的通信協(xié)議,另外PHY芯片能夠輔助FPGA控制器實(shí)現(xiàn)通信功能,通過這一芯片能夠?qū)崿F(xiàn)和PC機(jī)之間的數(shù)據(jù)傳輸。

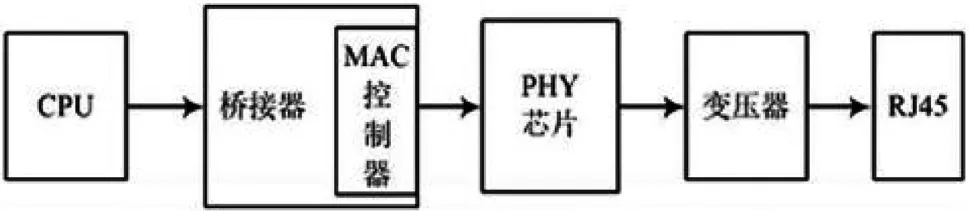

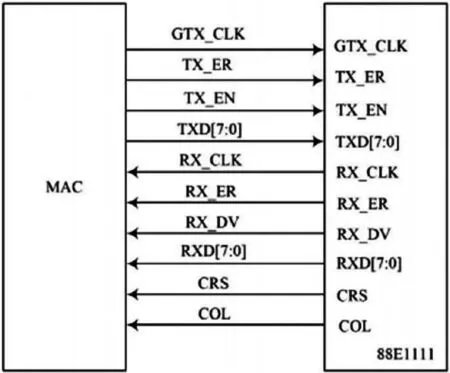

FPGA控制器作為控制核心芯片的選擇十分重要,本設(shè)計(jì)中選用Cyclone IV系列EP4CE40F23I7N芯片,另外比較重要的PHY芯片選用88E1111來進(jìn)行數(shù)據(jù)通信和傳輸,另外為完善系統(tǒng)功能需要配備相應(yīng)的各種寄存器,確定最終硬件連接關(guān)系如圖4所示。

圖4 MAC控制器與PHY芯片接口

如圖4所示,在千兆以太網(wǎng)的數(shù)據(jù)通信和傳輸過程中,綜合分析GMII模式和GMII模式兩種模式類型器,最終確定PHY芯片88E1111電路進(jìn)行數(shù)據(jù)傳輸?shù)臅r(shí)候應(yīng)該采用GMII接口的GMII接口模式,對于100 Mbps全雙工模式的數(shù)據(jù)傳輸和通信,采用PHY芯片88E1111電路中的MII接口模式中的MII接口模式進(jìn)行。

4 軟件設(shè)計(jì)

為完善本設(shè)計(jì),在硬件設(shè)計(jì)的基礎(chǔ)上需要配置相匹配的軟件系統(tǒng),本設(shè)計(jì)中基于Vcrilog HDL硬件設(shè)計(jì)語言進(jìn)行程序開發(fā)設(shè)計(jì)。

在進(jìn)行程序設(shè)計(jì)中一共包括4個(gè)模塊和部分,包括頂層模塊、UDP發(fā)送數(shù)據(jù)模塊和結(jié)構(gòu)模塊,另外在設(shè)計(jì)中還增加優(yōu)化了CRC校驗(yàn)?zāi)K。

在千兆以太網(wǎng)的數(shù)據(jù)傳輸和接口當(dāng)中,主要通過FPGA作為核心控制器進(jìn)行控制,并且能夠?qū)C機(jī)的情況進(jìn)行實(shí)時(shí)監(jiān)測在檢測基礎(chǔ)上能夠接受UDP發(fā)送的以太網(wǎng)數(shù)據(jù)包,并且通過軟件程序設(shè)計(jì)將數(shù)據(jù)包在外置SRAM存儲芯片中存儲,利用軟件程序進(jìn)行初步解析的基礎(chǔ)上,將以太網(wǎng)數(shù)據(jù)包通過網(wǎng)絡(luò)和系統(tǒng)傳遞回實(shí)驗(yàn)PC機(jī)[2]。

4.1 MAC功能配置

在設(shè)計(jì)中,必須通過一系列的配置才能使MAC軟核正常工作,在SOPC系統(tǒng)中,可以通過Avalon-MM控制接口來配置MAC軟核。對MAC控制寄存器的配置來完成控制MAC功能模塊,MAC功能模塊將在發(fā)送或接收位使用后立即開始工作。在對MAC軟核的配置中,主要涉及以下寄存器的配置:命令配置(command_ config ),MAC地址(mac_0/mac_ 1}、最大幀長(frm length、外部PHY地址Cmdio_addr0/mdio_ addrl,另外,由于本設(shè)計(jì)中的MAC軟核包含了內(nèi)部FIFO需要配置FIFO緩存器的一些閡值(almost empty,almost full,section empty,section full)。

4.2 控制軟件設(shè)計(jì)

軟件控制是整個(gè)設(shè)計(jì)正常運(yùn)行的關(guān)鍵一環(huán)。由于設(shè)計(jì)中MAC軟核、自定義模塊等均基于SOPC技術(shù)進(jìn)行設(shè)計(jì),所以NIOS軟核的正常運(yùn)行將是硬件邏輯工作的基礎(chǔ)。

在設(shè)計(jì)中,為了使以太網(wǎng)的網(wǎng)絡(luò)配置更加靈活,設(shè)計(jì)中利用Avalon-MM總線對自定義模塊中的IP地址,MAC地址以及UDP端口號等進(jìn)行配置。控制軟件的設(shè)計(jì)主要包括自定義模塊的設(shè)置、MAC軟核以及PHY芯片寄存器的配置,在上述過程完成后,觸發(fā)整個(gè)系統(tǒng)運(yùn)行。

系統(tǒng)首先初始化自定義模塊并利用MDIO接口初始化外部PHY芯片。然后進(jìn)行MAC配置寄存器的初始化,分為4個(gè)步驟:第一步,禁用MAC軟核的發(fā)送接收功能;第二步,對MAC軟核FIFO相關(guān)參數(shù)進(jìn)行配置;第三步,對MAC軟核的地址進(jìn)行配置;最后,完成MAC軟核的其他配置(最大幀長等)。接著,對PHY寄存器進(jìn)行配置,將PHY芯片配置在支持自動協(xié)商、支持全雙工、支持10 Mpbs/1 000 Mbps模式上。最后完成MAC控制寄存器配置,使能系統(tǒng)啟動標(biāo)志。

5 結(jié)語

本文主要是對當(dāng)前FPGA的特點(diǎn)以及優(yōu)勢進(jìn)行分析,設(shè)計(jì)了一種基于FPGA的千兆以太網(wǎng)接口,將FPGA控制器作為核心,來實(shí)現(xiàn)MAC層協(xié)議,F(xiàn)PGA引入不僅僅提高了方法運(yùn)用的靈活性、可靠性,而且有利于實(shí)現(xiàn)高速傳輸,具有重要意義。