應用于硅微機械諧振式傳感器的頻率計

黃榮玉,牛文舉,韓建強

(中國計量大學機電工程學院,杭州 310018)

0 引言

目前,MEMS傳感器由于其巨大的經濟效益和廣闊前景正處于快速發展時期。MEMS傳感器具有重量輕、體積小、成本和功耗低,易于集成和可以大規模批量生產等優點。廣泛應用于武器裝備、慣性導航和汽車安全等領域,是關系國家安全和經濟建設的基礎元器件之一[1]。微型傳感器按照敏感信號的測量方式不同,分為壓阻式[2],電容式[3],壓電式[4]和諧振式[5]等不同類型。在這些微傳感器中,硅微諧振式傳感器具有精度和分辨率高、功耗小、動態范圍寬以及輸出信號為數字信號的優點。硅微諧振式傳感器直接輸出頻率信號,在傳輸過程中不易產生失真誤差,可以直接和數字接口連接。由于諧振式傳感器輸出為頻率信號,這對頻率信號的測量精度提出很高的要求,而測量精度的提高依賴于頻率計性能的提高。

目前測量頻率的方法一般有周期測量法,頻率測量法和等精度測量法等[6]。周期測量法是在待測信號的一個周期內,通過測量標準信號的上升沿個數來計算出待測的頻率。這樣會引入標準信號個數的±1個字誤差[7]。同時周期測量法只適用于低頻、中頻下的測量。在高頻下,測量的誤差非常大。頻率測量法是通過在設定的閘門時間內,測量待測信號與標準信號的上升沿個數來計算出待測頻率。由于閘門時間不是待測頻率和標準信號周期的整數倍,這會引入待測信號和標準信號上升沿個數的±1個字誤差。等精度測量法[8]是先給定一個預置閘門時間,當待測信號的上升沿或者下降沿到來時,打開預置閘門開始對待測信號和標準信號同時計數。當預置閘門時間結束后,只有待測信號上升沿或下降沿到來時,才同時停止對待測信號和標準信號的計數。頻率的測量開始與停止都是在待測信號的上升沿或者下降沿完成,消除了待測頻率計數的±1個字的誤差,只有標準信號的±1個字的誤差。但是等精度法只適用于測量高頻,若要測量低頻,預置閘門時間需要設置很長的時間。例如要測1 Hz的頻率,預置閘門時間至少要設置1 s,這樣增大了測頻響應時間,大大降低了測頻的效率。

由于周期測量只測量待測信號的一個周期或多個周期,但是測的周期個數是一個定值,不隨待測信號的頻率變化而變化。因此隨著待測頻率的升高,測量精度下降,所以限制了測量頻率的范圍。針對這一弊端,設計了一種基于FPGA的測頻周期自調整頻率計。

本文設計的頻率計先在一個待測信號周期內,對標準信號的上升沿進行計數,粗略計算出待測信號頻率和周期。然后對待測信號的周期進行調整,對標準信號的上升沿重新計數,精確測量出待測信號的頻率。該頻率計不僅提高了測量頻率的精度,而且體積小,價格便宜,具有非常好的應用前景。

1 系統結構和原理

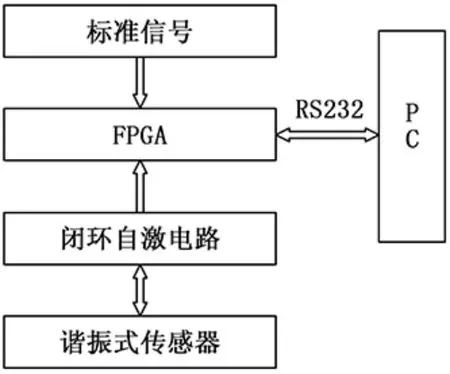

測試系統由諧振式傳感器、閉環自激測量電路、FPGA采集模塊以及PC上位機四部分組成,系統組成框圖如圖1所示。

圖1 頻率計結構框圖

諧振式傳感器使用微橋諧振器作為敏感元件。采用電熱激勵,壓阻檢測的激勵檢測方式。即給在位于諧振梁中間位置的激勵電阻上加熱,通過局部加熱使諧振梁的結構產生形變,引起諧振梁的振動。當諧振梁振動后,位于諧振梁根部的惠斯通電橋上的電阻會因為振動產生形變,從而導致阻值發生改變,通過檢測壓敏電阻的阻值變化來檢測振動。

測試過程中,先使用閉環自激電路[9]讓諧振器處于閉環自激狀態,閉環自激電路的輸出信號為頻率信號。利用FPGA對輸出頻率信號進行測量和采集,最后將測量的頻率信號經過RS-232串行通信接口送入PC上位機。上位機使用Visual C#進行操作界面的軟件設計,實現頻率數值的實時顯示和儲存。

本文設計的頻率計測量范圍為1 Hz~2 MHz。由于頻率計測量頻率的精度直接決定諧振式傳感器的測量精度,該頻率計全量程內測量精度可以達到10-7數量級,相比于六位半萬用表等傳統測頻工具,測頻精度有了明顯的提升。

2 系統硬件設計

2.1 FPGA開發板

FPGA(現場可編程門陣列)的開發區別于單片機,它是通過硬件語言來描述的,并且以并行運算為主。FPGA是在CPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路 (ASIC)領域中一種半定制電路出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。它是當今數字系統設計的主要硬件平臺。本文設計的頻率計采用的FPGA控制模塊是型號為AX301的黑金開發板平臺。此款開發板搭載的主芯片是ALERA公司的CYCLONE IV系列型號為EP4CE6F17C8的FPGA主芯片。AX301開發板通過USB供電,用MINI USB線將開發板跟電腦的USB連接,按鍵電源開關,可以給開發板供電。其數字工作電壓為3.3 V和1.2 V,板載晶振為50 MHz,晶振輸出連接到FPGA的全局輸入時鐘管腳 (CLK1管腳E1),這個CLK1可以用來驅動 FPGA內的用戶邏輯電路,用戶可以通過配置FPGA內部的鎖相環來分頻或倍頻實現其他頻率的時鐘,從而提高工作速度。

2.2 RS-232串行通信

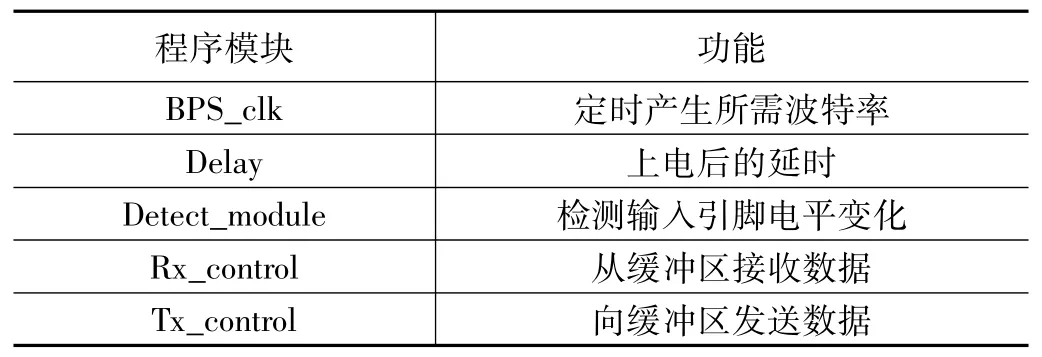

RS-232是現在主流的串行通信接口之一,它被定義為一種在低速率串行通信中增加通信距離的單端標準。當它傳送數據時,只需要一條傳輸線就能正確的將數據順利傳送到對方,因此叫做異步傳輸。由于RS-232是一種串行通信,故需要在軟件中設置包括波特率、奇偶校驗和停止位等多項設置。本設計波特率為128000、奇偶校驗位為NONE和停止位為1。采用FPGA與PC機通信的主要程序模塊如表1所示。

表1 FPGA與PC機通信的主要程序模塊

向緩沖區發送數據通過與RS232接口相連,將從閉環自激電路中輸出的頻率信號數據傳輸到PC上位機,并實時顯示出來。

3 系統軟件設計

3.1 軟件設計思路和編程方法

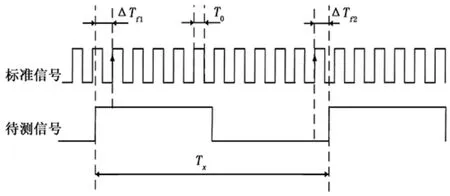

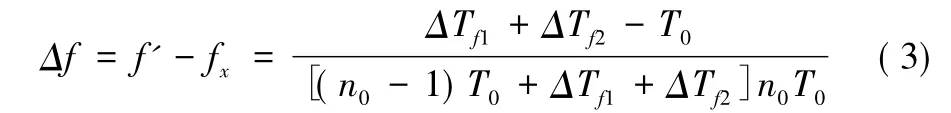

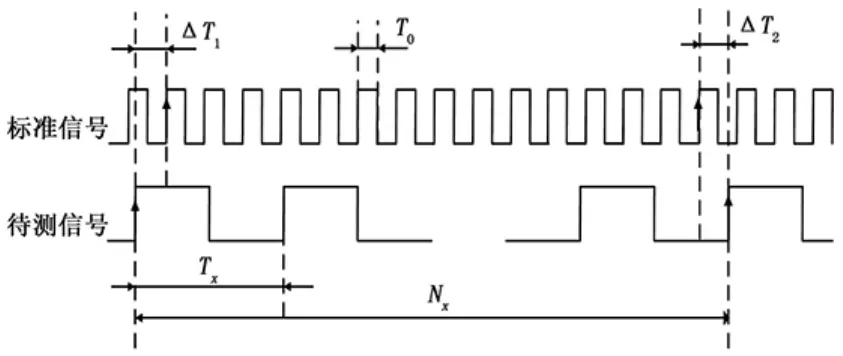

先用標準信號對待測信號的一個周期進行計數,預估算出待測頻率大小,原理如圖2所示。

圖2 周期測頻原理圖

假設標準信號的周期為T0,在待測信號的一個周期內,標準信號的上升沿個數為n0,待測信號的周期為Tx,因此待測頻率fx為:

其中,ΔTf1和ΔTf2為測量時的誤差。調整后的待測信號頻率f'為:

頻率的誤差為:

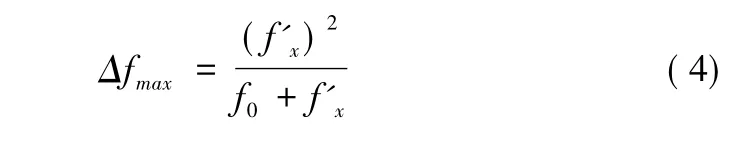

由 (3)式可得調整后的預估算頻率的最大誤差和最小誤差分別為:

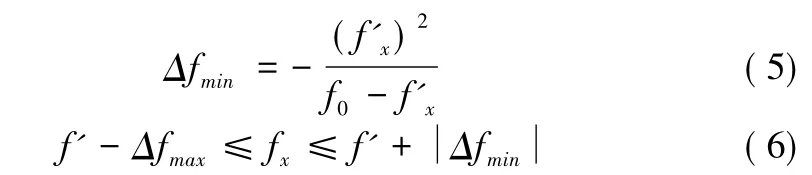

預估算待測頻率的大小后,程序開始進行對待測信號的頻率精確的測量,其測量頻率時序圖如圖3所示。

圖3 精確測量頻率時序圖

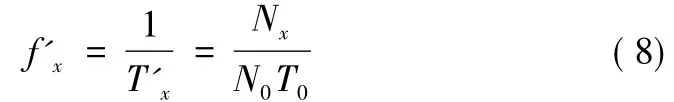

Nx是調整后需要測量的待測信號的上升沿個數,標準信號的上升沿的個數設為N0。

待測信號的真值為:

其中,ΔT=ΔT1+ΔT2調整后的待測信號的頻率f'x為:

待測信號的頻率的相對誤差為:

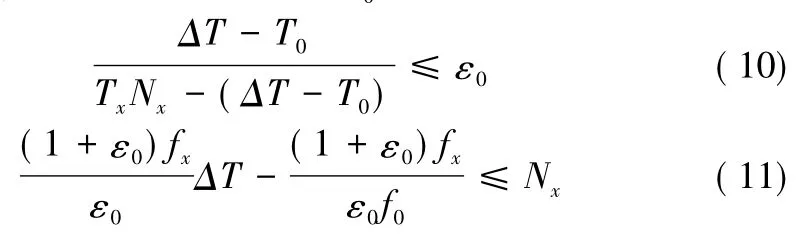

設頻率計測量的相對誤差為ε0

由 (11)可知,Nx隨ΔT的增大而增大,ΔT最大值為2T0。因此可得出調整后需要測量的待測信號的上升沿個數Nx,待測頻率的真值fx、頻率f0和在待測信號一個周期內標準信號的上升沿個數n0的關系,如式 (12)所示:

3.2 軟件實現流程圖

FPGA程序使用verilog語言進行編寫,使用quartusⅡ軟件進行編譯。Quartus II是 Altera公司的綜合性 PLD/FPGA開發軟件,支持原理圖、VHDL、VerilogHDL以及AHDL(Altera Hardware Descrip-tion Language)等多種設計輸入形式,內嵌自有的綜合器以及仿真器,可以完成從設計輸入到硬件配置的完整PLD設計流程。

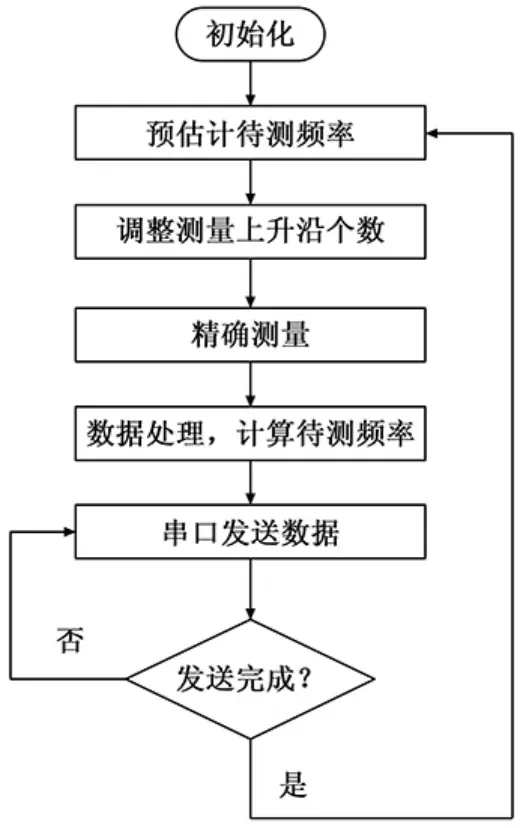

程序的流程圖如圖4所示。軟件程序主要由四大模塊組成,分別為預估算待測信號模塊,自調整待測信號周期模塊,精測量頻率模塊,數據處理和串口數據輸出模塊。首先是對程序進行初始化。然后預估算待測信號模塊初步測量待測信號的頻率和周期,在待測信號一個周期內,對標準信號的上升沿進行粗略地計數。所測出的上升沿個數n0再傳輸到自調整模塊中。自調整模塊根據n0的大小,計算出需要測量的待測信號周期個數Nx。然后再把Nx傳遞到精測量模塊。在待測信號的Nx個周期內,精測量模塊對標準信號的N0上升沿進行計數,計數結束之后。再把標準上升沿個數N0傳遞到數據處理模塊,通過對Nx和N0兩個數據進行處理,計算出待測的頻率。然后將待測的頻率傳遞到串口數據輸出模塊將頻率傳輸到上位機并顯示和儲存待測信號的頻率。發送結束后,程序再次對待測信號進行預估算,進入下一次的頻率測量。

圖4 FPGA測頻程序流程圖

3.3 PC上位機設計

為了實時的顯示出采集的頻率,FPGA將計算的頻率數據傳輸到上位機,通過上位機對接收的頻率進行處理后實時的顯示出來。該設計的上位機采用Microsoft公司的Visual C#開發平臺進行開發。設計的頻率系統操作界面如圖5所示。該上位機操作簡單界面簡潔,不僅能將采集的頻率實時顯示出來,也能將采集的頻率進行緩存或者保存為TXT文檔進行后期查看等操作。

圖5 頻率顯示窗口

4 實驗結果與分析

4.1 測量方波信號

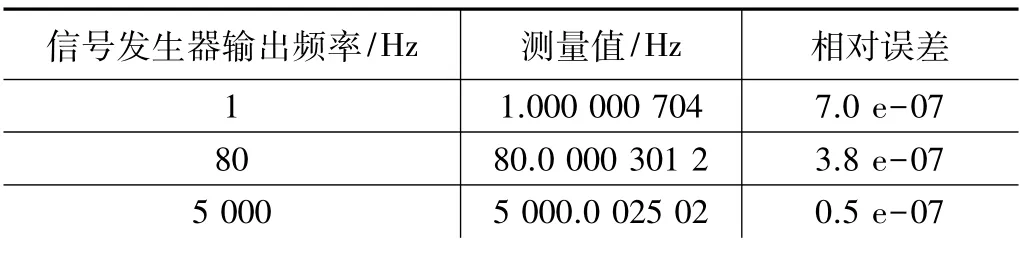

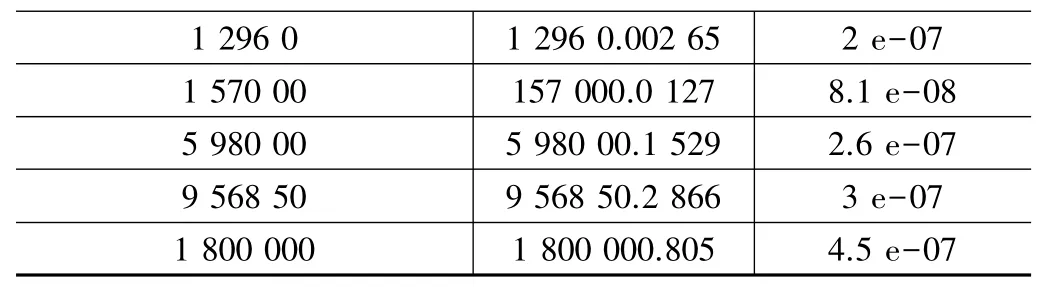

為了測試本文設計的頻率計精度,使用頻率計對安捷倫33521A信號發生器發出的不同頻率的方波信號進行測量,測量結果如表2所示。通過測量結果可以看出:本文設計的自調整頻率計精度在全量程范圍內達到精度要求,采用該頻率計測量1 Hz~2 MHz方波信號的頻率的相對誤差的數量級可以達到10-7。

表2 方波信號測試結果

__________1 296 0 1 296 0.002 65 2 e-07_________1 570 00 157 000.0 127 8.1 e-08_________5 980 00 5 980 00.1 529 2.6 e-07_________9 568 50 9 568 50.2 866 3 e-07_________1 800 000 1 800 000.805 4.5 e-07

4.2 測量諧振式加速度傳感器的輸出信號

將設計的頻率計應用到實驗室研制的諧振式加速度傳感器測試過程中。該加速度傳感器設計用來檢測面內加速度。由諧振梁、蟹腿型支撐梁、質量塊、激勵電阻、惠斯登電橋和金屬引線組成。在X方向加速度作用下,質量塊在X方向運動。X方向的其中一個諧振梁所受的軸向應力發生改變,諧振頻率發生變化,該諧振頻率變化的差值反映了X方向加速度的大小和方向;同樣地,在Y方向加速度作用下,質量塊在Y方向運動,Y方向的諧振梁之一軸向應力發生改變,諧振頻率變化。該諧振梁諧振頻率變化的差值反映Y方向加速度的大小和方向。

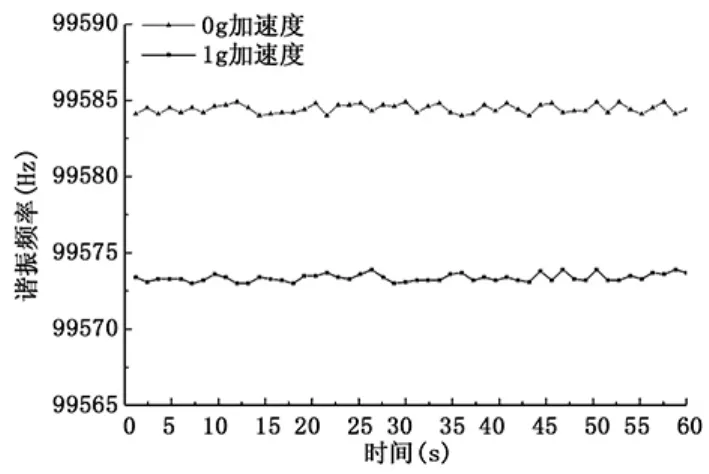

由于重力加速度精確度高,同時很容易獲得,便于應用到實驗中。因此實驗室采用重力場翻滾試驗來對制作出的加速度計樣片進行測試[10]。實驗使用裝置為精密型手動角度旋轉臺。測試時,將加速度計樣片置于角度旋轉工作臺上,使用閉環自激電路讓測試的諧振梁處于閉環自激狀態,通過旋轉精密型角度旋轉臺來調節被測諧振梁與重力加速度之間的夾角,從而來給樣片提供不同大小的加速度。諧振梁的諧振頻率隨著不同的加速度變化而變化,以此來測試該加速度計樣片的性能。在0 g和1 g X方向加速度下,使用安捷倫六位半萬用表34401采集1分鐘X方向諧振梁的輸出諧振頻率如圖6所示,本文設計的頻率計采集1分鐘X方向諧振梁的輸出諧振頻率如圖7所示。

圖6 安捷倫萬用表采集的輸出頻率

圖7 本文設計的頻率計采集的輸出頻率

分析兩組數據可以得到:對于使用安捷倫六位半萬用表采集的數據,當加速度計受到1 g加速度時,諧振頻率的平均值下降約為11.07 Hz。對于本文設計的頻率采集的數據,當加速度計受到1 g加速度時,諧振頻率的平均值下降約為11.12 Hz。比較兩者發現:與安捷倫萬用表相比,本文設計的頻率計在1分鐘內采樣數據個數約是安捷倫萬用表采樣數據個數的10倍,更加全面的反映出不同時間諧振梁的振動狀態。兩者在1分鐘內采集的諧振頻率的平均值存在一定的誤差,這是因為本文設計的頻率計采集的點更加全面。同時,該頻率計具有體積小,成本低等不可忽視的優勢,擁有廣闊的市場前景。后續工作可以圍繞進一步提高采集速度、減噪進行,從而提高系統穩定性。

5 結束語

該頻率計是基于FPGA設計的,使用quartus編譯后,寫入到FPGA芯片中。通過對信號發生器產生的標準頻率信號進行測量,結果證明,采用該頻率計測量1 Hz~2 MHz標準信號的頻率的相對誤差數量級可以達到10-7,達到設計要求。將其應用到硅微諧振式加速度傳感器的性能測試中,測得諧振式加速度傳感器在閉環時輸出頻率的變化穩定在1 Hz以內,同時測試了加速度計的靈敏度為11.12 Hz/g。由于FPGA體積小,結構簡單、靈活性高、可編程,造價較低,因此被廣泛應用在數據采集等方面。本文設計的頻率計其測量精度與響應時間成正比,在一些測量精度要求不高的工作中可適當降低精度提高測量的響應速度。