一種適用于移動芯片的低功耗低溫漂LDO電路

陳迪平,應 韜,董 剛

(湖南大學 物理與微電子科學學院, 湖南 長沙 410082)

高效的電源管理在有限能耗的移動設備中越來越重要[1].低壓差線性穩壓器(Low DropOut regulator, LDO)因響應速度快、噪聲低、電路結構簡單及外圍器件少等特點,逐漸被集成于片上系統中[2-5].針對不同電壓需求的各噪聲敏感模塊,分別被優化設計提供純凈的電源,可改善系統的整體性能.為了降低移動設備在睡眠等工作模式下的功耗,延長待機時間,需降低空載時靜態電流以改善其電流效率[6].低壓差線性穩壓器輸出電壓的穩定度受多種因素疊加影響,其中工作溫度的變化對誤差放大器輸出電壓穩定度和基準電壓的影響最大[7-8].

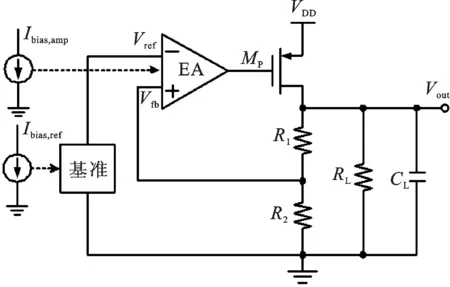

圖1 傳統低壓差線性穩壓器電路結構

基于傳統低壓差線性穩壓器電路,筆者提出了一種適用于移動設備芯片的新型低壓差線性穩壓器電路.將傳統低壓差線性穩壓器反饋網絡中的一個反饋電阻替換成經過一階溫度補償的恒流源,同時將其作為基準電壓源電路和誤差放大器的偏置參考電流,從而減少了額外的電流支路,降低了該低壓差線性穩壓器電路的靜態功耗.該低壓差線性穩壓器電路輸出電壓采用一階溫度補償措施,降低了其輸出電壓對溫度的敏感性,實現了低溫漂系數設計.

1 傳統低壓差線性穩壓器電路分析

傳統低壓差線性穩壓器的電路結構如圖1所示,主要包括誤差放大器、調整管、反饋電阻網絡和基準電壓源4個部分[9].低壓差線性穩壓器是一個閉環電壓負反饋系統,通過反饋作用將輸出電壓穩定.正常工作時輸出電壓為

Vout=Vref(1+R1/R2) .

(1)

Vout=(Vref+Vos) (1+R1/R2) .

(2)

若R1、R2使用相同類型的電阻,則它們的溫度特性相同,比值為與溫度無關的常數.據式(2)可得輸出電壓溫度系數TC為

(3)

根據式(3),Vref和Vos的溫度特性直接被放大為Vout的溫度特性.此外,傳統低壓差線性穩壓器結構輸出電壓Vout受多種因素影響,包括輸入電源電壓對其影響(ΔVLR),負載對其影響(ΔVLDR),基準電壓對其影響(ΔVo,ref),誤差放大器對其影響(ΔVo,a),反饋電阻對其影響(ΔVo,r)和溫度系數對其影響(ΔVTC)等.其中,ΔVo,ref和ΔVo,a對Vout的影響最大.低壓差線性穩壓器的輸出精度為[7]

% .

(4)

圖2 新型低壓差線性穩壓器電路結構

2 新型低壓差線性穩壓器電路設計

2.1 低功耗優化設計

筆者設計的新型低壓差線性穩壓器的電路結構如圖2所示.采用恒流源IL代替傳統低壓差線性穩壓器電路中的反饋電阻R2,同時將該電流映射到誤差放大器和基準電壓源電路,作為其偏置參考電流,減少額外電流支路,以達到降低靜態功耗、提高電流效率的目的.

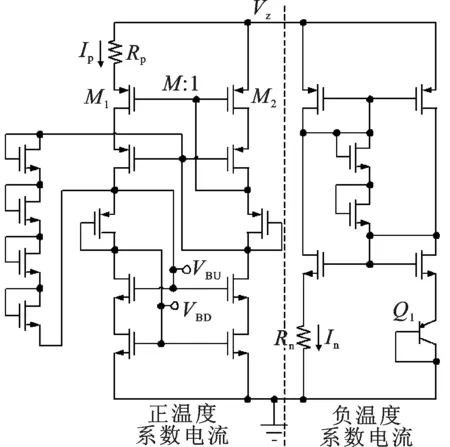

圖3 恒流源IL電路

基于上述結構設計,恒流源IL(圖3所示)采用溫度補償結構予以實現: 由正溫度系數電流(Proportional To Absolute Temperature, PTAT)和負溫度系數電流(Negative To Absolute Temperature, NTAT)兩部分構成.M1和M2管工作于弱反型區,弱反型區金屬氧化物半導體(Metal Oxide Semiconductor,MOS)管電流為[11]

(5)

其中,參數n定義為(1+Cdep/Cox),Cox為柵氧層單位電容,Cdep為溝道耗盡層單位電容,n值在1.2~1.5之間,取決于溝道耗盡層的厚度,且與偏置電壓相關.M1和M2的寬長比為M,其余對管寬長比均相同,因此,流過電阻Rp的電流Ip為

據式(6),電流Ip大小只與參數n、電阻Rp、溫度電壓VT以及兩管比例M相關,而與電壓無關.在正溫度系數電流電路中引出電壓端VBU和VBD,將電流Ip映射到誤差放大器和基準電壓源電路中分別作為其偏置參考電流.電流Ip為基準電壓源電路所需的正溫度系數電流,在電路實現中合理設計環路相位裕度和帶寬等參數,并留有一定的設計裕度,則復用偏置電流不會對誤差放大器偏置電路產生負面影響.

負溫度系數電流基于二極管方式連接的PNP管Q1產生,如圖3所示,流過電阻Rn的電流In約為

(7)

據式(7),電流In的大小與電壓無關,電阻Rn決定了電流In的大小.

根據式(6)和式(7),將兩部分電流相加可得到電流IL:

(8)

因此,該新型低壓差線性穩壓器的輸出電壓為

(9)

2.2 低溫漂系數設計

考慮誤差放大器失調電壓Vos后的低壓差線性穩壓器輸出電壓為

(10)

由式(10),可得低壓差線性穩壓器輸出電壓溫度系數為

(11)

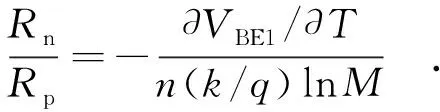

式(10)中第3項為正值,第4項為負值,可通過相關參數的合理設計使這兩項互相抵消,則與式(3)相比,低壓差線性穩壓器輸出電壓的溫度系數將有效減小.因此,令上式后兩項之和為零,可得

(12)

(13)

圖4 筆者設計的低壓差線性穩壓器整體電路圖

通過仿真掃描可得到?VBE1/?T的值.根據式(13)設計電阻比值,可實現溫度補償.與傳統低壓差線性穩壓器相比,筆者所設計的新型低壓差線性穩壓器電路在滿足式(13)的條件下,可有效地降低輸出電壓的溫度敏感性,提高輸出的穩定度.

2.3 整體電路設計

筆者設計的新型低壓差線性穩壓器整體電路如圖4所示,M3~M9、Rv和Q2構成帶隙電壓基準.在實現中,從正溫度系數電流部分N倍比例映射正溫度系數電流,與Q2產生的負溫度系數電流進行溫度補償,溫度補償后的電流在電阻Rv上生成基準電壓Vref[12]:

(14)

選擇合適的N、n、M和電阻比值,可獲得接近零溫度系數的Vref.

針對不同的負載電容,低壓差線性穩壓器環路頻率補償方式是不盡相同的.對于筆者的設計,因無片外大電容負載,為避免環路主極點隨負載電容的變化而變化,采用密勒補償方式實現電路的穩定性設計.將低頻主極點放在誤差放大器輸出端,使低壓差線性穩壓器輸出節點產生的極點成為次極點,以降低負載變化對環路穩定性的影響.

在實現中,增加誤差放大器增益可減小負載調整率,但此舉會影響閉環穩定性,需折中考慮.傳統結構中誤差放大器和基準電壓源電路有限的電源抑制比會限制低壓差線性穩壓器電路低頻處的電源抑制比,調整管有限的阻抗也會限制低壓差線性穩壓器的電源抑制比,而提高誤差放大器增益和環路帶寬可以有效地改善電源的抑制比.

筆者的設計為移動設備芯片提供電源管理,輸出精度及負載能力要求不高,故采用M10~M15構成的單級誤差放大器,尾電流源為共源共柵結構,直接從正溫度系數電流部分比例映射獲取.此舉可簡化頻率補償方案,降低電路成本.仿真分析表明,此設計可滿足實際應用場合的要求.

根據功耗和面積限定,由式(6)設定電流Ip為400 nA,n取1.45,M取8,則

Rp=n(kT/q) lnM/Ip≈196 kΩ .

(15)

Q1和Q2采用不同尺寸的晶體管予以實現.對溫度仿真掃描,可得 ?VBE1/ ?T約為 -2.8 mV/℃,?VBE2/ ?T約為 -1.6 mV/℃,由式(12)得Rn≈ 2.1 MΩ; 折中考慮功耗和電阻Rv的大小,式(14)中N取4,將其對溫度求導并令其為0,可得Rv≈ 300 kΩ.再根據具體仿真情況適當調整電阻值.在實際電路實現時,電阻Rn、Rp、R1和Rv均加入可控電阻陣列以便于修調.

圖5 筆者設計的低壓差線性穩壓器電路版圖設計

3 電路版圖設計及仿真結果分析

基于上海宏力半導體有限公司(Grace Semiconductor Manufacturing Corporation,GSMC) 0.18 μm 互補金屬氧化物半導體(Complementary Metal-Oxide-Semiconductor,CMOS)工藝,并利用Cadence軟件完成了電路和版圖設計,利用Spectre、Virtuoso等工具進行了仿真分析.圖5中的黑色虛線區域所示為該低壓差線性穩壓器的電路版圖設計,其面積為 0.12 mm× 0.09 mm.

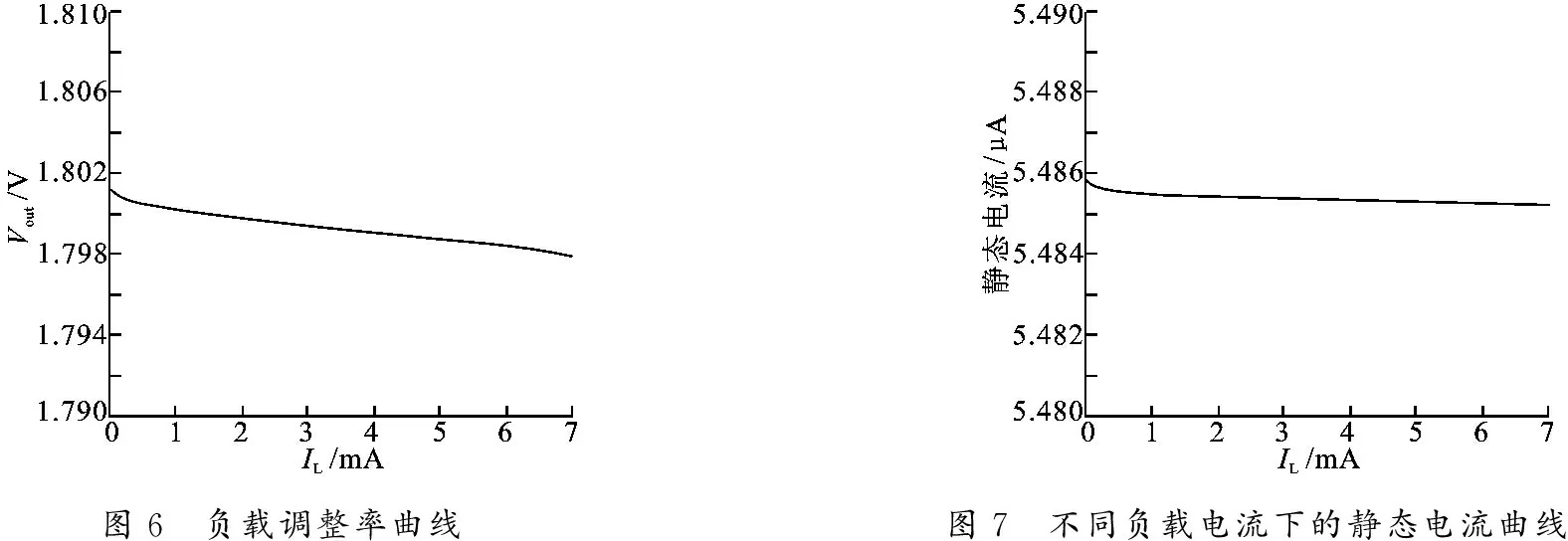

該電路用于芯片內部模塊的供電,其輸入電源電壓為 3.3 V,輸出電壓為 1.8 V.因負載驅動要求不高,故P溝道金屬氧化物半導體(P-channel Metal Oxide Semiconductor,PMOS)調整管尺寸較小,最大負載電流為 7 mA,滿足負載要求.如圖6所示,其負載調整率為 0.51 mV/ mA,滿足應用要求;在 2.85 ~ 4.00 V 的輸入電壓范圍內,其線性調整率約 1.437 mV/V; 輸出電壓精度約為0.25%.如圖7所示,負載電流在 0~7 mA 的范圍內,該低壓差線性穩壓器電路包括基準電壓源在內的總靜態電流基本保持不變,約 5.486 μA.

圖8 Vout和Vref的溫度敏感性曲線

如圖8所示,在TT工藝角下,對該低壓差線性穩壓器輸出電壓Vout和基準電壓Vref進行DC溫度掃描,掃描范圍為 -40~ 85℃,輸出電壓與基準電壓隨溫度的變化趨勢基本保持一致,其溫漂系數僅為 9.772× 10-6/℃,滿足設計要求.

在無片外電容的情況下,當負載電流為10 μA、100 μA和1 mA時,相裕度依次為66.0°、76.5°和87.5°; 在最大負載電流情況下,電源抑制比約為 -49.7 (100 kHz 條件下).

此新型低壓差線性穩壓器電路在不同設計要求下可達到不同性能,取決于面積、功耗和負載驅動能力等指標的折中.如采用高阻值電阻,可降低功耗; 使用大尺寸調整管,可增強負載能力; 采用經更高階溫度補償的恒流源,則溫漂更小.所設計的低壓差線性穩壓器電路應用于一款移動設備芯片,其電源供電電壓要求為 3.1~ 3.5 V,低壓差線性穩壓器工作電壓范圍將其完全覆蓋.筆者設計的新型低壓差線性穩壓器電路的部分性能指標與已發表文獻所提結構的對比分析如表1所示,據此可以看出,在相近工藝和面積條件約束下,筆者設計的新型低壓差線性穩壓器電路對于空載時靜態電流這一指標具有較大改進,約為文獻[1]中低壓差線性穩壓器靜態電流的 1/10,較另外幾篇文獻也具備明顯的優勢.該新型低壓差線性穩壓器電路靜態電流包括基準電壓源電路電流在內,而其他幾種設計并不包括.同時,文獻[7]中低壓差線性穩壓器輸出電壓的溫漂系數為 2.260× 10-5/℃,文獻[9] 中低壓差線性穩壓器溫漂系數低于 4.500× 10-5/℃,而筆者設計的低壓差線性穩壓器溫漂系數為 9.772× 10-6/℃,相比之下具有較大優勢.綜合衡量,筆者設計的低壓差線性穩壓器電路在降低功耗的條件下仍具有良好的整體性能,滿足設計要求.

表1 本設計與參考文獻部分性能指標對比

4 總 結

基于傳統低壓差線性穩壓器結構,筆者采取復用偏置電流、引入經溫度補償的恒流源等措施,設計了一種適用于片內集成的新型無片外電容低壓差線性穩壓器電路,有效地降低了電路功耗,減小了輸出電壓的溫度系數,提高了輸出電壓的穩定度.仿真基于GSMC 0.18 μm CMOS工藝,驗證了電路結構的正確性和有效性,結果表明該低壓差線性穩壓器電路在 2.85~ 4.00 V 工作電壓范圍內,空載時包括基準電壓源電路在內的總靜態電流僅為 5.486 μA,在 -40~ 85℃工作溫度范圍內,輸出電壓溫漂僅為 9.772× 10-6/℃,達到了低功耗和低溫漂的要求.