基于FPGA的高速數據采集系統的設計分析

吳明陽 上海柏飛電子科技有限公司

前言:數據采集在諸多領域得到了廣泛應用。當前,高速數據采集對相應的系統設計提出了較高要求。基于FPGA的高速數據采集系統,對Verilog HDL語言進行采用,并借助QuartusII6.0軟件編程對IP核進行控制,對多個ADC08B200芯片實施有效的數據采集,并借助DDRII SDRAM實施數據緩存,通過PCI總線將數據傳輸到PC機。利用PC機相應的測試軟件,能有效實現對高速數據的良好采集。

1 現場可編程門陣列(FPGA)技術分析

FPGA,即現場可編程門陣列,是各類可編程器件,諸如PAL、CPLD以及GAL的發展產物。FPGA是專用集成電路相關領域的半定制電路,既能彌補定制電路的缺陷,又能克服固有可編程器件門電路數有效的不足。

FPGA結構主要由以下部分組成:一,邏輯陣列塊LAB或者CLB,兩者構成了PLD器件的邏輯組成核心;二,輸入/輸出快;三,對邏輯塊進行連接的可編程連線陣列PIA或者互連資源IR,由長度各異的連線線段組成,也有部分可編程的連接開關,用于邏輯塊之間、邏輯塊與輸入/輸出塊間的連接。FPGA具有如下優點:一,具有較大規模,能實現任何數字邏輯的相關功能,能實現系統集成;二,在投片前對設計正確性進行驗證,具有較低的開發成本;三,對設計進行修改,無需對硬件電路進行改動,且具有較短的開發周期;四,減少PCB面積,能提高系統可靠性。

FPGA的制造工藝主要是查找表技術和SRAM工藝,可實現時序邏輯電路功能。FPGA技術通常采用“自頂向下”以及“自下而上”的設計方法。當前,大規模的FPGA設計通常對“自頂向下”的設計方法進行采用。所謂“自頂向下”,是指對完全獨立于相關芯片產商以及具體產品結構的相應描述語言進行采用,在功能級定義設計產品,并與功能仿真技術相結合,有效保障設計正確性。在完成功能定義后,借助邏輯綜合技術,對功能描述進行轉換,使之轉換為某具體結構芯片相應的網表文件,將向廠商提供的布局布線器輸出后實施布局布線,其結果可實現對同一仿真器的反標回,實施涵蓋功能與時序的后驗證,確保布局布線所導致的門延時以及線延時不會對設計性能造成影響。

傳統數據采集系統對高速數據采集的相關應用缺乏適應性。基于FPGA的高速數據采集系統設計則能大幅度提高采集速度和效率,且不易受干擾。FPGA技術具有較高的時鐘頻率和較小的內部延時,且具有較快的速度和較高的效率。FPGA技術能對電路板設計實際體積有效減少,還能促進系統采集及處理信號的能力實現大幅度提高,還能實現系統編程,能有效增強產品開發、產品維護以及產品更新的便捷性。

2 基于FPGA的高速數據采集系統設計需求

(1)總體方案與系統架構

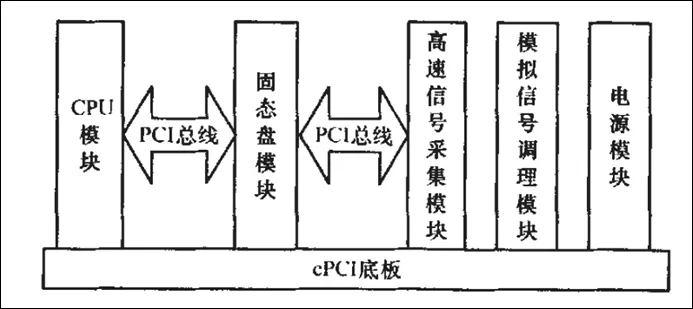

嵌入式高速數據采集系統,以緊湊型外部設備互聯標準為基礎,主要涵蓋高速數據采集、寬帶模擬信號調理、嵌入式處理器、存儲以及電源等模塊。高速數據采集技術的相關研究主要涉及如下關鍵軟件技術和硬件技術:數模混合電路設計、高速信號完整性、高速數據存儲于處理、高速并行同步數據流時序以及波形顯示與控制等[4]。基于計算機平臺相應的應用背景,設計以cPCI嵌入式計算平臺為基礎的總體方案,如下圖1所示:

圖1 基于cPCI標準的高速數據采集平臺

總體方案包括硬件及軟件相應的系統方案。硬件系統主要由cPCI底板,以x86架構為基礎的CPU模塊、兼容cPCI標準的固態盤、高速數據采集、模擬信號調理、電源等模塊構成。其中,CPU模塊是系統相應的主控、硬盤模塊與高速數據采集模塊間借助PCI總線實現數據傳輸;軟件系統涵蓋高速數據采集模塊相應的驅動程序、波形顯示與控制相應的人機界面軟件。

(2)高速數據采集系統數據流

系統數據流如下:模擬信號實現對模擬信號調理電路的進入,實現對模擬信號的放大、濾波等預處理,模擬信號經過處理后,對高速數據采集模塊進行進入,實現對高速數字信號的轉換,以代表相應的模擬信號樣點;高速數字信號對FPGA進行進入,實時樣點數據處理,樣點數據經過處理后,通過CPU以及DMA引擎借助PCI總線有效讀入內存,實現存儲、顯示等各類后端處理。

3 基于FPGA的高速數據采集系統功能設計

(1)數據采集相應的硬件模塊設計

基于FPGA的高速數據采集平臺,其硬件系統主要包括cPCI底板、固態盤模塊、以cPCI標準為基礎的CPU模塊、高速數據采集相應模塊、電源模塊以及模擬信號調理相應模塊等。在機箱、模塊結構,總線接口,電源以及系統管理等與cPCI標準完全兼容,呈現出模塊化、可擴展性、高可靠性以及堅固性等特點。高速數據采集模塊相應的硬件構架包括高速A/D轉換器、高速局部總線-PCI橋以及大規模FPGA,如下圖2所示。采集模塊借助標準cPCI總線連接數字采集系統相應的CPU模塊,借助兩路模擬信號相應的通道接口和控制總線連接前端模擬信號調理這一模塊。

圖2 高速數據采集模塊示意圖

模擬信號調理這一模塊實現了對多路增益可編程相應的模擬信號調理通道以及一路控制總線通道的有效集成。CPU模塊借助cPCI總線向高速數據采集模塊發送控制命令,采集模塊對控制命令進行解析并借助控制總線將命令對前端模擬信號調理模塊進行轉發,實現數據采集系統相應的主機控制并校準模擬前端相關電路參數的目的。借助主機實現對前端模擬信號調理模塊的有效動態配置,能促進模擬信號實際動態范圍的提高,還能增強模擬調理各項電路參數,諸如直流偏置、帶寬以及增益進行校準的便捷性。

數據采集系統包括2個通道,各通道相應的模擬信號由前端調理后,借助高速A/D遵循1GS/s的時鐘頻率,實施采樣。采樣過程如下:首先,將模擬信號轉換為8bit高速數字信號,其頻率為1GHz,在高速A/D轉換器內部,該信號被兩分頻成頻率為500MHz的16路高速同步并行數據流,實現對FPGA的進入。在FPGA內部,數據流進一步被串行轉并行處理以及排序,其后在FPGA內部相應的先入先出(即FIFO)中緩存。FIFO控制器連接局部總線-PCI橋,由其向cPCI總線傳送FIFO中存在的波形數據樣點。

(2)FPGA邏輯設計

可編程器件FPGA相應的速度以及集成度逐步提高,其設計手段日趨完善和靈活。FPGA編程具有較強的靈活性,得到了廣泛使用。本文選用StratixⅡ系列器件作為設計FPGA,該器件對ALM(即自適應邏輯)模塊進行了引入,性能以及邏輯封裝更高,邏輯以及布線級數更少,DSP支持更強。

本文設計FPGA采用主動串行與JTAG相結合的配置方式,可將FPGA芯片相應的MSEL0、MSEL1、MSEL2、MSEL3引腳驅動作為高、低電平選擇相應的配置方式。FPGA主要將具體設計方案作為依據確定內部功能,該硬件平臺在設計上對系統相應的可擴展性進行了充分考慮,在器件選擇方面評估系統資源,就功能設計而言,具有較多的可選性和較強的通用性,基本能良好實現一般數字信號相應的預處理功能。

(3)寬帶模擬信號調理電路設計

在高速信號采集系統中,模擬信號調理電路是其模擬前端,其具備的寬帶性能對于高速信號采集系統的整體采集能力以及可測量信號頻率的實際范圍具有直接影響。為實現對該技術的有效突破,對寬帶模擬信號相應的放大電路方案、模擬信號接地、濾波、隔離以及屏蔽方案、PCB布局布線方案、阻抗匹配方案以及阻抗變換方案實施科學設計和有效調試實現-3db寬帶200MHz以及5倍放大倍數的模擬信號調理電路相應指標。該指標有效滿足了綜合電子信息系統對于模擬前端的要求。

(4)高速采集電流與數據流實時存儲

該技術在本文設計中占據著核心地位。經過相關研究,最終確定以高速A/D轉換器結合FPGA主處理器作為系統實現方案。該方案實現了對單通道相應的1GS/s采樣率、雙通道相應的2GS/s采樣率、實時寬帶相應的16Gb/s二進制編碼形成的同步并行數據流的有效捕獲以及實時存儲。

(5)寬帶信號交替并行采集技術

該技術借助2個采樣率相同的采集通道按照一定時序對雙倍速采集通道進行合成。在本文設計中,通過深入研究A/D轉化器以及FPGA數據處理相應的時序,實現將兩個采樣率為1GS/s的采集通道對單個采樣率為2GS/s采集通道合成的交替并行采集技術,無需對硬件成本進行添加,即可使采集率相應的性能指標實現加倍。

(6)軟件系統設計

軟件系統包括如下兩部分:一,驅動程序。驅動程序訪問高速信號采集模塊相應的硬件寄存器,實現對底層各類硬件操作的控制,并將軟件訪問的相應接口提供于上層相關應用程序。二,波動顯示與控制相應的人機界面軟件。該軟件在Windows操作系統環境下運行,為用戶提供相應的人機界面,并借助驅動程序對底層相關硬件設備進行訪問。

4 系統測試

根據系統設計的具體要求,實施系統測試,以驗證高速信號采集模塊的具體功能和各項性能指標。基于采樣定理,任意模擬信號由A/D轉換器實施轉換之后,以數字信號的具體方式在數字域內對原始模擬信號相應波形進行重現,A/D轉換器具備的采樣頻率不能小于該模擬信號自身2倍的最高頻率分量。相關實驗證明,若A/D轉換器實際采樣頻率不小于所采集的相關模擬信號相應的5倍基波頻率時,所采集到的相應數字信號波形可實現對原始模擬信號具體波形的重現。

在實驗室相應環境下,對系統軟件及硬件各類模塊具備的功能和相關性能指標進行測試,對Agilent LXI33220A標準信號源或者Tektronix AFG3252標準高速信號源進行使用。

實驗測試相應的軟件環境如下:Windows操作系統;DataAquiLG軟件。其中,以20MHz/100mV正弦波作為模擬信號進行輸入。

實驗測試后獲取相應的波形圖,據圖可知基于FPGA的高速信號采集模塊具備的各項功能以及相關性能指標,均能完成預期目標。

本文設計的方案在3個cPCI標準模塊中,對模擬信號調理、數據處理顯示以及高速信號采集等核心功能進行劃分,確保用戶能基于自身各項應用需求對型號各異的標準模塊進行選配,實現對性價比和定制化程度均相對較高的高速數據采集系統的構建。該解決方案具有較強的適應性、靈活性以及可擴展性。另外,該解決方案在各類硬件指標上均能實現對cPCI計算平臺相關標準各項要求的良好滿足。

5 總結

本文研究了基于FPGA的高速數據采集系統的科學設計和有效實現,并對系統模塊實施了測試驗證。相關結構顯示,該系統能基于GS/s采樣率,實現高速數據采集的穩定性和可靠性。可對本文設計系統的高速數據緩存、采樣率以及主機總線接口等實施優化,還能將高速數據處理的各類功能,諸如插值算法以及傅里葉變換等添加于波形顯控軟件內。