基于FPGA的非壓縮高清視頻光纖傳輸關鍵問題研究

嚴 楓 成海龍 劉 濤 劉艷明 喬 鑫

(駐218廠軍事代表室 北京 100000)

0 引言

隨著工業用及商用對視頻清晰度及分辨率要求的不斷提高,視頻格式從低的600×480的分辨率發展至目前的超高清的4K級乃至8K級。這些劇增的視頻數據給傳輸應用帶來了巨大的挑戰[1-2]。例如,當視頻格式為4K級時,如以RGB4:4:4傳輸,幀率為60幀/秒,每個像素為8bit灰度等級,則一路視頻的有效最大數據速率為14.4Gbps。直接以網絡或者應用電纜的HDMI(High Definition Multimedia Interface)或者DP(DisplayPort)方式傳輸距離有限,現有應對長距離傳輸的方法可以采用基于H.265或者H.264的壓縮/解壓,通過以太網傳輸,或者基于FPGA(Field Programmable Gate Array)和光纖的方式進行無損非壓縮傳輸后直接恢復[3-5]。兩者相比較,后者由于采用非壓縮實時傳輸方式,對原有視頻無任何損失,且具有較小的時延及數據抖動,因此在視頻質量要求高的場所應用較廣泛。

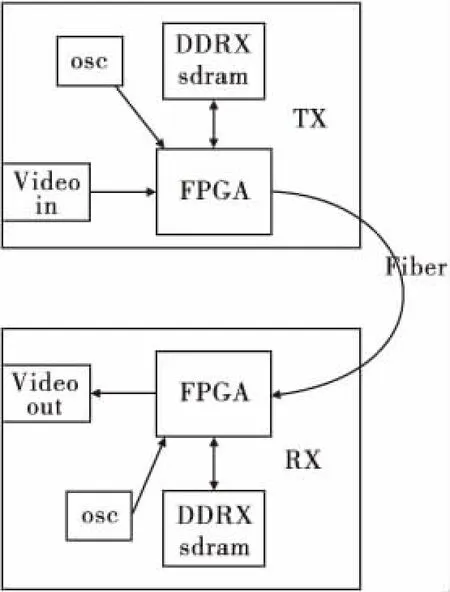

現有基于FPGA及光纖的高清長距離非壓縮視頻傳輸的方案模型可如圖1所示。

圖1 非壓縮光纖視頻傳輸方案架構圖

方案架構中TX為發送端,RX為接收端。其工作流程為:在發送端,超高清視頻流(Video in)輸入至FPGA中,FPGA在時鐘晶振OSC(oscillator)的驅動下,對視頻流的數據進行緩存處理,存儲至DDRxSdram(Double Data RateSynchronous Dynamic Random Access Memory,x為0-4) 并同步讀出,通過其自帶的高速串行數據口連接至高速光模塊進行發送;在接收端,高速光模塊接收帶視頻流數據的光信號,轉換為高速電信號輸入至FPGA高速串行數據口,FPGA對信號進行解碼,得到視頻流數據存儲至DDRxSdram。并同步讀出視頻數據,后在OSC的驅動作用下,恢復原有的視頻格式,輸出視頻流(video out),便于后續處理。

本文在研究這個方案傳輸機制的基礎上,針對其中的幾個關鍵技術問題,給出了解決方法,實現高效傳輸。其一是超大視頻流數據存儲訪問帶寬計算及帶寬分配調度策略;其二是視頻幀間動態同步及失步應對方式;其三是時鐘重建及視頻格式恢復方法。

1 超大視頻流數據存儲訪問帶寬計算及帶寬分配調度策略

視頻流數據進入FPGA后,在對輸入/輸出數據速率、系統內部帶寬及外部存儲器帶寬進行計算后,可采用更高速度的存儲器,并采取有效的調度策略,以此達到數據延遲時間短、資源利用率最高,系統性能最優的目的。

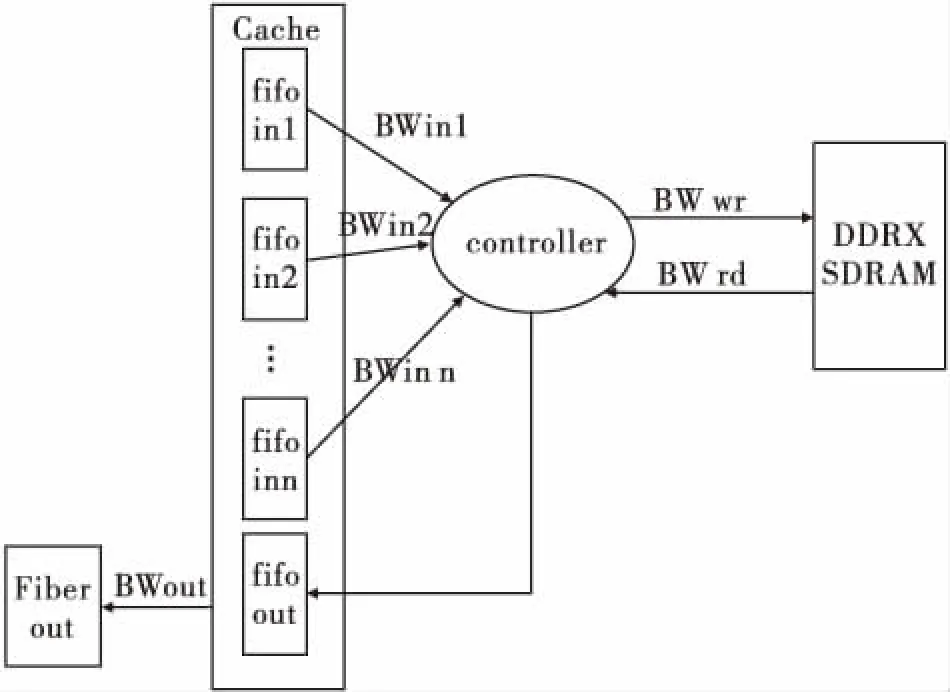

首先對所需的各個環節帶寬進行計算,得到理論值。系統帶寬計算結構可如圖2所示。

圖2 系統帶寬計算示意圖

圖2中fifo為先進先出(first-in-first-out),fifoin1至fifoin n為多路輸入視頻緩存區,fifo out為視頻數據輸出緩存區。BWin1至BWin n為讀取輸入視頻所需帶寬,BW out為視頻輸出帶寬,即為光纖傳輸的固定帶寬,BW wr為寫入外部存儲器的所需帶寬,BW rd為讀取外部存儲器的所需帶寬。在給定的存儲器條件下,其整體帶寬BW sdram為

BWsdram=BWwr+BWrd

(1)

給定視頻輸入總帶寬為

BWin=BWin1+BWin2+…+BWinn

(2)

為滿足視頻輸入數據不丟失要求,BW wr 必須大于或者等于BWin;且為達到光纖通道帶寬最有效利用的要求,BW rd必須大于或者等于BW out。BW rd與BWin無必然聯系,一般在視頻流無停頓及實時性的要求下,接收端輸出視頻顯示正常時,BW out的基本指標必滿足輸出視頻格式的24幀/秒以上,即BW rd≥BW out≥輸出幀頻24幀/秒。

按照上述視頻流數據計算所需帶寬后,實現帶寬最大利用率上需要考慮兩個方面。其一是FPGA內部數據高速獲取。在上述要求下,多路視頻輸入時,需要滿足在一個固定周期T內,每路輸入視頻數據均需至少讀取一次。為此,在給定外部存儲器的物理條件下,執行實現機構設計上最直接也是最有效的方法就是采用多層次存儲結構(Cache)進行視頻數據緩沖。其原理是依據分時復用或者分空間復用性,不斷刷新讀寫數據,使得內部功能單元能快速得到連續數據,可大為提升系統內部數據讀寫性能。具體實施上,需要考慮極限條件(讀寫數據最大速率)以及視頻格式,從而在資源利用最有效的情況下,決定Cache緩沖多少行視頻數據。Cache實現一般可采用FIFO或者片內RAM(Random Access Memory)。

其二是FPGA與外部SDRAM之間的數據讀寫最優方法。在操作現有的外部各類型大容量高速存儲器SDRAM的過程中,由于總線資源天然的共享限制,其讀寫操作必然存在沖突。為有效解決此類沖突,在設計中,采用令牌環調度方式(Round-Robin Scheme)或者固定優先級調度方式(Fixed PriorityScheme)。兩者各自存在自身的優缺點,前者帶寬均衡分配,存在延遲等待,浪費帶寬等問題。后者無延遲問題,會出現高優先級搶占低優先級的情況,導致低優先級通道數據可能丟失。為解決這些問題,綜合兩者優點,采用基于單時鐘條件下的動態總線競爭和Cache緩存相結合的方式。在每個時鐘的邊沿,讀寫調度邏輯控制器偵測當前總線歸屬狀態,以及每路視頻數據Cache空滿緩存情況,依次分配下一個時鐘的總線控制權。例如其中某路視頻輸入數據寫入SDRAM調度用邏輯語言可表示為:

IF(第1路輸入視頻緩存空 == 真 )且(第2路路輸入視頻緩存空 == 真)且(第3路輸入視頻緩存空 == 假 ) 且(第3路輸入視頻寫允許==真 )且(當前寫SRAM狀態 == 真 ),此時選擇滿足條件的第3路輸入視頻數據寫入SDRAM。讀寫調度邏輯控制器從第3路的Cache中讀取數據寫入SDRAM,且考慮SDRAM本身的讀寫效率,一般可選用行觸發方式。當第3路輸入視頻數據寫入SDRAM的數據數量計數比SDRAM一行數據數量少1時,第3路輸入視頻寫允許為假,第3路輸入視頻數據放棄總線控制權,控制權移交給其它數據通道。如其它通道滿足類似條件,其就獲得總線權;如有多個通道滿足條件,由于存在Cache緩存,后響應的通道數據不會丟失,只是響應滯后,此時Cache緩存容量需要滿足最長時間訪問要求;如都不滿足條件,總線浪費的帶寬所用時間為通道數乘以時鐘數,依據此方式,SDRAM總線控制調度可獲取最高帶寬利用率。

2 視頻幀間動態同步及失步應對方式

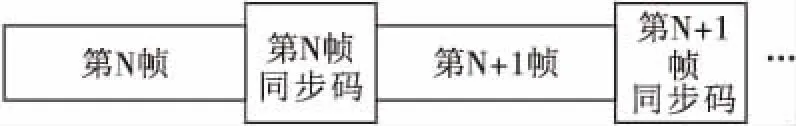

輸入視頻在傳輸中總是會存在輸入視頻源斷開、光纖斷開以及輸入端電路斷電等各種斷路情況,導致從發射端傳輸至接收端的視頻為不完整的一幀圖像。而斷路情況恢復正常后,接收端需要得到完整的幀圖像,且在接收端接收到的視頻數據為無限長的數據流,需要從數據流中分割出獨立的每幀圖像進行緩存、處理及顯示。解決這些問題需要采取視頻幀間動態同步方法。現有幀同步實現方法有兩種:一種是插入標志幀同步法;另一種是利用間隔固定時隙插入固定位同步的方法實現。如圖3所示,本文采用第一種方法并對輸入視頻的格式進行編碼,形成固定長度的標志同步碼。

圖3 幀同步示意圖

建立同步碼需要考慮如下幾個問題:

1)同步碼長度與誤碼率的關系。由于視頻數據樣本量大,若選取同步碼長度短,出現視頻數據與同步碼一樣的概率大。在極限條件下,參考KRONE誤碼率標準10E-12,即零誤碼率標準,其倒數換算成十六進制為0X0E8D4A51000,長度為40位二進制。選取同步碼長度可為40位以上,當選取40位以上長度的同步碼后,出現視頻數據本身與同步碼一致的概率接近于0。

2)碼字選取。確定同步碼長度后,選取碼字參照8421編碼方式以及滿足信號線路均衡需要,選擇同步碼為“0XAA55F0F08421”。

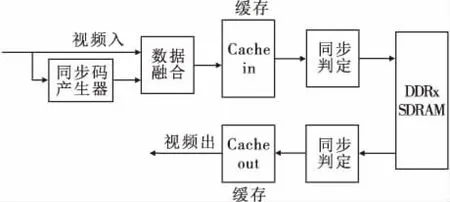

3)在FPGA內部的同步實現上,建立如圖4所示的緩存輸入輸出均同步的同步機制。

圖4 同步機制

在發送端視頻輸入的同步判定中,當且僅當檢測到同步碼時,從緩存cache in中得到的第一個輸入視頻數據(可以是RGB4:4:4或者YCrCb4:2:2格式)寫入至SDRAM中本路輸入視頻定義的初始地址,后續依次從緩存cache in讀取數據寫入SDRAM。依此方式至下次檢測到同步碼,重復開始寫入新的一幀輸入視頻數據。從SDRAM中讀出視頻數據傳輸給緩存cache out時,依舊是當且僅當檢測到同步碼,下一行(SDRAM獲取數據按行突發方式)讀取的地址必為本路輸出視頻定義的初始地址。

在接收端視頻數據的同步判定中與發送端處理一致,只是當同步碼丟失后,必須能夠重新同步。本文中采取的方式為,設定一個固定時間(該時間應長于2幀圖像間隔時間),在此時間內無同步碼出現,清除輸入cache in緩存的數據,寫入SDRAM的地址清零至初始地址,從而確保完整的一幀圖像輸入至接收端的緩存cache in中。由此機制及按帶寬計算的要求,可在滿足實時視頻數據的輸入與輸出速率需要的同時,極大降低了視頻數據幀誤碼率,解決上述文中所提及的各種輸入視頻數據斷路問題,提高了視頻輸出顯示的穩定性。

3 時鐘重建及視頻格式恢復方法

按行業內視頻各種格式標準,視頻輸入端的分辨率格式可從640×480@50Hz至4096×2016@60Hz,時鐘頻率從25MHz至297MHz,涵蓋幾十種格式及頻率,而視頻輸出端不能通過其他有效方式獲知發送端視頻格式,但同時需自動輸出相同視頻格式。為滿足此要求,本文給出一種編碼及自適應的方法。步驟為:

首先在發送視頻輸入端進行格式編碼。參照圖4,在視頻發送端,同步碼發生器通過計數檢測視頻輸入行的有效像素個數、一幀中行的行數目及一幀的場同步間隔時間,從而可確定輸入視頻格式。獲知格式后,采用8bit對視頻格式進行編碼,例如,0×01表示為640×480@50Hz,0×02表示為640×480@60Hz,…,0×0FF表示為4096×2160@60Hz。其可表示的格式類別為256種,能夠滿足現有絕大部分視頻格式。格式編碼完成后,此編碼數據與視頻輸入數據融合一起寫入緩存cache in。

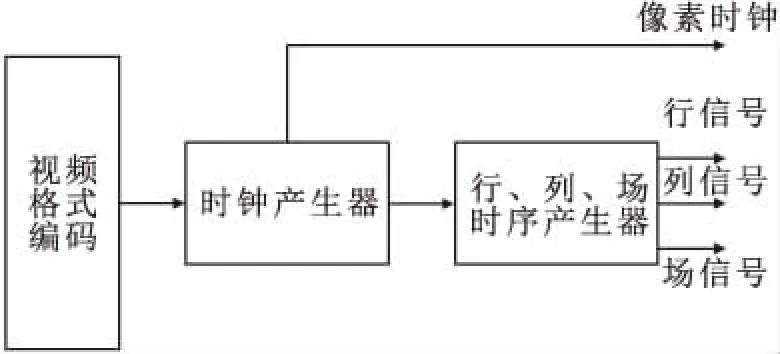

其次在接收視頻輸出端進行解碼及恢復視頻格式。上述編碼一直隨視頻數據進行緩存、寫入SDRAM及傳輸至接收端輸出。當接收端從SDRAM讀出視頻數據輸出至緩存cache out時,視頻數據同步判定完成后,可獲取當前的視頻格式編碼。得到格式編碼,需恢復視頻格式。恢復視頻格式的過程包括產生輸出視頻像素時鐘及行、列、場同步信號,如圖5所示。其中重點為產生合適的輸出視頻像素時鐘,現有的產生方式有FPGA片內產生及片外專用芯片(ASIC)產生。圖5中產生的行信號作為讀取緩存cache out的有效使能信號,在像素時鐘及行、列及場信號的作用下,讀取視頻數據輸出直接顯示。

圖5 視頻格式恢復示意圖

4 實驗驗證

為驗證本文中所提出方法的可行性,設計如圖6所示的實物進行驗證。實物設計采用了Xilinx公司的Spartan6中的XC6SLX45器件及二片外置SDRAM。采用了ChipScope工具在線進行數據及時序觀測,觀測的結果如圖6所示。

圖中的數據獲取結果表明,帶寬的調度及同步碼的方式能夠滿足要求。

最后,進行光纖視頻的傳輸,傳輸的視頻格式為1920×1080P,視頻輸出顯示結果如圖7所示。并經過長時間連續測試,視頻輸出無抖動,無像素缺失;在接收端進行斷電,光纖拔插,視頻均能自動恢復。

5 結束語

非壓縮的高清或者超高清視頻光纖傳輸方式與采用直接電纜方式、壓縮傳輸方式或者網絡傳輸的方式比較而言,在延長視頻傳輸距離及保障視頻質量方面具有一定的優勢。本文在基于FPGA電路的基礎上,對大容量視頻數據的光纖傳輸的方法進行了較為深入的討論。對其涉及的幾個主要問題,如帶寬的計算及調度、幀同步機制的建立與實現以及視頻格式的自適應恢復等提出了解決方法。后進行了電路實物設計驗證,驗證的結果實現了視頻長時間穩定透明傳輸,表明文中所提方法具有可行性,并可為未來需要高質量視頻如超高清8K級或者其它方式的光纖傳輸提供了一條路徑。