SOPC通用化彈載自測試平臺的設計與實現*

陶然,王昭磊,羅悅,田琨

(1.北京航天自動控制研究所,北京 100854;2.北京電子工程總體研究所,北京 100854)

0 引言

傳統的導彈武器測試方法為地面測試,通過綜合測試系統完成對導彈內部各產品硬件、軟件及系統功能、特性的全面檢查,將彈上各測試信號全部引入地面,通過各類測試設備完成測試功能。地面測試方法需將大量待測信號經過長線傳輸引入地面設備,影響測試準確性,導致彈地接口龐大,地面測試設備復雜度高,資源消耗大。

隨著武器系統的智能化、網絡化發展,在不增加過多的有效載荷情況下使得彈載自測試功能逐漸可行,簡化了彈地接口,降低了彈上產品和地面產品的耦合度,可獨立進行模塊化、通用化設計,降低了研制成本。若設計一種功能通用、擴展性好、可靠性高的彈載自測試設備,根據不同的被測產品進行快速的配置實現一個測試平臺測試多種產品的功能,既可以減少資源重復、通用性差的問題,同時大幅降低導彈武器系統研制成本。

1 系統架構設計

1.1 彈載自測試架構現狀

現階段彈載自測試技術系統架構主要分為2種:

(1) 基于彈上載荷實現的非獨立式自測試架構。主要應用于對小型化要求較高的武器系統中,利用彈上載荷中未使用的空閑資源實現彈載自測試,其測試電路與彈上功能電路集成于同一印制板內,測試電路的可靠性直接影響彈上載荷飛行的可靠性,且測試資源受制于彈上載荷的空余資源,存在一定的局限性,且無法實現通用化。

(2) 基于DSP(digital signal processing)+FPGA(field programmable gate array)的獨立彈載自測試架構[1]。隨著武器系統復雜程度的不斷提升,利用DSP作為核心處理器同時輔助FPGA擴充處理器接口資源,此類架構需要針對2類芯片設計獨立的外圍電路以及專用的外部總線進行數據交互,可靠性較低,且需要針對DSP及FPGA獨立進行開發,增加了調試及開發的成本。

本文提出SOPC彈載自測試架構,SOPC資源豐富,硬件電路設計及軟件開發集成于單個器件內,降低開發成本的同時具備較強的通用化及可擴展性,可以滿足現階段武器系統復雜測試及小型化的需求。

1.2 SOPC技術

SOPC,即片上可編程系統(system on a programmable chip,SOPC),通過可編程邏輯技術將整個系統集成到單個芯片上,是一種新型的嵌入式系統,結合了SOC,PLD,FPGA的各自優勢,片上資源豐富,包括嵌入式處理器、DSP、存儲器、外圍IO及可編程資源,同時是一種具有靈活設計方式的可編程系統,具備可剪裁、可擴充、可升級的特點。

基于SOPC技術的處理器按類型分為軟核處理器與硬核處理器2種。軟核處理器即通過FPGA邏輯源碼構建出虛擬的處理器,處理器實現是以邏輯源碼的IP核方式進行設計,用戶可以根據自己的需求修改IP核[2]。硬核處理器是固化在FPGA內部的獨立處理器內核,用戶只能對其進行配置而不能對其接口進行修改與替換,即固化在FPGA內部的ASIC(application specific integrated circuit)電路,性能上硬核處理器運算速度較高,整體功耗低。基于SOPC的通用化彈載自測試平臺作為武器有效載荷之一,首要考慮的是其可靠性與環境適應性,其次需要具備高通用性,適應多種類型接口數據的高速處理與運算,硬核處理器環境適應性強、可靠性高,通過基于ARM COTEX A9的硬核處理器SOPC芯片,實現了應對復雜環境條件下的高可靠彈載測試。

1.3 平臺架構設計

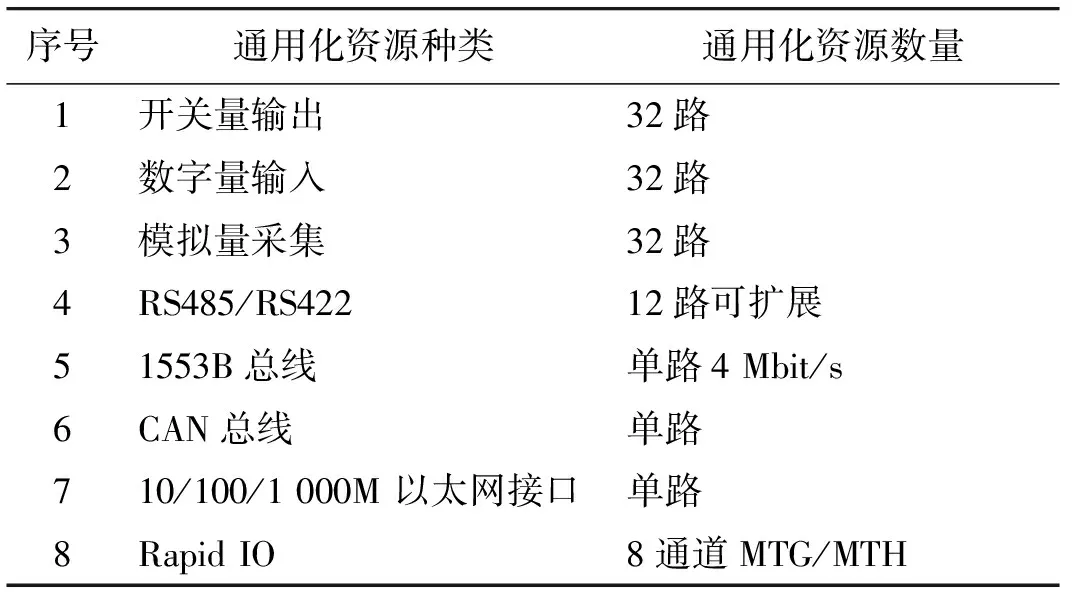

彈載自測試平臺基于小型化、通用化的原則,與彈上計算機進行集成化設計。現有導彈武器系統對彈載測試資源類型的需求相同,其中數字量、模擬量為通用測試資源需求,不同裝備型號的測試信號數量不同,所選用的總線類型不同,為滿足通用化需求,彈載自測試平臺可設計足夠的數字量信號,且同時具備多種不同類型總線通訊功能,彈載自測試平臺通用化資源詳見表1所示。

表1 彈載自測試平臺通用化資源Table 1 General missile-borne self-test platform resources

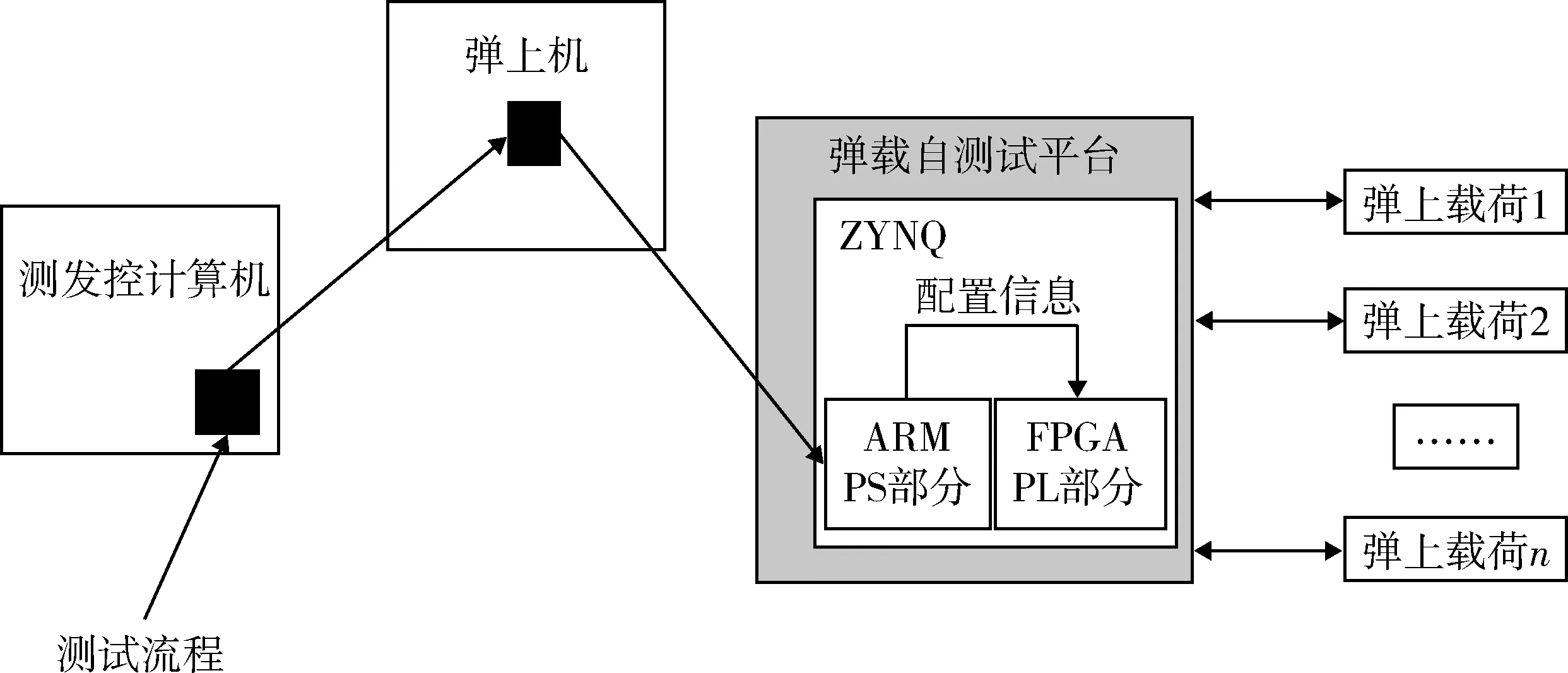

本文提出的基于SOPC技術的通用化彈載自測試平臺系統架構如圖1所示,整個自測試平臺以SOPC處理器為控制處理核心,外部連接電源模塊、DDR3存儲器模塊、SPI FLASH模塊、各類通信模塊、模擬量隔離及信號調理模塊以及數字量輸入輸出模塊,其中通信模塊包括1553B總線、CAN總線、RS485/RS422、以太網以及RapidIO,通信模塊可兼容不同型號裝備的通信需求,以最大程度上保證平臺的通用性。SOPC處理器IP資源豐富,同時基于FPGA的可編程特性實現數字量輸入、輸出接口以及各類總線通信接口的可配置功能,以適應各類復雜系統的測試需求,此外考慮到后續機內總線的發展與應用,預留Rapid I/O接口滿足后續彈上計算機機內總線的縱向擴展功能。

彈載自測試平臺作為彈上計算機的機內載荷以子板連接的方式與彈上機進行連接,為實現獨立有效性的彈載測試,應最大程度上減少與彈上各設備的耦合性,故自測試平臺設計采用獨立電源與彈上機隔離,各對外接口進行電平隔離,最大程度上保證測試的有效性及可靠性。

2 硬件平臺設計

2.1 SOPC架構設計

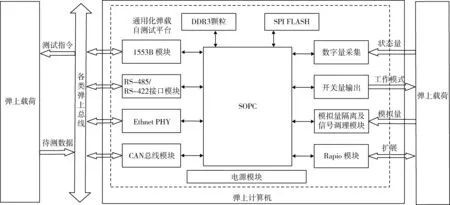

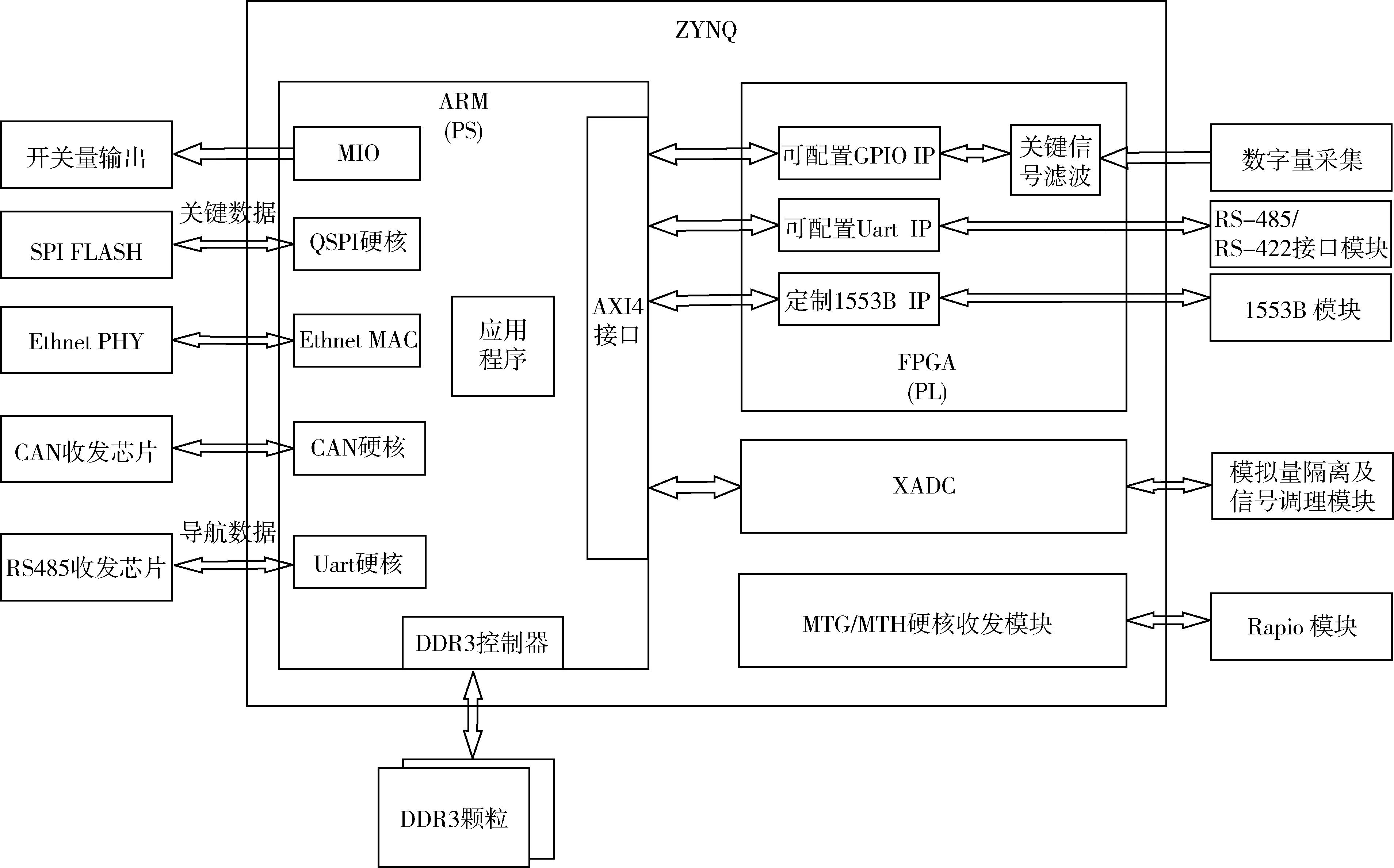

本文采用ZYNQ[3-4]SOPC實現通用化彈載自測試平臺,ZYNQ由多個ARM COTEX A9硬核及傳統FPGA邏輯資源構成,通過內部總線將ARM核PS部分(Processing System)與FPGA的PL部分(Programmble Logic)部分互聯為一個整體,以此獲得高內聚、低耦合的SOPC架構。通過利用PS部分靈活裁剪的各類接口控制器以及PL部分強大而靈活的IP核資源實現SOPC處理器設計[5-6],SOPC架構如圖2所示。自測試平臺采用了PS部分可配置硬核Uart接口接收彈上計算機母版的RS-485導航數據,通過ARM硬核處理器對關鍵導航節點參數進行實時判斷后,將測試結果通過可配置硬核CAN總線接口控制器或Ethnet接口控制器傳輸至地面,為滿足彈上機導航數據的高實時性處理及有效性數據鑒別要求,通過高度集成的DDR接口控制器完成外部DDR3的高速數據存儲與運算,同時通過多路MIO(Multiuse I/O)接口輸出關鍵測試信號及指示,確保外部被測彈上載荷與測試平臺的測試狀態統一有效。考慮到自測試平臺的通用性與可擴展性,在PL部分設計了1553B接口控制器IP核、雙向多路可配置GPIO IP核、高可靠可配置Uart IP核、以及XADC運算硬核,各IP核通過AXI4總線掛載至硬核處理器端,面對數據量較大且實時性高的彈載測試多個硬核間可以進行獨立配置與并行處理,可由運行于ARM處理器中的頂層應用程序統一控制。通過MTG/MTH硬核收發模塊設計多路Rapid IO高速通信以增加自測試平臺的數據傳輸縱向性能擴展能力[7-8]。

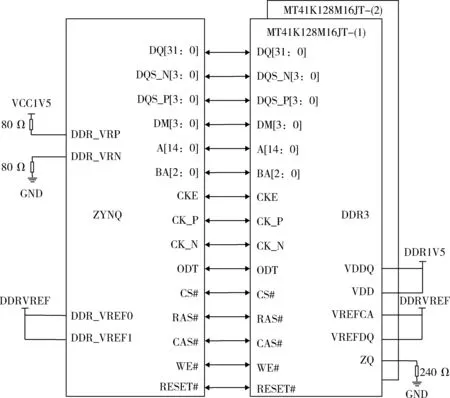

2.2 DDR3緩存模塊設計

彈載自測試平臺通過接收總線指令進入彈載測試模式,根據不同測試流程的配置,并行采集外部各類通信接口、數字量及模擬量的消息,將采集到的數據傳輸至ARM處理器進行判斷與決策,選用2片DDR3顆粒構建外部32-bit存儲模塊,存儲容量達512 MB,最大支持533 MHz時鐘頻率,充分滿足大數據量彈載測試的實時性需求。DDR3存儲顆粒與PS部分DDR3硬核控制器相連[8],通過并聯2片DDR3中的數據總線DQ[15∶0],數據選通差分信號DQS_N[1∶0],DQS_P[1∶0],數據寫入標志信號DM[1∶0]3類信號,使其擴展為DQ[31∶0],DQS_N[3∶0],DQS_P[3∶0],DM[3∶0],實現方式如圖3所示。

圖1 通用化彈載自測試平臺系統架構Fig.1 Architecture of general missile-borne self-test platform

圖2 SOPC架構設計Fig.2 Architecture of SOPC

圖3 DDR3緩存模塊Fig.3 DDR3 cache module

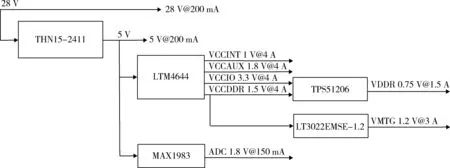

2.3 電源設計

通用化彈載自測試平臺作為獨立測試平臺,需要具備穩定可靠的電源以提供準確的測試結果,采用外部28 V供電作為整體輸入,通過2次電源轉換為5 V電源后供各模塊使用[9],平臺2次電源與彈上計算機電源物理隔離,由于SOPC及外部應用電路種類較多,考慮小型化設計整體思路,電源設計應最大程度上遵循一轉多路、復用等原則,電源設計如圖4所示。

選用可配置4路4 A輸出通道陣列LTM4644電源模塊提供SOPC需要的1 V內核電壓、1.8 V輔助電壓、3.3V I/O電壓以及1.5 V DDR3存儲電壓,LTM4644最大支持4通道獨立輸出,可通過外部電路配置輸出電壓范圍,內置開關控制器、功率FET、電感器等組件,體積小且集成度高,同時具備過壓、過流及過熱保護,最大程度上保證彈上載荷的可靠性,保證設計安全性,可有效避免因測試狀態不確定而造成的彈上負載損壞的情況。同時選取3種線性電源實現MTG模塊1.2 V電源電壓、0.75 V DDR參考電壓以及1.8 V ADC電源供電。通過設計自測試平臺SOPC及外圍電路上電順序提升系統可靠性,遵循5 V上電后,內核1.0 V上電,1.8 V輔助電源至3.3 V IO上電,最后DDR模塊上電的順序,有效避免內核未啟動的狀態下IO上電后輸出不定態導致的誤發測試指令。

2.4 通信控制模塊設計

隨著彈上載荷復雜化的趨勢,武器系統所采用的數據傳輸接口從最初的單路點對點傳輸發展為組網協同多路冗余傳輸,傳輸速率也從Mbit/s發展至100 Mbit/s,武器系統常用的各類數據傳輸總線包括1553B總線、CAN總線、RS-485總線及以太網,為最大程度上實現通用化彈載自測試平臺,通信控制模塊兼容目前各類總線通信接口,以應對不同武器型號的運用,同時應具備高速數據傳輸擴展能力[10]。本文通過設計1553B控制IP核控制外部總線協議芯片的方式實現1553B總線通信,RS485總線、CAN總線及以太網通過PS部分硬核控制器配合外部總線收發器及PHY芯片進行實現,同時通過PL部分設計可靠配置Uart IP核擴展12路RS-485/422接口以滿足不具備總線接口的彈上載荷數據傳輸。

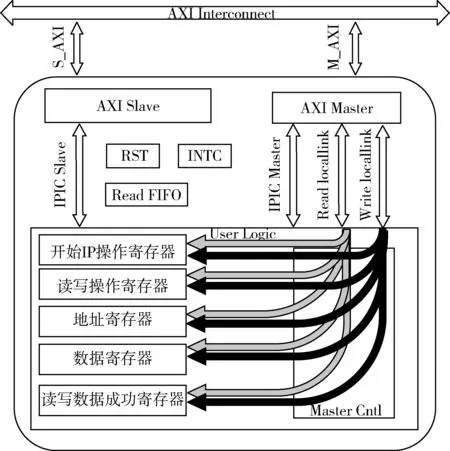

2.4.1 1553B IP核設計

為實現1553B子地址、應用層協議通用可配置,用硬件描述語言實現1553B控制器IP核模塊控制外部1553B協議芯片。本文選用國產化1553B協議芯片,總線傳輸速率由傳統的1 Mbit/s提升至4 Mb/s,電平標準兼容LVTTL,可直接與FPGA的IO口3.3 V電平進行直連,在實現通用化1553B通信的基礎上,具備一定的總線速率擴展能力。IP核模塊具備AXI4(Advance Extensible Interface 4.0)總線邏輯功能,以外設的方式掛載至ARM處理器,采用通用化設計思想,可通過處理器在線配置的方式可更新1553B子地址、站點等內容。針對不同型號,可進行在線重配置與應用層二次開發。同時,處理器端應用程序通過軟件的方式實現復雜協議與幀結構解析,設計成本降低的同時增強了模塊靈活性。

基于AXI4總線的1553B控制IP核設計組成如圖5所示,IP核由AXI4總線接口部分與用戶邏輯塊兩部分組成,ARM處理器通過AXI總線互聯(AXI Interconnect)將控制信號及數據流傳送至AXI4 IP中總線接口部分完成總線地址譯碼,譯碼后的數據流寫入1553B用戶邏輯塊(1553B User Logic)中相應寄存器,用戶邏輯塊控制外部1553B協議芯片完成數據收發,將收到的數據寫入用戶邏輯塊數據寄存器,同時操作讀寫數據成功寄存器置位,用于向處理器指示當前IP核工作狀態,運行于ARM處理器上的應用程序周期性查詢該地址空間,確定數據發送或接收狀態以及后續數據收發決策。

圖4 電源設計Fig.4 Power design

圖5 基于AXI4總線1553B的IP核Fig.5 1553B IP core based on AXI4 bus

2.4.2 Uart模塊設計

SOPCUart模塊由PS部分硬核Uart模塊與PL部分高可靠Uart IP核共同組成,外部通過MAX3485收發芯片實現RS485/422串行通信,資源數量總計14路。利用PS部分Uart硬核接收彈上機下傳的導航解算數據及配置信息,PS部分外部收發芯片硬件上關閉的發送使能,使其上電后始終工作在接收狀態。其余Uart模塊均通過PL部分進行擴展,為增加串行數據傳輸的可靠性及有效性,擯棄傳統IP核資源,自行設計了具備高可靠性的Uart IP核,高可靠Uart IP核最大支持921 600波特率,奇偶校驗位可設置,IP核針對所配置的波特率進行16倍頻后作為數據采樣時鐘,對每一比特位串行數據進行三取二表決操作,所采集到同一比特的3個數據中連續2個數據相同時則視為有效數據,可有效排除因各類干擾引入的錯誤數據,增加了彈上測試的可靠性。IP核具備AXI4總線接口邏輯,IP核所采集到的串行數據通過可通過AXI4總線傳輸至ARM處理器端供頂層應用程序進行協議解析與處理。

2.4.3 CAN總線及以太網設計

CAN總線及以太網設計均采用PS部分硬核模塊配合外部電平轉換及PHY芯片實現。CAN總線協議及以太網MAC層協議由PS部分硬核實現,硬核結構精簡且可靠性高,搭配外部芯片大大降低了開發成本。采用隔離型CAN總線收發器ADM3053實現CAN總線信號下傳,ADM3053將雙通道隔離器、CAN收發器與DC/DC轉換器集成于單個器件中,兼容5 V/3.3 V電平,以最小硬件資源設計實現隔離CAN總線的收發控制。考慮到自測試平臺的通用化設計,選用88E1518以太網PHY芯片,根據不同頻率的外部晶振自適應IEEE 802.3協議以太網10/100/1 000 MB帶寬,支持RGMII(reduced gigabit media independent Interface)接口,具備同步時鐘恢復及自動極性矯正、支持低VIO壓供電。

3 平臺軟件設計

3.1 驅動層軟件設計

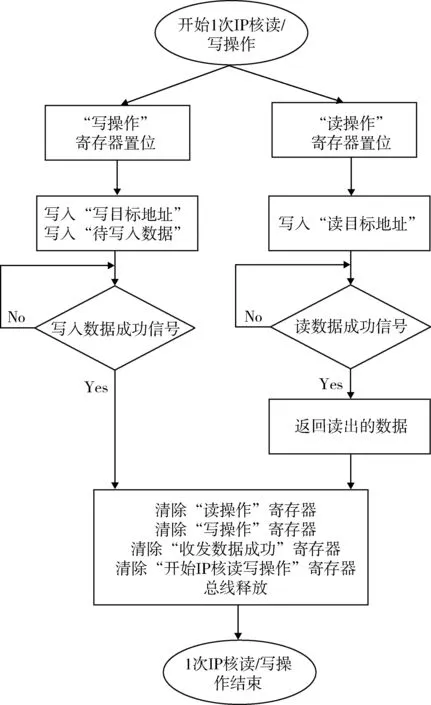

驅動層作為應用程序與IP核之間的紐帶,實現IP核的控制與數據處理收發。應用程序通過驅動層將相應地址的寄存器置位后,開始1次數據傳輸周期[11-12]。1553B IP核讀寫操作流程如圖6所示。

圖6 1次1553B IP核讀/寫操作Fig.6 A 1553B IP core read/write operation

開始1次數據傳輸周期后,首先將“開始IP操作寄存器”置位,之后對應讀寫操作,分別將“讀操作寄存器”或“寫操作寄存器”置位,之后寫入“寫目標地址”、“待寫入數據”或“讀目標地址”,驅動層循環查詢讀/寫數據成功信號,數據成功后,若為讀數據操作,則返回IP核所讀出的數據后復位各寄存器狀態,寫操作則直接復位各寄存器,至此1次IP核操作結束。

3.2 應用層軟件設計

彈載自測試平臺應用層軟件需要周期性查詢地面測發控系統發送的總線測試指令,收到測試命令進行測試項目解析后分發至各模塊開始測試,需要將采集到的各類的接口數據按協議組成對應幀結構后,通過總線進行下傳,其中包括采集I/O口數據、AD模擬量數據、RS485數據等。應用層軟件設計流程如圖7所示。

自測試平臺上電后,首先通過Begin_T()函數查詢總線自測試開始命令,當收到自測試開始指令后,執行Scanf_Bus()函數查詢地面測發控發送的測試項目指令,通過解析測試項目,分別向彈上模塊A,B,C發送RS485,IO以及AD測試指令,其中模塊A測試指令通過485消息發送,模塊B,C測試開始指令通過約定的GPIO發送。開始測試指令發送后,延遲5 ms應用程序查詢GPIO以確認各模塊返回的的測試結果準備好狀態,當收到準備好狀態后,讀取各接口的測試數據,最后向各測試模塊發送測試結束指令EOC_T_Uart(),EOC_T_IO(),EOC_T_AD(),各模塊狀態復位。應用程序將各模塊返回的測試結果進行組幀,通過總線發送至地面測發控。

4 自測試平臺配置方法

系統測試流程由地面測發控計算機控制,第1次測試開始前需要對自測試平臺進行配置,當配置完成后,后續的測試即可直接向自測試平臺傳輸帶有配置信息校驗幀的測試流程碼。測發控計算機向彈上機上傳武器型號配置文件,彈上機收到配置文件后將結果解析后通過Uart接口傳輸至彈載自測試平臺,自測試平臺應用程序根據彈上機傳輸的配置信息,解析出詳細的接口配置信息并記錄相應的校驗信息,將配置信息寫入PL部分配置寄存器,從而配置自測試平臺各對外接口通道數量及通道狀態。同時配置信息會備份至FLASH存儲器中[13-15]。配置完畢即可進行正式測試流程,自測試平臺接收彈上機下發的測試流程碼,將測試流程碼通過不同的接口如IO,Uart等分別傳輸至各彈上載荷,各彈上載荷回復相應的測試流程確認幀后,進入模塊自測試,此時自測試平臺同步接收各載荷傳輸的測試數據或測試結果,將測試結果組幀后,通過總線進行下傳。整體操作可重復配置,最大限度降低系統功耗的前提下實現了在線動態可配置。如圖8所示。

圖8 自測試平臺配置方法Fig.8 Self-test platform configuration method

5 結束語

本文基于導彈武器彈載測試系統的通用化、輕小型化需求,提出了基于SOPC的彈載自測試技術,充分發揮了FPGA的硬件可編程性、實時性、高度集成性、可靠性的特點,大大提高了彈載自測試平臺的通用化和可靠性,并且該系統結構簡單,性能可靠,最后給出了彈載自測試平臺在線配置方法,配置方法靈活,極大程度上降低了系統測試的成本。

SOPC通用化彈載自測試平臺需要在實際應用中不斷積累和完善,在以下2方面可以進一步改進:

(1) SOPC器件的國產化替代,現階段尚無同等資源數量的SOPC器件替代,可以針對實際應用場合縮減部分資源以實現器件的國產化;

(2) 擴展測試資源,現階段通用化平臺空余資源仍較為充裕,可以根據實際需求進行資源橫向擴充,以及利用靈活的IP資源進行縱向擴展。