基于單片機的數字合成波形發生器

□ 李鍵傑

一、概述

信號發生器,也稱信號源,就是能夠產生并輸出符合用戶要求的電信號的裝置或儀器。信號發生器的基本構成主要有頻率產生單元、緩沖放大單元、調制單元、輸出衰減和阻抗變換單元、指示及調節控制單元等。其核心和基礎的部分,是頻率或波形產生單元。

根據頻率產生方式可分為諧振法和合成法兩種。諧振法是傳承傳統技術的方法,即用具有頻率選擇性的諧振回路來產生正弦振蕩,并獲得所需頻率。頻率合成法是指由一個或多個頻率穩定度和精確度很高的參考信號源通過頻率域的線性運算,產生具有同樣穩定度和精確度的大量離散頻率的過程。

二、頻率合成技術

頻率合成可分為直接頻率合成和間接頻率合成。而時下大多數研討的是直接頻率合成模式,這其中又分為非相干直接合成和相干直接合成。而相干直接合成模式大致可概括為直接數字合成(DDS)和直接模擬合成(DAS),間接模擬合成(PLL)和數字合成(PLL)。

DDS是一種全數字化的頻率合成器,由相位累加器、波形ROM、D/A轉換器和低通濾波器構成,是一種從相位概念出發直接合成所需要波形的新的頻率合成技術。DDS實質上是對一個(或少許幾個)參考頻率進行數字分頻的技術,通過編程頻率控制字來對系統時鐘進行分頻,從而獲得所需要的頻率。由于DDS工作在數字域,很方便得到任意周期以及非周期波形。

三、基于單片機的數字頻率合成

本文論述的數字合成波形發生器是一個實驗裝置,主要通過實驗加深對DDS的運行過程和技術特點的理解和掌握。

(一)電路構成

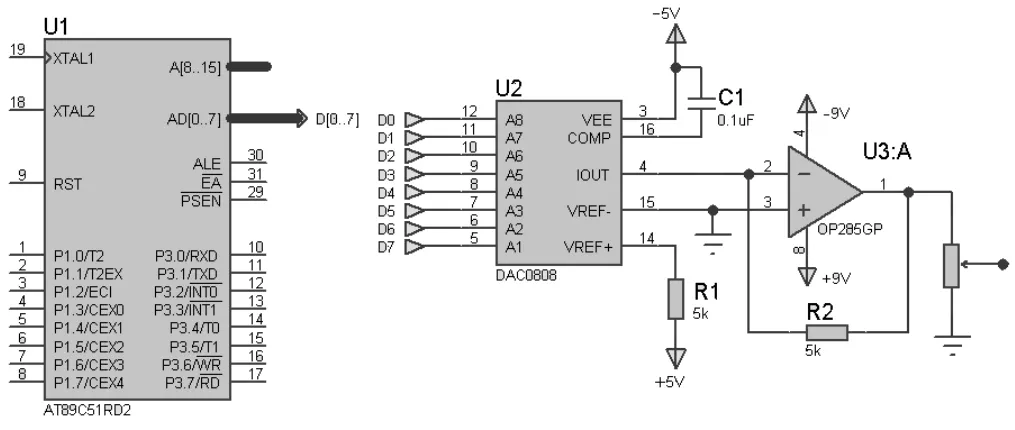

實現數字頻率合成主要由單片機和數模轉換器DAC構成,并沒有采用專用的DDS模塊,而是通過單片機來實現DDS的部分功能。

上圖是一幅仿真示圖,現在的單片機有很多都把數模轉換器DAC集成到單片機里面去了。

對照DDS構成原理和流程:

Fc→地址計數器(÷N)→波形存儲器→D/A→LPF→fo

以DAC模塊為界分為前后兩個部分,DAC及后面部分,就是一個PCM譯碼輸出的過程。而DAC前面部分,主要是生成符合要求的PCM二進制碼組,而這部分在本實驗里將由單片機通過運行程序代碼來實現。

(二)DAC譯碼轉換過程

當DAC接收到一個二進制數經譯碼后輸出一個與其基準電壓VREF為參照的電壓值,即量化樣值,并保持直到DAC接收下了一個數才會改變。因此在連續輸入一串二進制數組的過程中,DAC的輸出將是一串階梯波,如下圖b,然后經低通濾波器濾除高頻分量,便可得到模擬信號。顯然譯碼輸出階梯波要比還原為PAM波形(如下圖a),其高次諧波含量大為減少,從而也降低了對濾波器的要求。

圖b是二進制碼組經DAC譯碼還原為量化后的階梯波序列,階梯級數對應脈沖抽樣次數。因此其實質為以階梯波來逼近所要得到的模擬信號波形。

那么如果要輸出的是周期信號,則其波形周期為:T=Tc×N。

Tc是階梯的脈沖寬度(每一級等寬),N是階梯級數。可見其實質就是實現了一種數字分頻,Tc就是合成頻率的基準信號參數,稱謂參考時鐘信號周期,T則是合成波形周期。改變輸出信號周期,一是保持階梯寬度Tc不變而改變階梯級數N,二是保持階梯級數值N不變而改變階梯寬度Tc,三是同時改變Tc、N。本實驗裝置采取保持階梯寬度Tc不變而改變階梯級數N的形式來改變輸出信號頻率。

(三)PCM的編碼要求

單片機應用中常用的DAC芯片僅適用于單極性處理方式,采用的是自然二進制編碼的PCM。即二進制碼最小值為全0,中間值則按自然二進制遞增規律遞增,最大值為全1,每一個二進制碼對應一個量化電壓值。

為了對應上述DAC模塊對PCM編碼的要求,需要采用自然二進制碼,均勻抽樣均勻量化,而完成把模擬信號變換為二進制碼組。

(四)波形數據的生成

為了對應DAC特性,設想要得到的波形,首先是一個單極性的信號,最小值為0V,峰值小于5V(或者是小于DAC的參考電壓VREF)。對其進行均勻抽樣均勻量化及自然二進制碼編碼,從而取得PCM二進制碼組的波形數據。

在波形切換或者改變頻率時,需要重新計算并生成所需要的PCM二進制碼組。這大大降低了對內存資源的要求,這里不強求切換速度。

(五)合成信號的參數

從存儲器傳送數據到外設DAC的快慢,決定了輸出階梯波的寬度Tc。

在CPU指令代碼運行形式中,有兩種方式。一是采用中斷運行方式,這是通常做法。其優點是,很便利地降低參考時鐘頻率,也降低了N的資源占用度。而其缺點則是Tc無法取得更小,不利于提升合成頻率。因為執行一句P0=waveArray[N]的C語言語句,大致需要14個機器周期,而執行中斷最基本的現場保護與恢復指令,大致就要消耗24個機器周期,在只允許一個中斷例程運行的條件下,中斷間隔都需要在50個機器周期以上,如果一個機器周期為1uS,則Tc=50uS,Fc=1/Tc=20KHz。二是禁止一切中斷運行,在設置好波形參數后就直接進入向DAC傳送數據的死循環,只有通過復位CPU才能推出循環。如執行一句P0=waveArray[N]的語句,大致需要14個機器周期,那么Tc=14uS,Fc=1/Tc=72KHz。顯然這種方式得到的時鐘脈沖頻率提高了很多。其中waveArray[N]表示儲存有待輸出波形的二進制數組,若是合成周期信號波形,那么就是一個周期的數據,共N個抽樣量化的數據值。

上述討論中,機器周期的長短也是限制時鐘脈沖頻率提高的一個因素,只是畢竟C51單片機的運算能力有限,通過選型來提升的空間也有限。

然而,進一步提高時鐘脈沖頻率的方法是采用DMA(直接內存存取)技術。現在性能好的單片機,都內含有DMA(直接內存存取)技術,由于數據從存儲器到外設DAC的轉移是通過硬件直接實現的,無須CPU的干預,其內存存取周期比CPU指令序列的運行周期快多了,大致得到Tc≤機器周期的傳輸速率,也不受CPU其他中斷的影響。因此,在相似條件下,單片機利用內置的DMA設備可提高合成信號頻率,在相對的低頻段輸出頻率信號方面,則通過中斷方式的運行。

由于本實驗是工作在數字域,很方便得到任意周期以及非周期波形信號。

四、結語

本實驗裝置數字合成波形發生器,由單片機、數模轉換器(DAC)、直接內存存取控制(DMA)構成,主要通過DMA來獲得更高合成頻率,通過單片機中斷方式的運行來延展更低的合成頻率。在分配到2KB的RAM的占用度時,就可獲得很高的頻率分辨率。另外,DAC的量化級數大于8位時,占用的RAM會成倍增加,而壓縮到N的取值范圍。總體上該裝置可輸出最高頻率約50KHz,最低1Hz的合成正弦波,尤其是采用了STM32F系列中具備DAC、DMA的芯片時。因為是采用單片機,而非專業的DDS模塊,所以在輸出波形的頻率上限值和頻帶范圍會有一定的限制。