基于FPGA 的極化碼交織器設計與實現

向明尚,張志華,潘麗艷

(東北石油大學,黑龍江 大慶 163318)

1 引言

Pοlar碼是基于信道極化現象提出的一種編碼方案[1],在設計時并沒有考慮碼距特性,而是利用了信道聯合與信道分裂的過程來選擇具體的編碼方案[2],是目前理論上證明唯一可以達到香濃極限[3]傳輸的信道編碼方案,已被3GPP選為5G eMBB場景控制信道編碼標準。

隨著5G技術逐步走向商用,在移動通信過程中對信息安全、可靠的傳輸要求越來越高。為保證信息的可靠傳輸,需要用到各種編碼技術來糾正信道中產生的隨機錯誤。當傳輸過程中產生突發性的干擾,用糾錯編碼理論和技術進行糾錯需要很長的碼字,增加了復雜度且延時較長。交織技術與糾錯編譯碼技術相結合,可以把突發錯誤離散成隨機錯誤,在隨機錯誤狀態進行譯碼糾錯,可取得良好的效果[4],使突發錯誤引起的碼字個數在規定的安全范圍內。交織編碼主要應用于有記憶信道,特別是無線信道,以此來糾正成串發生的比特差錯和一些突發錯誤[5]。發送端加上交織器,接收端接收到交織后的信息后,按照一定的規律進行解交織,即可還原信息。

極化碼具有很好的誤碼性能并且速率兼容性能優良[5],與交織器和解交織器配合,既可以糾正信道傳輸中的隨機錯誤,也可以糾正突發錯誤。交織與解交織過程是信道糾錯的一個非常重要環節,本文利用Altera公司開發的Quartus軟件仿真環境,基于FPGA設計實現了交織器電路。

2 交織模式的確定

交織是通信系統中進行數據處理而采用的一種技術,交織從其本質上來說是一種實現最大限度改變信息結構而不改變信息內容的技術[6]。極化碼采用統一的交織方法和結構,即給出了統一的交織模式,是根據交織器最大輸入信息比特數Kmax得到的,它是一種根據信道的狀態信息進行符號調整的自適應交織方法[7]。最大信息比特數包括傳輸的原始信息位和添加的CRC校驗位,共計164位,構成了循環冗余校驗碼,其中CRC校驗位為24位,添加在原始信息比特的后面。即發送信息中添加了冗余碼,使信息傳輸的開銷增大了,但卻可以進行差錯檢測和糾錯[8]。添加CRC校驗位長度為K的信息表示為:c0,c1,c2,c3,…,cK-1是加入到交織器的輸入序列,是經過交織器交織的輸出序列,它們之間滿足下列關系:是子交織模式。當輸入信息序列長度小于最大輸入信息比特數時,可以通過下列算法得到子交織模式。

當K的取值不同時,得到的子交織模式各不相同。例如K=50時,可以得到的一種子交織模式,如表1所示。其中m取值為0~49,是加入到交織器輸入序列共計50個信息比特的原始比特順序。Π的值也是0~49,但它是離散的,是經過交織器交織后輸出序列對應的信息比特順序。如m=9表示原始信息比特在輸入序列中的第9位上,與其對應Π=18,表示交織后原始信息比特在輸出序列中第18位上。

子交織模式如表1所示。當m≥29時,交織器輸出的信息比特順序與交織前信息比特順序一致,并沒有做交織處理。如果在這些連續的比特位傳輸過程中發生連續的突發性錯誤,是否會降低編碼的可靠性?回答是否定的。因為加入到交織器輸入序列的后24位是CRC校驗碼,可以得到修正。

表1 子交織模式(K=50)

3 交織器電路設計

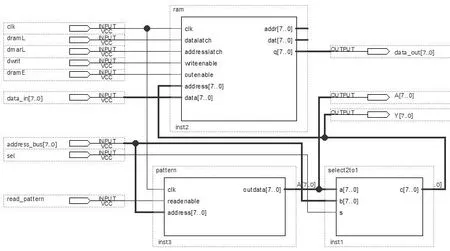

圖1 交織器設計原理圖

3.1 交織模式存儲器設計

交織模式存儲器設計利用ROM元件實現,地址線8位,數據線8位,存儲單元256個,每個單元可存儲一個8位二進制數。其中0~163連續的164個單元存儲交織模式數據它事先保存在數據文件中,作為存儲器配置文件在設計存儲器時提供。

數據文件的內容取決于輸入信息比特位數K,對應不同的子交織模式Π(k)。當K的值確定后,Π(k)及其數據文件都是固定不變且唯一,只能完成K個比特數據的交織工作,K變化時需要修改模式數據文件,并且需要重新配置模式存儲器,即可實現交織操作。

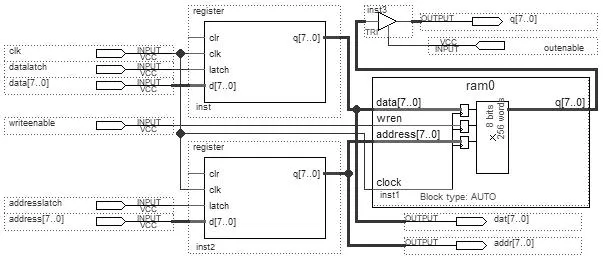

3.2 數據存儲器設計

數據存儲器設計,利用RAM元件實現,如圖2所示。

圖2 數據存儲器原理圖

地址線8位,數據線8位,存儲單元256個,每個單元可存儲一個8位的二進制數。其中,0~163連續164個單元,用于連續存儲加入到交織器的輸入序列,即等待交織的二進制信息比特數據,其長度K=164,即按照交織模式進行數據交織。

由于輸入的信息比特是二進制數,所以RAM的每個存儲單元只需保存1位二進制數據即可,也就是說其數據線只需要1位。而這里設計RAM時數據線用了8位,目的是在仿真測試時,可以使用十進制數0~163作為信息輸入,連續存入數據存儲器的存儲單元中,經過交織后輸出的是按交織模式離散的十進制數,方便觀察交織器的輸出情況,并與輸入序列作對比,有助于判斷交織器的工作是否正確。

3.3 數據選擇器設計

數據選擇器的設計利用硬件描述語言編程實現,完成地址二選一功能。在進行交織操作前,數據選擇器選擇連續地址0~163作為輸入,并按此順序輸出且作為地址提供給數據存儲器RAM,指向RAM連續的164個存儲單元。當需要交織輸出數據時,由交織模式存儲器輸出離散的模式數據,作為數據選擇器的輸入,經選擇器選中輸出且作為地址提供給數據存儲器RAM,指向RAM的對應存儲單元。

3.4 交織器工作流程

3.4.1 待交織數據的存儲實現

如圖1所示,加入到交織器等待交織的連續數據0~163,通過數據總線依次加到數據存儲器RAM的數據輸入端data_in,同時由地址總線address_bus依次給出連續的地址數據0~163,經過選擇器加到數據存儲器RAM的地址端,指向RAM連續的0~163個存儲單元,在寫信號和時鐘作用下,將待交織數據按信息比特順序存入數據存儲器RAM連續的存儲單元中。

3.4.2 交織過程的實現

由地址總線address_bus給出連續的地址0~163,加到模式存儲器pattern的地址輸入端,在讀信號和時鐘作用下讀出模式數據加入到數據選擇器。經選擇器輸出加到數據存儲器RAM的地址端,在讀信號和時鐘作用下讀出數據存儲器的數據,即可完成交織過程。

4 仿真結果分析

測試數據為0~163連續的十進制數據,作為輸入序列加入到交織器的數據輸入端,經交織器交織后輸出,通過輸出波形圖觀察驗證交織器的工作情況。

4.1 信息比特的輸入與存儲

等待交織的信息比特測試數據存入到交織器的數據存儲器中,這里用十進制數代表二進制信息比特,如圖3所示。圖3中add是0~163個連續的存儲器地址,add_latch為地址寄存器鎖存信號。

data_in為輸入的0~163個待交織的信息比特數據,data_latch為數據寄存器鎖存信號。data_write為寫信號,在時鐘信號clk配合下,將連續的待交織信息比特數據依次寫入數據存儲器0~163個存儲單元中。

圖3 交織器數據輸入波形圖

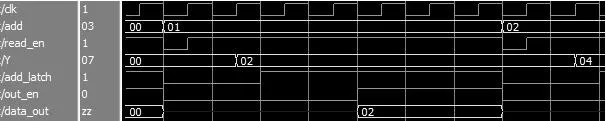

4.2 交織器輸出驗證

經過上一步操作,輸入信息比特數據已經寫入交織器數據存儲器,在此通過輸出操作來驗證數據存儲是否正確,如圖4所示。add為模式存儲器的連續地址0~163,read_en為模式存儲器讀出信號,Y為模式存儲器的輸出,即為交織模式的數據。果,也是交織模式的數據。

圖4 交織器交織結果輸出波形圖

Y的輸出數據是離散的交織模式數據,由add_latch信號鎖存,作為數據存儲器的地址,指向數據存儲器離散的存儲單元,當clk和οut_en信號有效時,data_οut輸出交織結

5 結語

交織器是極化碼編碼過程中的重要一環,它的質量直接影響到5G控制信道短碼傳輸效率。通過交織器電路的驗證,得到了與交織模式完全一樣的輸出序列信號,表明交織電路設計正確。交織器的設計方法及實現電路,可以滿足信息傳輸的可靠性和工作效率的要求。