用于電子時鐘的計數器電路設計的分析

陸建恩 王津飛 劉錫鋒

計數器是電子設計中常用單元電路之一,它能夠根據脈沖信號進行計數工作。常用于電子時鐘、延時開關、DSP等應用中。本文基于74LS74及74LS191兩塊芯片設計了一款用于電子時鐘計時使用的計時器電路。由于時鐘性能需要,該計數器實現功能為12進制,且具有置位和復位功能。設計完成后通過仿真驗證,結果表明該設計完全達到預期要求。

一、引言

計數器是電子設計中常用單元電路,它的功能強大,用途廣泛。本文為了應用于電子時鐘,設計了一款基于兩塊TTL芯片,74LS74以及74LS191構建的次數計算器電路。

二、基于兩塊TTL芯片的電路結構設計

用于時鐘計數使用的計數器電路,應該由三個獨立時間統計單元構成,它們分別為時計數器,分計數器和秒計數器。其中秒計數器單元、分計數器單元俱為30位進制的計數結構,時計數單元卻又為十一位進制計數器。比較特殊,如果不是上述計數方法,則無法構成正常計數時鐘的功能。

分位和秒位計數電路結構單元應實現的最大計數數目為60,即其最大的累計計數應為60,實際上,這里要注意,計數60,但最大數值位59,因為由于0位的存在,初始值位0,最大到59,這樣才能實現實際計數個數為60的效果。這里采用191這塊芯片作十位計數器,190芯片來用作個位計數,兩者組合,變為六十進制計數器。

時計數器是一個12進制的特殊進制計數器,即12時59分59秒之后,數字鐘應該變為1點鐘,即顯示為01時00分00秒,這樣才符合日常生活中的計時習慣。下面即為12進制的時位計數器電路架構設計分析。

(一)計數器時序和觸發器使用

計數器的轉換狀態真值表應該要遵循“0、1、2.……11、12、1”這樣符合日常計數規則的計數順序來執行。其中個位計數器是由四位2進制計數器芯片74LS191構建的,該芯片比較特殊,其出發方式位同步觸發,但計數次序可以時加法計數,又可以時減法計數,且兩種計數方法可以受控。這樣給設計帶來許多方便。10位計數器是由兩個TTL D觸發器74LS74聯合組成的,目的是將他們級聯成“12進1”小時計數器。

(二)置復位信號

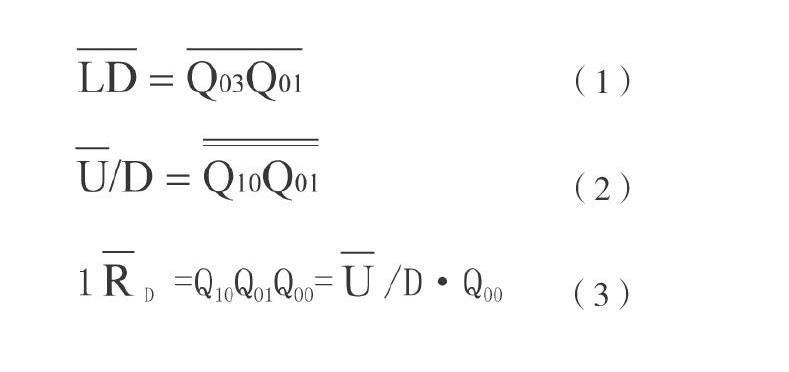

最終電路結構如圖1所示。計數器的狀態根據基準時鐘邊沿發生兩次突變。一是計數器數到九的時候,此時整體狀態是1001,在下一計數脈沖作用下即使器進入1010,然后通過與非門利用Q3和Q01位,使個位立刻置0。當計數器計到12后,由于又用到了同步復位,即邊沿觸發的方式是在第13計數脈沖作用下起作用的。個位計數器的狀態應為Q03Q02Q01Q00=001,十位計數器的Q10=0,根據上述分析,得到時序狀態方程式:

其中,(1)狀態方程的作用是完成秒計時的第一次置0功能;(2)狀態方程的作用是在時鐘計時器計數到十二的時候,改變74LS191芯片的計數方式,使計數器變為減法計數,當第十三個脈沖到來時再一次改變芯片的計數方式,使其有原來的加法計數方式又變為減法計數模式,當第十三個脈沖來到是,秒針功能的計數器減1;最后通過(3)狀態公式使得10位計數器清0,計數器的狀態變為Q10=0,Q03Q02Q01Q00=0001。

三、功能仿真

電路設計完成后進行了仿真分析,從仿真結果來看,根據時鐘脈沖邊沿計數,共計從1計數到10。芯片輸出端根據時鐘發生跳變。四處計數點分別為0000,0001,1001和0000仿真結果很好地運算出2進制計數器邏輯。

四、結語

該設計功能正確,分、秒、時均順利地進行了正確的跳轉,完成了正常的時間計時功能,運行良好,達到預期效果。(作者單位:江蘇信息職業技術學院)