基于FPGA的X射線熒光光譜儀數據采集與控制系統的設計

宋春苗 周超 胡學強

摘要:為提高X熒光光譜儀的準確性和測試靈敏度,本文基于FPGA設計了一套數據采集與控制系統,實現對X熒光光譜儀各個部件系統的控制,以及對探測系統輸出的信號及儀器所需的環境變量的實時采集,最終實現對被測樣品中元素種類及含量的分析。

關鍵詞:X熒光光譜儀;FPGA;數據采集與控制系統;被測樣品;分析

中圖分類號:TH741;TH842 文獻標識碼:A 文章編號:1007-9416(2020)01-0137-03

X射線熒光光譜儀是通過對樣品中不同元素中產生的熒光X射線能量(或波長)和強度進行分析,以獲得樣品中的元素種類與含量信息,達到定性和定量分析的目的。目前,X射線熒光光譜儀在地質、冶金、材料、環境、工業等無機分析領域中應用廣泛,尤其是在無損分析和原位分析方面,X射線熒光光譜儀具有無可替代的地位。

X射線熒光光譜儀由樣品交換系統、X射線發生系統、分光系統、探測系統、數據采集系統組成。其中樣品交換系統將樣品移動到測樣位置、X射線發生系統產生X射線激發樣品產生X射線熒光、分光系統將激發產生的X射線熒光篩選為待測元素的特征X射線熒光、探測系統將待測元素的特征X射線熒光的能量和強度轉變為電信號、數據采集系統對探測系統輸出的電信號及儀器所需的環境變量(流量、溫度、真空)進行實時采集上傳。數據采集與控制系統是X射線熒光光譜儀的關鍵部件,對儀器的測試準確性和測試靈敏度起著至關重要的作用。本文基于FPGA設計了一套適用于X射線熒光光譜儀的數據采集與控制系統,實現對樣品交換系統、X射線發生系統、分光系統、探測系統各部件節點的控制,同時對各元素特征X射線熒光的能量和強度進行實時采集處理及上傳,最終實現對被測樣品中元素種類及含量的分析。

1 系統的總體結構分析

本文所設計的X射線熒光光譜儀數據采集與控制系統以網絡通訊的方式與上位機進行交互,控制樣品交換系統將樣品移動到測樣位置,然后控制X射線發生系統產生X射線來激發樣品產生X射線熒光,同時控制分光系統對X射線熒光進行篩選,控制探測系統對篩選得到的特征X射線熒光進行光電轉換,采集流量、溫度、真空的實時狀態以及探測系統輸出的脈沖信號,最終以網絡通訊的方式傳輸到上位機進行實時顯示及分析,實現X射線熒光光譜儀對被測樣品元素種類和含量分析的功能。

本系統由通訊單元、控制單元及數據采集單元三大部分組成,其中通訊單元負責和上位機之間的信息傳遞,以及與X射線發生系統、溫控系統、流量系統之間的狀態交互;控制單元實現對樣品交換系統、X射線發生系統、分光系統、探測系統的實時控制;數據采集單元對探測系統輸出的有用信號及儀器所需的環境變量(流量、溫度、真空)進行實時采集。系統的總體結構如圖1所示。

2 硬件電路的設計

本系統采用FPGA作為主控制器構成控制單元,W5300與MAX3232配合構成通訊單元,數據采集單元采用AD公司的A/D轉換芯片實現對所需信號及狀態的采集。

2.1 通訊單元

系統的通訊單元包括網絡通訊和串口通訊兩部分,網絡通訊實現FPGA與上位機之間的信號傳輸,采用博控的W5300作為網絡通訊芯片該芯片內部集成10M/100M以太網控制器,MAC和TCP/IP協議棧,采用總線接口與控制器通訊,可以簡單快捷的實現高性能網絡數據傳輸,W5300芯片與FPGA采用并口連接,25M外部晶振時鐘信號通過W5300的內部鎖相環倍頻到150M作為W5300的內核工作時鐘。串口通訊實現FPGA與X射線發生系統、溫控系統、流量系統之間的信息交互,這里采用3片MAX3232實現,MAX3232芯片可實現TTL電平與RS232電平之間的雙向轉換。

2.2 控制單元

系統的控制單元由Altera公司的CycloneⅢ系列的FPGA芯片EP3C16F484實現,該芯片具有豐富的可配置邏輯單元(CLB)以及可編程輸入輸出單元(IOB),可以實現X射線熒光光譜儀的各個部件系統的高速并行數字化控制,其硬件配置電路圖如圖3所示,采用JTAG的方式加載硬件程序,設置FPGA的MSEL0、MSEL2、MSEL3管腳為低電平,MSEL1管腳為高電平。

2.3 數據采集單元

系統的數據采集單元包括對探測系統輸出的有用信號的采集及對儀器所需的環境變量(流量、溫度、真空)的實時采集兩個部分。由于探測系統輸出的脈沖信號上升時間為250ns,為保證采樣信號不失真,根據奈奎斯特采樣定理,采樣頻率應大于兩倍被采樣信號的最高頻率,本文選取AD公司的模數轉換芯片AD9255,其采樣速率高達125MSPS,精度為14位,可以實現探測系統輸出脈沖的高速高精度數字化,由于環境變量變化緩慢,采樣精度要求高,故選取AD公司的模數轉換芯片AD976,其采樣速率為200KSPS,精度為16位,可以滿足系統要求,其硬件接口電路圖如圖2所示,AD976與FPGA采用并口方式連接,參考電壓REF為10V。

3 數字邏輯的設計

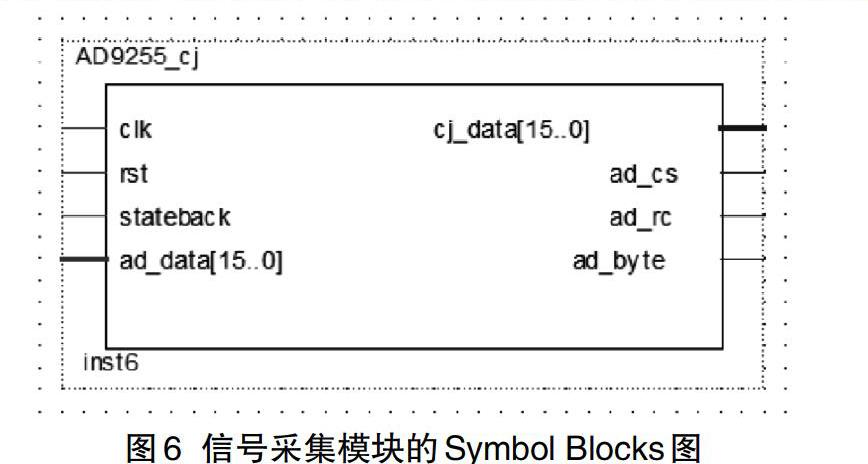

本文采用QuartusⅡ軟件進行自頂向下的模塊化設計,根據系統需求,劃分為時鐘發生模塊,系統復位模塊,網絡通信模塊,數據轉換模塊,系統控制模塊,信號采集模塊,以及狀態采集模塊。系統的邏輯結構圖如圖3所示。

3.1 時鐘發生模塊

時鐘發生模塊將外部晶振輸入的50M時鐘信號通過鎖相環輸出系統的標準時鐘以驅動系統的所有模塊,同時將系統時鐘根據需求的不同分頻產生不同頻率的時鐘信號輸出到系統的各個模塊以滿足需求,時鐘發生模塊的Symbol Blocks如圖4所示。

3.2 網絡通信模塊

網絡通信模塊通過配置W5300實現UDP協議的網絡通信,UDP是一種無連接的傳輸協議,資源消耗小,傳輸數據快,其通訊流程如圖5所示。