數字鐘電子設計研究

梁可 常楠 郭磊 段昭烈

摘 要:本設計是采用數字電路技術實現基本時鐘功能時、分、秒,并能進行整點報時和校準的制作。數字鐘適用于家庭鐘設計,倒計時裝置設計,也適用于各種電氣設備和其他醫療設備上。為達到鞏固數字電路與模擬電路的學習知識并實際運用的效果,本設計主要采用中小型規模集成電路設計數字鐘電路。

關鍵詞:數字鐘;譯碼計數;數字電路

1前言

數字鐘常用于人們的生活中,能在跑步時計時,能在手表上報時,能在鬧鐘響鈴。人們生活中無處不在,它能具象出時間的流逝,使人們生活更加高效。

1.1設計背景

數字鐘是一種用簡單數字電路技術可實現的電子設計,僅用簡易的電子元器件便可實現準點報時,計數等要求。

1.2設計目標

本設計主要是利用如計數器、觸發器、與門、異或門等數字邏輯器件,將脈沖進行計數,并用6位數碼管顯示出來,其主要功能是能較精確的進行時間顯示和時間校準,并實現整點報時的附加功能,具體設計要求:

(1)產生的秒脈沖頻率精確;

(2)可完成整點報時功能;

(3)數碼管顯示時間準確,可實現校準功能。

1.3必備條件

要求使用晶體振蕩器產生頻率為1Hz的時鐘基準信號電路,電路秒信號發生器由CD4060和CD4013組成。它與電容、電阻、石英晶體等元器件共同組成32768Hz振蕩器,后進行14級二分頻,[2]再采用D觸發器(CD4013)進行二分頻,輸出1Hz的時秒信號。通過數字邏輯運算,采用74LS390計數,經七段顯示譯碼器CD4511直接驅動LED數碼管顯示對應時間,并能通過單刀雙擲開關對時鐘進行校時,在整點時蜂鳴器進行報時。

1.4方案比較

1.4.1方案一

通過1個NE555定時器與多個電阻和電容組成多諧振蕩器,輸出頻率為1kHz的信號,再經分頻器74F160產生1Hz時鐘脈沖所需的頻率,(或經過3個74LS90級聯而成的千分頻器產生1Hz脈沖)提供給計數單元,并通過譯碼驅動在數碼管上顯示出來。[1]采用NE555芯片組成的多諧振蕩器可輸出符合要求的頻率脈沖,其計算可由公式得:

計算得:

通過計算結果與仿真當R2調整為10kΩ左右時,輸出頻率更加接近于1KHz。

1.4.2方案二

通過集成邏輯門7401與非門與RC組成時鐘源振蕩器,可產生脈沖信號。

1.4.3方案三

對發出的秒沖信號進行設計,采用32768Hz的晶體振蕩器和外接電阻、電容、石英晶體共同組成振蕩器,通過CD4060并進行14級二分頻,再經D觸發器(CD4013)進行二分頻,輸出1Hz的秒信號。

1.5方案論證

方案一NE555構成的多諧振蕩器難以準確輸出1KHz的頻率脈沖,可能時鐘不準確,同時其對電阻和電容的精度要求較高。不易輸出符合要求的頻率脈沖。

方案二采用RC組成的振蕩電路,不僅與時間常數τ相關,還取決于閾值電壓VTH,兩者均易受電源電壓,溫度等因素干擾,因此頻率穩定性差。故不采用此方案。

方案三采用石英晶振產生脈沖信號,有著輸出頻率準確,不易干擾的優點。

1.6方案選擇

由于數字鐘電路的設計,注重時鐘顯示的準確度,精準的時間是數字鐘的核心,因此采用32768石英振蕩器穩定輸出32768Hz(215)脈沖,再經CD4060進行14分頻計數再外加級D觸發器(CD4013)二分頻,輸出1Hz的時基秒信號。可輸出1Hz脈沖,因此采用方案三準確輸出1Hz脈沖,提高了方案的準確性。

2各單元模塊功能介紹及電路設計

數字鐘設計主要含有5個單元模塊,它們分別是:1Hz時鐘信號模塊、60進制和24進制計數器模塊、譯碼驅動數碼管顯示模塊、校時模塊和整點報時模塊。

2.11Hz時鐘信號模塊設計

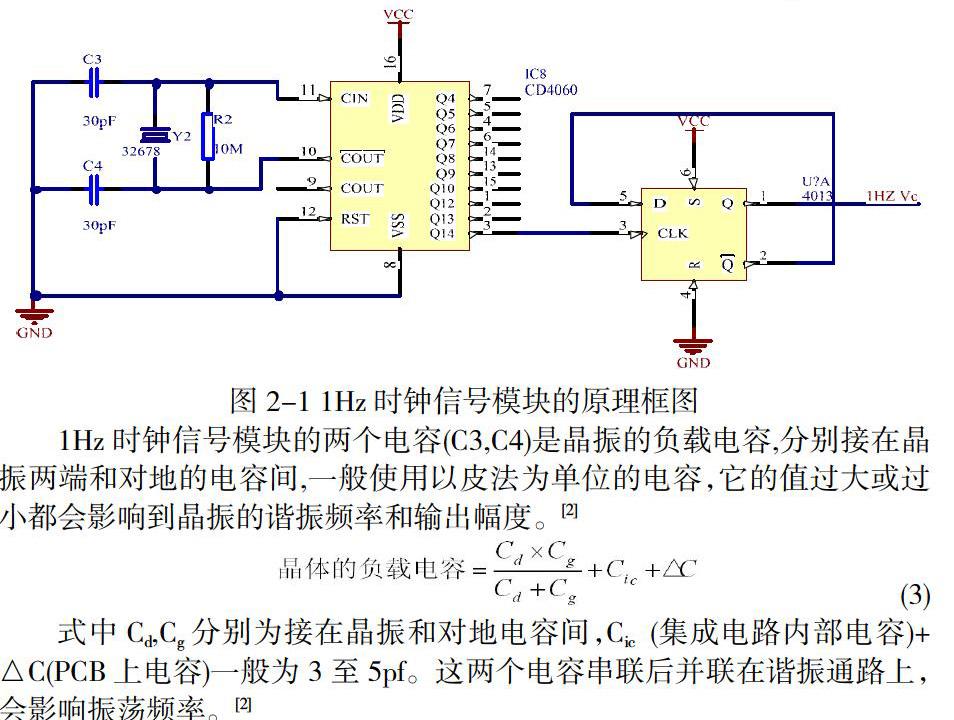

該模塊因無法一次性直接產生1Hz的低信號脈沖,因此采用石英晶體振蕩電路,它與CD4060組成32768Hz(215)振蕩器,再外加D觸發器(CD4013)二分頻,因此采用了14級二分頻,輸出1Hz的時脈沖信號。

1Hz時鐘信號模塊的兩個電容(C3,C4)是晶振的負載電容,分別接在晶振兩端和對地的電容間,一般使用以皮法為單位的電容,它的值過大或過小都會影響到晶振的諧振頻率和輸出幅度。[2]

式中Cd,Cg分別為接在晶振和對地電容間,Cic(集成電路內部電容)+△C(PCB上電容)一般為3至5pf。這兩個電容串聯后并聯在諧振通路上,會影響振蕩頻率。[2]

2.2計數模塊設計

數字鐘的分鐘和秒鐘計時電路要設計為60進制計數器是分鐘和秒鐘計時電路,為減少器件使用量,分別用兩個74LS390芯片構成60進制計數器。將兩芯片的個位芯片接成十進制計數器,而將十位計數單元將10進制計數器轉換為6進制計數器。

(1)60進制計數器

60進制計數器:在計數部分,采用74LS390芯片構成60進制計數器,將其中一片74LS390設計成10進制計數器,另一片設計成6進制計數器。兩片74LS390按反饋清零法串聯而成。秒計數器兼具60清零和進位的功能,因此輸出脈沖進行清零外,同時還作為分計數器的輸入脈沖CP1。分秒計數器基本功能相同,因此此可作為秒計數器的同時,也可作為分計數器。[1]

秒與分鐘十位計數器應為6進制計數器,為使芯片構成更加簡單,采用相同的器件,對進制進行接線改制。采用將10進制計數器轉換為6進制計數器的電路連接方法,分個位與十位基本一致。

(2)24進制計數器

數字鐘中各位計數器功能基本相同,但小時的整體計數應為24進制計數器,運用反饋清零法,將兩個74LS390級聯,接成模100計數器,其中U11構成十位計數器和U12構成個位計數器,在此基礎上,借助與門譯碼和計數器譯碼清零的功能,將U11的Q2端和U12的Q1端接在與門的輸入端。工作時,在第24個脈沖作用后,十位數計數器輸出為0010,個位數計數器輸出為0100,經與門后,兩者在計數器U11和U12的清零端CR使其返回0狀態,形成24進制計數器。

2.3譯碼驅動顯示模塊設計

譯碼器對計數器的輸出值進行譯碼,得到數碼管顯示數據,用于驅動七段數碼管的譯碼器常用的有CD4511,在本設計中用于驅動LED驅動共陰極顯示數碼管。將其與七段數碼管連接即可完成不同數字的顯示,數碼管dp端為小數點端,在本設計暫不使用,因此接地。

2.4校時模塊設計

校時模塊可暫時先采用單獨的脈沖接入計數器的輸入端進行調試。

(1)外接開關S1。

(2)選擇蜂鳴器為發聲器件。

在校時模塊外加入整點報時功能,即在時間出現整點時,數字鐘會自動發聲,采用555芯片輸出穩定電平通過蜂鳴器后,可以使人聽到,達到準點報時目的。

3系統調試

采用Proteus軟件對計數模塊、譯碼器驅動模塊、七段譯碼顯示模塊、脈沖發生器、校時模塊進行了仿真,達到了目的。

3.1硬件調試

在數字鐘硬件調試中,利用Proteus對計數驅動顯示模塊、校時模塊和頻率發生模塊分別進行了仿真。通過控制單刀雙擲開關SW1作為開啟端,SW2、SW3、SW4作為校時端,因為信號的精確性和穩定性不可能做到分毫不差,因此電路中需要校準時間功能的電路,人為地調整時間的誤差。每搬動一次單刀雙擲開關產生一個計數脈沖,實現校時功能。

在總模塊分秒計數部分均實現了60進制顯示,時計數部分實現24進制清0顯示,校時部分搬動單刀雙擲開關一次即可調整時間。

4結論

本文從設計的電路應用數字電路計數器、555多諧振蕩電路、32768Hz晶振與分頻器產生1Hz脈沖功能。在電路設計中為節約電路設計成本,采用一片74LS390可完成兩片其他計數器的技術功能。

參考文獻:

[1] 康華光,電子技術基礎-數字部分[M].高等教育出版社,2014.

[2]徐紅霞,數字鐘電路的設計[J].廣東技術師范學院學報,2008(03):17-20.

作者簡介:

梁可(1998—),女,漢族,四川成都,本科,研究方向:電氣工程及其自動化。

常楠(1998—),女,漢族,河北唐山,本科,研究方向:電氣工程及其自動化。

郭磊(1997—),男,漢族,四川仁壽,本科,研究方向:單片機開發、自動化。

段昭烈(1999—),男,漢族,四川廣安,本科,研究方向:單片機開發、自動化。