鐵電負電容場效應晶體管研究進展*

陳俊東 韓偉華 ? 楊沖 趙曉松 郭仰巖 張曉迪 楊富華?

1) (中國科學院半導體研究所,半導體集成技術工程研究中心,北京市半導體微納集成工程技術研究中心,北京 100083)

2) (中國科學院大學,材料與光電研究中心,北京 100049)

鐵電負電容場效應晶體管可以突破傳統金屬氧化物半導體場效應晶體管中的玻爾茲曼限制,將亞閾值擺幅降低到60 mV/dec以下,極大地改善了晶體管的開關電流比和短溝道效應,有效地降低了器件的功耗,為實現晶體管特征尺寸的減小和摩爾定律的延續提供了選擇.本文分析總結了國內外近年來關于鐵電負電容場效應晶體管代表性的研究進展,為進一步研究提供參考.首先介紹了鐵電負電容場效應晶體管的研究背景及其意義;然后總結了鐵電材料的基本性質和種類,并對鐵電材料負電容的物理機制和鐵電負電容場效應晶體管的工作原理進行了討論;接下來從器件溝道材料維度的角度,分別總結了最近幾年基于三維溝道材料和二維溝道材料且與氧化鉿基鐵電體結合的鐵電負電容場效應晶體管的研究成果,并對器件的亞閾值擺幅、開關電流比、回滯電壓和漏電流等性能的改善進行了分析概述;最后對鐵電負電容場效應晶體管目前存在的問題和未來的發展方向作了總結與展望.

1 引 言

1965 年,Moore[1]提出摩爾定律,即每過 18 個月,集成電路芯片上集成的晶體管數量增長一倍,晶體管的特征尺寸減小為上一代的0.7倍.半個世紀以來,隨著半導體技術的快速發展,晶體管的特征尺寸大幅度減小.2002 年,金屬-氧化物半導體場效應晶體管(metal-oxide-semiconductor fieldeffect transistors,MOSFETs)的尺寸進入了100 nm節點[2],但僅僅通過縮小溝道尺寸帶來的性能提升已經不能滿足市場對MOSFETs的要求,因此需要引入新的材料和結構來提升MOSFETs的性能.在90 nm節點的時候引入了應力硅技術[3],使得溝道中載流子的遷移率得到了提高.為了抑制SiO2氧化介質層減薄導致的漏電流,在45 nm節點引入了高k介質層以及金屬柵工藝,MOSFETs的性能得到了極大的提升.但隨著MOSFETs尺寸達到22 nm節點,傳統體硅平面結構MOSFETs的問題變得嚴重,短溝道效應導致的漏電流和亞閾值擺幅 (subthreshold swing,SS)退化現象使得器件的功耗急劇上升,因此人們開始考慮采用新型結構器件.其中,絕緣體上硅[4](silicon on insulator,SOI)、超薄絕緣體上硅[5](ultra thin body-SOI,UTB-SOI)和三柵鰭式晶體管[6](FinFET)等結構的利用在很大程度上緩解了由于短溝道效應帶來的諸多問題.文獻 [7]中指出,在 3 nm 節點,MOSFETs 采用環柵結構 (gate all around,GAA)以提高柵對溝道的控制能力,其性能相較于目前主流的FinFET將提高30%以上.

但隨著晶體管特征尺寸進入10 nm以內,由于短溝道效應和漏致勢壘降低(drain induced barrier lowering,DIBL) 效應造成的亞閾值區性能退化現象已變得不可忽略,器件的SS增大,因而其閾值電壓Vth和工作電壓VDD不能等比例減小,這導致器件的靜態功耗急劇增大,成為阻止器件尺寸進一步縮小的主要因素.2017年的國際器件與系 統 路 線 圖 (international roadmap for devices and systems,IRDS) (圖1)[8]指出,由于對高集成度低功耗器件的需求,到2033年,晶體管的特征尺寸將縮小到2 nm,其SS也將降低到40 mV/dec.而對于傳統MOSFETs,由于載流子玻爾茲曼分布的[9]限制,室溫下的SS無法降低到60 mV/dec以下,因此探尋降低晶體管的SS的方法,對于促進晶體管特征尺寸的進一步減小具有重要的意義.

圖1 IRDS 提出的 SS 路線圖[8]Fig.1.Roadmap of subthreshold swing (SS) proposed by IRDS[8].

目前一類器件是通過改變器件載流子的運輸機制來降低SS,主要包括隧穿晶體管[10?13]、雪崩晶體管[14]和納機電原理晶體管[15?17]等.這一類器件都可以將SS降低到60 mV/dec以下,但是都面臨著相應的技術上的問題.其中隧穿晶體管的電子隧穿概率低導致器件工作電流小和源漏之間的非對稱工作特性是其面臨的主要問題[18];雪崩晶體管的雪崩擊穿電壓高,不利于器件系統的穩定性[19];納機電原理晶體管的制作工藝復雜,開關速度慢[20],因此這一類器件目前仍停留在實驗室研究階段.另外一類器件是通過調節柵介質層電容和溝道電容的電容匹配來降低SS,如超薄體硅SOI晶體管[21]、無結納米線晶體管[22,23],但這類器件本質上還是傳統MOSFETs,其室溫SS仍然無法突破60 mV/dec的物理限制.

鐵電負電容場效應晶體管(ferroelectric negative capacitance field effect transistors,Fe-NCFETs)一種新興的晶體管,其概念最早由Salahuddin和Datta[24]于2008年提出,他們提出將傳統MOSFETs的柵極氧化介質層替換成鐵電材料介質層,放大柵壓對溝道的作用效果,降低柵電容與溝道電容的比值,原理上可以把晶體管的SS降低到60 mV/dec以下,這種現象他們稱之為負電容 (negative capacitance,NC)效應.與其他降低晶體管 SS 的方法相比,Fe-NCFETs有著明顯的優勢.由于Fe-NCFETs僅是在MOSFETs柵介質層中引入了鐵電材料,其總電容等效為NC,本質上并沒有改變金屬-氧化物半導體 (metal oxide semiconductor,MOS)器件的工作機制,晶體管結構上也沒有太大的變化,因此Fe-NCFETs保持了傳統MOS器件高驅動電流的優點,而且還具有與互補金屬氧化物半導體(complementary metal oxide semiconductor,CMOS)工藝兼容、對稱的源漏工作機制、低功耗和負DIBL效應等優點[25,26],使Fe-NCFETs成為未來小尺寸、低功耗MOS器件中極具潛力的一種選擇.研究人員也因此對Fe-NCFETs進行了廣泛的研究,各種新材料[27?30]、新結構[31?34]和新技術[35?38]不斷被提出,Fe-NCFETs的性能也得到了極大提升.

本文從器件溝道材料維度的角度,總結國內外最近幾年關于Fe-NCFETs理論和實驗的重要研究進展,并對器件的SS、開關電流比、回滯電壓和漏電流等性能的改善進行分析概述.第二部分首先介紹鐵電材料的基本性質,然后對鐵電材料的種類進行總結.其中氧化鉿基鐵電材料的發明,解決了傳統鐵電材料與CMOS工藝的兼容問題,使得Fe-NCFETs的性能進一步提高.第三部分首先對MFS、MFIS和MFMIS結構Fe-NCFETs的優缺點作簡要總結;然后從原子微觀受力出發,推導出鐵電材料的“S”關系曲線,并結合吉布斯自由能公式和 Landau-Khalatnikov (L-K)方程,得到鐵電材料自由能曲線中的本征NC區域,接下來從概念和電路特點方面分別討論鐵電電容中穩態NC和瞬態NC;最后討論NC Fe-NCFETs的工作區域.第四部分從三維溝道材料和二維溝道材料角度總結近幾年來采用氧化鉿基鐵電體的Fe-NCFETs的重要研究成果.其中采用硅、鍺基材料、III-V族化合物和碳納米管等三維溝道材料的Fe-NCFETs與傳統CMOS工藝的兼容性高,溝道與鐵電層之間界面性能好,電學性能穩定.但是,也存在一些問題,比如硅材料的載流子有效遷移率低限制了晶體管開態電流的大小,鍺基材料的帶隙較小導致開關電流比小,III-V族化合物材料與介質層之間的界面性能差以及碳納米管Fe-NCFETs的工作機理尚未探索清楚等.而與過渡金屬硫族化物、石墨烯和黑磷等二維材料相結合的Fe-NCFETs為晶體管特征尺寸進入3 nm提供了可能,二維材料一些獨特的物理效應也極具應用潛力.但是二維材料與柵介質層的界面性能較差,溝道表面缺陷態較多,而且二維材料與傳統CMOS工藝兼容性較差.因此,需要尋找新型材料和新的設計方案,以在這些條件之間尋找一個平衡,來滿足未來器件對溝道材料的要求.最后對Fe-NCFETs目前存在的問題和未來的發展方向作總結與展望.

2 鐵電材料基本性質與分類

2.1 鐵電材料基本性質

在一定溫度范圍內,某些晶體會在特定方向上產生自發極化,使晶胞中的正負電荷中心沿該方向產生相對位移,形成電偶極矩,且自發極化的大小和方向會隨著外界電場的大小和方向的改變而改變,具有這種特性的晶體稱為鐵電體(ferroelectrics).其中,極化方向與晶體的其他任何方向都不是對稱等效的,也就是在晶體所屬點群的任何對稱操作下都保持不動的方向,稱這個方向為特殊極性方向.而在 32 個晶體學點群中,只有 1(C1)、2(C2)、m(C3)、mm2(C2v)、 3(C3)、 3m(C3v)、 4(C4)、 4mm(C4v)、6(C6)和6mm(C6v)這10個點群具有特殊極性方向[39].即只有屬于這10個點群的晶體,才有可能發生自發極化,也才有可能是鐵電體,圖2給出了32個晶體學點群所包含的電介質材料所屬點群之間的關系[39,40].

圖2 介電體分類示意圖Fig.2.The schematic diagram of the classification of dielectrics.

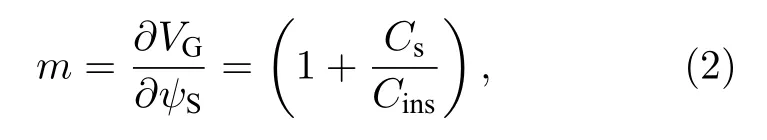

鐵電材料在宏觀上具有居里溫度和電滯回線兩個主要特征.圖3為鐵電材料極化強度P和外加電場E之間的典型關系圖,即電滯回線[41].其中,Pr為剩余極化強度,表示撤去外電場時材料剩余的極化強度;Ec為矯頑電場,表示使極化強度為零時的電場強度.當鐵電體位于初始狀態時,內部的電偶極矩方向隨機排列,鐵電體的凈極化強度為零(點1).當施加外加電場時,電偶極矩開始沿著電場方向排列(點1到點3).當全部的電偶極矩方向與電場方向一致時,鐵電體的極化強度達到最大值.隨后撤去外電場,由于電偶極矩之間的相互耦合,鐵電體內部存在剩余極化,極化強度為Pr(點4).當施加反向電場時,電偶極矩開始反轉.當施加電場強度達到?Ec時,鐵電體內部的電偶極矩方向隨機排列,此時凈極化強度為零(點5).繼續增大電場強度,極化強度將在反方向上達到最大值(點6).

圖3 鐵電電滯回線[41]Fig.3.Ferroelectric hysteresis loop[41].

因為晶體的構型是溫度的函數,所以晶體的極化狀態將隨溫度的變化而變化[42].對于鐵電體來說,存在一個臨界溫度Tc,當溫度低于Tc時,晶體結構為有自發極化的鐵電體結構;當溫度高于Tc時,晶體結構轉變為沒有自發極化的順電體(paraelectrics)結構,稱Tc為居里溫度.以 BaTiO3為例,其居里溫度Tc為 130 ℃,當溫度T>130 ℃時,晶格結構為立方晶系(m3m),此時晶體是順電體,不具有自發極化;當 0 自1921年Valasek[46]發現羅息鹽(酒石酸鉀鈉,NaKC4H4O6·4 H2O)晶體具有鐵電電滯回線以來,到目前為止,人們已經發現1000多種具有鐵電性的材料,按照材料組成大致可分為傳統無機鐵電材料、有機鐵電材料、范德華類層狀二維鐵電材料和氧化鉿基鐵電材料四類. 2.2.1 傳統無機鐵電材料 傳統無機鐵電材料包括: 鈣鈦礦型鐵電體如BaTiO3、PbTiO3、PbTiZrO3和 KNbO3等,酸鋰型鐵電體如 LiNbO3、LiTaO3和 BiFeO3等,青銅礦型鐵電體如PbTa2O6、PbNb2O6和Ba2Sr3Nb10O30等,鉍層狀鈣鈦礦結構鐵電體如SrBi2Ta2O9,其鐵電性來源于晶格結構的不對稱性.這一類材料具有居里溫度點高、抗疲勞特性優異和自發極化強度大等優點,所以最開始被應用于基于極化反轉特性的鐵電存儲器研究領域,但是其薄膜沉積溫度高(一般大于800 ℃)、電滯回線矩形度差以及與CMOS工藝兼容性差等缺點也阻礙了其商業化進程[39]. 2.2.2 有機鐵電材料 有機鐵電材料包括聚偏氟乙烯(Polyvinylidene fluoride,PVDF)及其衍生物[47?50]、奇數尼龍[39](如尼龍–11、尼龍–9 等)、金屬-有機混合物鐵電材料[51,52]和鐵電液晶(癸氧基芐叉對氨二甲丁基肉硅酸鹽[39]、溴化膽固醇及其衍生物[53]等)等,其鐵電性的物理機制是材料含有的手性有機物分子基團導致了材料分子的不對稱性,從而表現出自發極化的特性.有機鐵電材料的沉積溫度低(一般在200—300 ℃ 左右),與襯底無化學反應,因此可以在各種半導體材料上兼容生長,而且還具有延展性好、生物兼容、去極化場小、穩定性高、光化學響應速度快和衍生物種類豐富等優點[28],因此吸引了研究人員的廣泛關注,并對有機鐵電材料在存儲器[49]、晶體管[50,54]和電光顯示等[55]方面的應用以及新型有機鐵電材料的開發[56,57]進行了大量的研究,而提高自發極化強度和居里溫度是目前有機鐵電材料主要研究方向. 文獻[56]中報道了新型有機鈣鈦礦鐵電材料,如圖4所示,采用手性有機分子基團、NH4+離子和鹵族負離子 (Cl–,Br–,I–)分別替代了傳統鈣鈦ABO3中的 A3+離子,B3+離子和 O2–離子,合成了結構式為A(NH4)X3的一大類共計23種全有機新型鈣鈦礦材料.其中共有17種材料顯示出了良好的鐵電性,尤其是發現的 MDABCO-NH4I3,其自發極化強度 (Ps)為 22 μC/cm2,已接近無機鈣鈦礦鐵電體 BaTiO3的極化強度 (26 μC/cm2),其居里溫度Tc高達 175 ℃,比 BaTiO3的居里溫度(117 ℃)高出 50 ℃以上,在新一代柔性可穿戴器件和生物電子學方面具有極高的應用潛力. 2.2.3 范德華類層狀二維鐵電材料 近幾年來,人們發現范德華類層狀二維材料具有鐵電性.Li和Wu[58]通過第一性原理計算,證明二維AB型層狀堆疊材料(BN、AlN、ZnO、MoS2、GaSe等)由于層間的電子轉移導致其在垂直方向上具有鐵電性.Ding等[59]也通過第一性原理計算從理論上證明了二維In2Se3具有水平方向和垂直方向的自發極化,而且其自發極化方向可以通過外部電場調控[60],為調控鐵電材料的極化方向提供了新方法.Liu等[61]通過在硅上沉積了一層厚度為4 nm的范德華類二維CuInP2S6薄膜制備了二極管,在50 ℃下觀察到了材料的鐵電性能,而且器件的開關電流比約為100,表現出了較好的存儲性能.這一類材料由于只需要幾個分子薄層就能表現出鐵電性能,對于實現鐵電器件尺寸的進一步縮小是很有吸引力的.但是其居里溫度低,而且鐵電性的物理機制尚未研究清楚,關于材料鐵電性的實驗證明也相對較少,所以這一類材料仍需要進行大量的研究工作[62]. 圖4 有機鈣鈦礦 A(NH4)X3家族化學和晶格結構[56] (a) 有機鈣鈦礦鐵電體的三維化學結構組成圖;(b) 鐵電相 MDABCONH4I3在293 K時的晶胞結構圖,右側橢圓中為有機正離子的空間結構示意圖,其對稱性接近于球體;(c) 鐵電相MDABCONH4I3在463 K時的晶胞結構圖Fig.4.Chemical and crystal structures of the metal-free A(NH4) X3 family[56]: (a) Chemical structures of constituents of the metalfree 3D perovskite ferroelectrics;(b) the packing diagram of MDABCO–NH4I3 in the ferroelectric phase at 293 K.The oval to the right contains the space-fill diagram of the organic cation,showing the cationic geometry to be close to a ball;(c) the packing diagram of MDABCO–NH4I3 in the paraelectric phase at 463 K. 2.2.4 氧化鉿基鐵電材料 氧化鉿基鐵電材料是一類新型的鐵電材料,自 2011年 B?scke等[63]發現 Si摻雜的 HfO2薄膜具有鐵電性以來,人們又陸續發現摻雜Al[64]、Y[65,66]、Gd[67]、La[67]、Sr[68]等元素的 HfO2 也顯示出了顯著的鐵電性,而且,B?scke 等[63]還發現在HfO2中摻入ZrO2形成的薄膜表現出了優異的鐵電性能[69,70].本征HfO2常見的三種晶體結構[71]分別是: 單斜相-c(T<1727 ℃)、非極性四方相-nmc(1717 ℃ Fe-NCFETs作為一種新型低功耗器件,通過在傳統的MOSFETs柵介質層中引入鐵電材料將SS降低到 60 mV/dec以下 (圖5).SS是描述器件開關性能的重要參數,定義為源漏電流每改變一個數量級所帶來的柵壓改變量.SS數值越小,表示柵對溝道的控制能力越強,即器件的開關性能越好,同時可以在較小的柵壓下得到相同的電流,降低器件的功耗.SS的表達式為 其中VG為柵壓,ID為源漏電流,ψS為溝道表面電勢;m=?VG/?ψS稱為體因子,表示柵壓對溝道表面電勢的控制能力,取決于溝道電容與柵介質層電容的比值大小;n=?ψS/?log10ID稱為傳輸因子,表示溝道表面電勢對源漏電流的控制能力,取決于載流子的傳輸機制. 圖5 場效應晶體管轉移特性曲線Fig.5.The transfer characteristic curve of field effect transistors. 傳統MOSFETs的器件結構圖和電容模型如圖6所示[24],利用圖中的等效電容模型,可以將m表示為 其中Cins為介質層電容,Cs為溝道電容.對于常規MOS 器件來說,Cins和Cs均為正值,所以m取值總是大于1.另一方面,由于MOS器件溝道中載流子的輸運機制是漂移擴散原理,會受到載流子玻爾茲曼分布的限制,導致n存在一個理論最小值,即 其中kB為玻爾茲曼常數,T為溫度,q為單位電荷. 圖6 標準場效應晶體管結構示意圖與其等效電容電路[73]Fig.6.The schematic diagram of a standard field effect transistors.structure and its eauivalent circuit of capacitance[73]. 因此傳統 MOSFETs室溫 (T=300 K)下的 SS的理論最小值為 60 mV/dec,而對于 Fe-NCFETs來說,由于柵介質層中的鐵電材料具有NC效應,因此柵介質層電容可以為負值,即 所以m的數值可以小于 1,則 SS可以突破60 mV/dec的限制,但同時為了保證器件運行的穩定性,需要滿足m>0,即 因此,通過合理設計器件的電容,可以實現SS低且穩定性好的低功耗高性能Fe-NCFETs器件,而且由于柵介質層電容與漏端電容的耦合作用,器件具有負DIBL和負微分電阻(negative differential resistance,NDR) 效應[25],改善了短溝道效應,對于晶體管尺寸的減小是很有利的. 對 MFS、MFIS和 MFMIS結構 Fe-NCFETs的優缺點作簡要總結;然后從原子微觀受力出發,推導出鐵電材料的“S”關系曲線,并結合吉布斯自由能公式和L-K方程,得到鐵電材料自由能曲線中的本征NC區域;接下來從概念和電路特點方面分別討論鐵電電容中穩態NC和瞬態NC;最后討論NC Fe-NCFETs的工作區域. 2008 年,Salahuddin 和 Datta[24]首先提出利用鐵電材料替換傳統晶體管的柵介質材料,可以將器件的柵電壓放大,從而理論上可以降低器件的SS,這種器件結構稱為MFS(圖7(a)),具有結構簡單的優點,但是鐵電層與溝道之間的界面不兼容性問題嚴重,器件的界面性能差.隨后人們提出在鐵電層和溝道之間加入一層傳統柵介質層,即MFIS結構(圖7(b)),這種結構很好地解決了鐵電層與溝道之間的界面問題,但由于溝道的表面電勢在源漏之間有變化,而鐵電層上表面電勢分布是均勻的,從而導致鐵電材料在溝道方向上電壓放大效果不一樣[74?79].因此,有人提出在柵介質層和鐵電層之間加入一層金屬,即MFMIS結構(圖7(c)),以此來均勻鐵電層在溝道方向上的電勢放大效果,但內部金屬柵電極的存在極大地增加了器件的制造難度,對于器件尺寸的進一步減小是不利的,而且會導致柵極漏電流的增加,降低了器件的穩定性能[80?82].相 比 于 MFMIS 結 構,MFIS 結 構 Fe-NCFETs的電容匹配更穩定,將更適用于高頻邏輯應用[83]. 因此,MFIS結構仍是未來Fe-NCFETs的主要選擇,而且隨著氧化鉿基鐵電材料的提出,通過熱氧即可在氧化鉿和硅之間形成一層薄氧化硅介質層,改善了MFIS結構中鐵電層與溝道的界面性能差的問題,同時還引入高k材料介質層的優點[84],進一步優化了器件的性能. 圖7 器件結構圖 (a) 傳統 MOSFETs;(b) MFIS;(c) MFMISFig.7.Device structure diagram: (a) Traditional MOSFETs;(b) MFIS;(c) MFMIS. 3.2.1 穩態 NC 鐵電材料NC來源于晶格不對稱性導致的自發極化,之前人們采用吉布斯自由能理論,結合鐵電材料的電滯回線和相關物理參數,分析證明了鐵電材料NC現象,但是缺少對鐵電材料電滯回線來源的理論分析[24].之后,Wong 和 Salahuddin[85]從晶格出發,結合晶格中原子受到的各種微觀力,分析得到了鐵電材料極化強度P與電場強度E的“S”曲線關系圖的物理機制.其中,“S”曲線的負斜率區域內是熱力學不穩定的,而且P具有多值的特點,因此,隨著電壓正、反掃描過程中,在相同電壓下,鐵電層處于不同的極化狀態,因此P-E關系曲線表現出回滯的特點,即“電滯回線”.因此,結合多種理論,以鈣鈦礦型鐵電材料為例,從原子微觀受力出發,推導出P與E的“S”關系曲線;然后結合電位移矢量連續方程,得到材料所帶電荷量Q與電壓V的“S”關系曲線,從宏觀角度(CFE=?QFE/?VFE)證明NC的存在;接著采用吉布斯自由能公式,得到系統能量U與所帶電荷Q的“雙勢阱”關系曲線,又從微觀角度證明NC的存在,系統性地介紹鐵電材料NC現象的物理機制來源. 圖8是鈣鈦礦型(ABO3)鐵電體的晶胞結構圖和極化電場分布圖,圖中B離子所受的力可以分解為由于離子與周圍價電子之間的位移所導致的局域有效原子力Fion、由于偶極子電場導致的極化力Fp和外界電場施加的電場外力Fext. B離子的局域有效原子力可表示為 其中VB為B離子的局域有效電勢能,uB為B離子與其周圍價電子的相對位移.為了簡化,假設相對位移沿著z方向,把uB寫為zB,然后VB(zB) 展開為 這里有VB(0)=0 ,而且由于晶格對稱性的原因奇數項也為零,為了簡化,省略了高階項.其中aB和bB可通過第一性原理計算得到,為了簡化,設aB>0,bB>0.將 (7)式代入 (6)式中,得到 圖8 (a) 鈣鈦礦型 (ABO3)鐵電體的晶胞結構圖[85];(b) (200)晶面的極化場分布圖[85]Fig.8.(a) Conventional unit cell of an FE perovskite (ABO3)[85];(b) schematic of the dipole fields in the (200) plane[85]. B離子除了受有效局域原子力之外,還會和周圍的離子發生庫侖相互作用.當離子i振動時,會產生一個贗偶極矩pi,這個贗偶極子在位置r處會產生一個偶極子電場,其表示式為 其中Ri是離子i的平衡位置,ε0時真空介電常數.將晶胞中各離子在r處產生電場疊加后可得到r處的總偶極子電場 采用Luttinger和Tisza[86]的偶極子疊加理論,可得到B離子處的偶極子電場為 將其代入(11)式中可得 則B離子受到的極化電場極化力為 其中qB為B離子的有效電荷量. 到此為止,已經得到了B離子所受到全部內部微觀力: 局域有效原子力FiBon(zB) 和極化力Fp(RB),接下來推導外部電場E時對B離子所產生的電場外力Fext.由電位移矢量方程D=ε0·E+P可得到電場E與極化極化強度P的關系,其中P為電位移矢量,表示外部電場與內部偶極子相互作用后在材料表面所產生的凈電荷.因此可以得到施加外部電場后對B離子所產生的電場力為 則由(8)式、(15)式和(16)式可以得到B離子所受的合力為 其關系曲線如圖9(a)所示,即P-E關系的“S”曲線.但是當改變外加電場,測量鐵電材料的極化強度,得到圖9(b)中的電滯回線,而不是圖9(a)中的“S”曲線,這是因為在圖9(b)中的藍色虛線區域,P具有多值特點,而且宏觀NC現象是熱力學不穩定的,所以表現出滯回曲線的特點.圖中紅色虛線為鐵電體處于初始狀態時的掃描曲線,藍色曲線為經過一個掃描周期后的掃描曲線. 圖9 鐵電體極化強度 P 和電場 E 之間的關系 (a) PE 關系圖;(b) 電滯回線圖Fig.9.The relationship between polarization P and electric field E of ferroelectrics: (a) P vs.E;(b) hysteresis diagram. 前面提到,材料表面凈電荷QFE即為電位移矢量,即 而對于鐵電材料,可假設認為P?ε0·E[88],則QFE≈P.根據電場強度定義式E=VFE/tFE其中tFE為鐵電材料的厚度,可得到表面凈電荷QFE與電壓VFE 的關系 其關系曲線如圖10(a)所示,根據宏觀電容定義式CFE=?QFE/?VFE,可以看到圖10(a)中紅色虛線框區域為NC區域. 圖10 (a) 鐵電體的 QFE-VFE 關系圖;(b)鐵電體的 UFEQFE關系圖Fig.10.(a) QFE vs.VFE of ferroelectrics;(b) UFE vs.QFE of ferroelectrics. 對于鐵電材料,其吉布斯自由能公式為 其中α,β和λ為材料的常量參數,而且鐵電材料的α為負值[89].可得到能量UFE與電荷QFE的關系 通過上述分析,得到了鐵電材料的本征NC區域,但是由于NC在宏觀上是熱力學不穩定的,因此,需要串聯一個線性的介質層電容(CDE),通過介質層中退極化場的作用[88],將鐵電層的電容(CFE)穩定在NC區域.不同電容系統自由能和極化強度的關系曲線如圖11所示,可以看到,在串聯了一個合適大小的CDE之后,系統自由能的最低點位于鐵電電容的NC區域,因此鐵電層的NC得到了穩定[90]. 圖11 不同電容系統的自由能曲線形貌[90]Fig.11.Energy landscapes of CFE,CDE and their series combination[90]. 由于熱力學不穩定性,不能直接在電路中觀察到NC現象,只能通過對比串聯后系統電容的增大來間接證明鐵電層中NC的存在.其測量電路如圖12(a)所示,測量模式稱為小信號測量,被認為是一種準靜態的測量模式,因為在測量過程中沒有發生極化翻轉[91].Gao等[90]制備了圖12(b)所示的LaAlO3/Ba0.8Sr0.2TiO3超晶格結構,其中LaAlO3為介質層,Ba0.8Sr0.2TiO3為鐵電層,超晶格結構的電容和相同厚度LaAlO3介質層的電容與電壓的關系如圖12(c)所示,可以看到,與相同厚度的LaAlO3介質層相比,超晶格結構的電容增大了,這說明Ba0.8Sr0.2TiO3鐵電層的電容為負值. 圖12 小信號測量模式測量鐵電體 NC (a) 等效電路圖[91];(b) LAO/BSTO 超晶格結構示意圖[90];(c) 電容與電壓的關系[90]Fig.12.Ferroelectric NC measured by small-signal measurement mode: (a) Equivalent circuit diagram[91];(b) schematic diagram of a LAO/BSTO superlattice stack[90];(c) capacitance dependence on voltage[90]. 上述的測量結果是在單電疇近似下得到的,在多電疇鐵電材料HfxZr1–xO2(HZO)電容與介質層電容串聯結構中沒有發現這種直流增強效應[92],因此人們認為目前HZO中的NC是瞬態NC[93],即接下來要討論的內容. 3.2.2 瞬態 NC 到目前為止,得到了鐵電材料的自由能曲線中的本征NC區域,并通過串聯一個介質層電容,通過介質層中能夠退極化場的作用,將鐵電層的電容穩定在NC區域,稱為穩態NC.在鐵電材料中還存在另外一種NC,即瞬態NC,是指在R-CFE串聯電路(圖13)中,當施加一個正(負)脈沖電壓時,在短時間內CFE上的電壓與電荷的變化相反,即CFE上的電荷增加(減少)而電壓下降(增加).關于鐵電材料瞬態NC的實驗現象已有大量的文獻報道[94?97],其中,Khan 等[94]首次在R-CFE串聯電路中觀察到了瞬態NC現象,認為當施加的脈沖電壓超過鐵電材料的矯頑電壓時,鐵電體發生極化翻轉,極化狀態從一個穩定態轉換到另外一個穩定態,會經過NC區域,從而表現出了短暫的NC效應,因此,瞬態NC效應可以看成是鐵電體極化翻轉過程中在自由能曲線中存在負曲率區域的一種表征.之后人們指出導致瞬態NC的直接原因是鐵電材料極化強度的變化速度比金屬極板上自由電荷的變化速度快,而且這個差值越大,瞬態NC現象越明顯[98]. 2018 年,Chang等[99]結合基爾霍夫電路定律和朗道自由能理論對瞬態NC的物理機制進行了分析.考慮圖13所示的電路,根據基爾霍夫定律,電極板電荷Qfree與時間t的關系為 其中?Qfree/?t為電流密度,Vin為輸入電壓,Vout=VFE為鐵電材料電容電壓,R為串聯電阻電阻值,A為鐵電電容的表面積.根據電位移矢量方程,可將自由電荷Qfree 寫為 其中EFE表示穿過鐵電層的電場,ε0為真空介電常數,P為鐵電層的平均極化強度,其與時間的微分方程可根據L-K方程[100]寫為 其中γ為鐵電材料的粘度系數,α1 、α11 和α111 是鐵電材料的熱膨脹系數,tFE和tdep分別是鐵電層的厚度和有效退極化場厚度. 結合(23)式—(25)式中可得 對(24)式兩邊取時間的微分可得 圖13 測量鐵電體瞬態 NC 的 R-CFE 等效電路圖[99]Fig.13.The schematic of a R-CFE circuit for studying the transient NC in ferroelectrics[99]. 由(25)式與(26)式可以看到,自由電荷和極化強度之間通過EFE耦合.同時,自由電荷和極化強度對時間的響應速度分別被R和γ所限制.通過歐拉方法對(25)式和(26)式進行模擬,并且在模擬之前,先輸入一個負電壓,使得鐵電層中的初始極化方向為負.模擬結果如圖14和圖15所示.圖14(a)展示了R-CFE電路對脈沖輸入信號的響應,可以看到,有兩個區域中鐵電電容上自由電荷增加(減少)但是電壓降低(升高),也就是?Qfree/?V<0.從圖14(b)中可以看到,NC 僅發生于鐵電層中極化翻轉時,而且自由電荷和極化強度與隨時間的變化基本一樣.但對其取時間微分,結果如圖14(c)所示,自由電荷和極化強度對時間的微分總是存在一個差距,而且在第一個NC發生時有?P/?t>?Qfree/?t.從 (27)式可以看到,鐵電電容電壓隨時間的變化速度與自由電荷和極化強度隨時間的變化速率之間的差值線性相關.對比圖14(a)和 (d)可看到,在 NC剛開始出現時,?VFE/?t變為負值,而當在施加負向脈沖電壓區間內的的 NC 發生時,?VFE/?t變為正值,此時自由電荷和極化強度減小,但|?P/?t|>|?Qfree/?t|.因此在NC發生時,極化強度的變化速率總是快于自由電荷的變化速率的. 圖14 瞬態NC模擬結果[99] (a) 輸入電壓,輸出電壓和鐵電電容上自由電荷與時間的關系圖;(b) 極化強度和自由電荷與時間的關系圖;(c) 極化強度和自由電荷對時間的微分結果及其差值隨時間的變化曲線;(d) 鐵電電容電壓的變化速度隨時間的變化曲線Fig.14.The simulation results of transient NC[99]: (a) Input voltage,output voltage,and free charge on a ferroelectric capacitor as functions of time;(b) polarization and free charge as functions of time;(c) charge density per unit time for free charge and polarization and the difference between them;(d) change in the voltage across a ferroelectric capacitor per unit time as a function of time. 圖15 (a) 外電阻對 R-CFE 電路中瞬態 NC 的影響;(b) 粘度系數對 R-CFE 電路中瞬態 NC 的影響[99]Fig.15.(a) The effect of the external resistance on transient NC in a R-CFE circuit;(b)the effect of the viscosity coefficient on transient NC in a R-CFE circuit[99]. 由上述分析可得,R-CFE中的瞬態NC與自由電荷和和極化強度隨時間的變化速率之間的差值相關,因此由(25)式和(26)式可得,外部電阻和粘度系數對瞬態NC會產生影響,其模擬結果如圖15所示.由圖15(a)可以看到,隨著外部電阻的增大,極化翻轉速度變慢,瞬態NC持續的時間也變長,這是因為自由電荷需要更多的時間在鐵電電容中建立電場.而且瞬態NC現象也隨著外部電阻的增大而變得更明顯,這是因為隨著R的增大,?Qfree/?t 將變小,(27)式中的差值將增大,因此瞬態NC現象將變得更明顯.同樣地,隨著粘度系數的增大,極化翻轉速度變慢,?P/?t 將變小,因此瞬態NC持續的時間增長,而(27)式中的差值將減小,瞬態NC現象也變得更不明顯.Hoffmann等[101]從鐵電疇翻轉動力學角度分析得到了R-CFE電路中瞬態NC的持續時間 ?T與外部電阻和粘度系數的關系式 其中,CFE為鐵電層單位面積電容,tFE為鐵電層厚度,Ea為鐵電疇翻轉的激活電場[102],EFE為鐵電層的內部電場.可以看到,瞬態NC的持續時間與隨外部電阻和粘度系數的增大而增大,與圖15中的結果相符合. 瞬態NC效應并不能在無滯回Fe-NCFETs中導致瞬時電流增強效應,這是因為瞬態NC的發生伴隨著鐵電體的極化翻轉,而無滯回 Fe-NCFETs沒有發生極化翻轉[103].因此由于瞬態NC導致也能觀察到SS的下降的Fe-NCFETs,但由于自由電荷遲滯現象的存在,器件往往伴隨著較大的回滯電壓[104],對于低功耗邏輯晶體管的實現是不利的,因此仍需要進行更深入的研究. 通過以上分析得到了鐵電材料NC的物理來源,但是由于NC區域多值特性導致的熱力學不穩定性,因此單獨的鐵電材料存在滯回曲線,并不能穩定在NC區域工作,需要串聯一個合適的常規正電容,才能將鐵電材料穩定在NC區域工作. 考慮如圖12所示的電容模型,采用穩態NC理論,則各電容器上的電荷量分別為 由串聯電容的帶電荷量相等可得 則(20)式與(31)式曲線的交點即為器件的工作點[26],如圖16(b)和(c)所示,圖中紅色實線為VG=0 時的溝道電容電荷量與鐵電層電壓的關系曲線,紅色虛線為VG>0 時的溝道電容電荷量與鐵電層電壓的關系曲線.可以看到,當CS<|CFE|時,兩條曲線只有一個交點,如圖16(b)所示,此時器件的轉移特性曲線無回滯現象,稱之為Fe-FETs[91](圖16(d)).而當CS>|CFE|時,兩條曲線在NC區域有多個交點,如圖16(c)所示,此時器件的轉移特性曲線有回滯現象,稱之為 Fe-NCFETs(圖16(e)).而且可以看到,當CS增大時,SS 低,但同時回滯現象也變嚴重了,從(2)式中也可看到這個趨勢. 所以器件的SS與回滯現象之間存在一個本質上的矛盾關系,即不能同時減小SS和回滯現象,Wang等[105]結合 Kolmogorov-Avrami-Ishibashi(KAI)方程[106],從多電疇動態反轉的角度解釋了器件SS與回滯現象之間存在矛盾關系的物理機制. 對于邏輯器件的應用,回滯現象是要避免的,可以通過調節CS與CFE之間的比例,從而調制器件的SS與回滯電壓,即所謂的電容匹配(capacitance matching)工程,研究人員也對此進行了大量的研究[107?112].Si等[113]制作了以 Hf0.5Zr0.5O2/Al2O3為介質層的二維MoS2溝道器件,其中2 nm厚的Al2O3作為掩蔽層和電容匹配層,器件的SS降低到 47 mV/dec,而且消除了回滯現象,為低功耗邏輯器件的實現提供了選擇. 溝道的形狀和材料種類對于器件的性能有著很大的影響.近十年來,為了提高器件性能,延續摩爾定律,各種新技術和新溝道材料被應用于Fe-NCFETs上,也就是所謂的溝道工程,研究人員對這個方向開展了大量的研究工作.而氧化鉿基鐵電材料因具有高介電常數和與CMOS技術兼容性高等優點被人們廣泛應用于Fe-NCFETs研究.以下從溝道的形狀和材料種類出發,分別從三維溝道材料和二維溝道材料的角度總結了近幾年來采用氧化鉿基鐵電體的Fe-NCFETs的重要研究成果,并對器件的SS、開關電流比、回滯電壓和漏電流等性能的改善進行了分析概述,對于Fe-NCFETs的設計與制造具有指導意義. 圖16 器件電容電荷量與電壓的關系 (a) 電容模型;(b) C S<|CFE| ;(c) C S<|CFE| ;(d) Fe-NCFETs[91];(e) Fe-FET[91]Fig.16.The relationship between capacitive charge and voltage of the device: (a) Capacitance model;(b) C S<|CFE| ;(c) C S<|CFE| (d) Fe-NCFETs[91];(e) Fe-FETs[91]. 采用硅、鍺基材料、III-V族化合物和碳納米管等三維材料作為溝道的Fe-NCFETs有諸多優點,如與傳統CMOS工藝的兼容性高、溝道與鐵電層之間界面性能好、在三維尺度上的可控性高、電學性能穩定.因此,三維溝道Fe-NCFETs被認為是下一代MOS晶體管的主要選擇之一[114]. 4.1.1 硅溝道 氧化鉿基鐵電材料的出現,使得利用傳統CMOS技術集成硅和鐵電材料成為了可能,自2014年 Cheng和 Chin[115]首次報道了 SS小于60 mV/dec的采用氧化鉿基鐵電體(HfZrO,HZO)的硅基Fe-NCFETs以來,人們對硅基Fe-NCFETs進行了廣泛的研究,器件的結構也從最開始的平面型(planar)發展到現在的FinFET型和GAA納米線型. Fan等[116]制備了鐵電層為 10 nm-HfAlO(Al: 6%) 的 planar 型硅基 Fe-NCFETs,如圖17(a)所示,器件的性能優異,其開關電流比大于108,正掃和反掃SS均低于25 mV/dec,而且回滯電壓僅為 20 mV,成功實現了無回滯且低 SS的 Fe-NCFETs.他們采用了TaN作為柵電極,柵電極會對 HfAlO鐵電層施加應力,這個應力會導致HfAlO由順電性的單斜晶相向具有鐵電性的正交晶相轉變[117],而且由于鐵電體具有壓電性質,應力的存在還會增大鐵電體的極化強度,因此隨著TaN中的N含量的增加,TaN的應力逐漸增大,HfAlO的剩余極化強度增大,如圖17(b)所示.而且他們還采用了CF4等離子體對器件進行鈍化處理以消除界面處的氧離子缺陷,從而減小了界面陷阱電荷對鐵電層極化作用的抑制作用,增大了鐵電層對溝道表面電勢的放大作用,如圖17(c)所示.由圖17(d)可以看到,在經過柵電極應力和F離子鈍化作用后,不僅器件的SS大大降低了,而且回滯現象也得到了抑制.他們通過測量恒壓應力和相對應力誘導漏電流的方法研究了F離子鈍化作用對鐵電層NC的影響,進一步證明界面處的陷阱電荷和氧離子空位在經過F離子鈍化作用后被消除了[118]. 圖17 平面型硅基- HfAlO Fe-NCFETs[116] (a) 器件截面透射電子顯微鏡 (transmission electron microscope,TEM)圖;(b) 剩余極化強度與TaN中N含量的關系曲線;(c) F離子鈍化作用對鐵電層能帶影響的示意圖;(d) 不同處理作用后器件的SS與源漏電壓的關系Fig.17.Planar Silicon based HfAlO Fe-NCFETs[116]: (a) HR TEM cross-section image;(b) polarization as a function of nitrogen content of TaN;(c) schematic band diagram of HfAlO before and after F-passivation;(d) SS as a function of VDS after different treatments. Cheng 等[119]研究了 Hf1–xZrxO2中 Zr含量對planar型硅基Fe-NCFETs性能的影響,發現隨著Zr含量的增大,Hf1-xZrxO2中正交相的占比增大,鐵電層的極化強度增大,即鐵電性增強,器件的SS減小.但當Zr的含量超過50%時,Zr離子的漂移作用會導致介質層漏電流的增大,從而降低了鐵電層電容與溝道電容的匹配度,導致SS退化,最后通過實驗確定當Zr含量為25%時,器件的SS和介質層漏電流都較小.其他研究人員也對planar型硅基Fe-NCFETs中柵電極種類[120]、鐵電層退火溫度與電壓掃描范圍[121]和ZrO2籽晶層[122]對器件性能的影響進行了研究.由于結構本身的限制因素,planar型硅基Fe-NCFETs和傳統MOSFETs相比,其亞閾值區性能改善并不理想,維持SS低于60 mV/dec的電流區間往往小于三個數量級,因此人們對其他結構如FinFET和GAA結構硅基Fe-NCFETs進行了研究. Li等[123]報道了首個硅基鐵電NC FinFET,他們采用 5 nm Hf0.42Zr0.58O2作為鐵電體,其結構如圖18(a)所示,溝道寬度約為 30 nm,柵介質層為MFMIS雙TiN柵結構.圖18(b)是不同柵壓下鐵電層對柵壓的放大系數曲線,可以看到,柵壓放大系數最大為1.4左右.而由圖18(c)可以看到,鐵 電 NC FinFET 的 SS 為 58 mV/dec,比 傳 統FinFET 的SS(88 mV/dec)下降了1.5倍,與圖18(b)中的測量結果相符合.2018年Zhou等[25]采用全耗盡SOI為襯底,制作了鐵電層為4 nm Hf0.5Zr0.5O2的硅基鐵電NC FinFET,不僅將器件SS降低到54.5 mV/dec,而且還消除了回滯現象,使其回滯電壓僅為3 mV.除此之外,他們還首次在硅基Fe-NCFETs中發現了由于鐵電層NC和漏端電容耦合作用導致的負DIBL和NDR效應,對于抑制短溝效應和實現器件尺寸的進一步減小是很有利的. Zhang等[124]在超薄SOI襯底制備了如圖19(a)所示的硅基鐵電NC p-FinFET,其柵介質層結構為 Hf0.42Zr0.58O2/TiN/TaN/TiN/W,這種多層柵電極結構可以在降低鐵電層和柵電極之間界面態密度的同時增強對鐵電層的柵控能力,同時在鐵電層與溝道之間沉積了一層1 nm厚的HfO2界面層,改善了鐵電層與溝道之間的界面性能.而且多柵結構會對Fin溝道施加應力,增強了溝道載流子遷移率.圖19(b)是傳統FinFET和NC-FinFET在不同柵長下的IDS數值,可以看到,NC-FinFET 的IDS比傳統FinFET的IDS提高了250%以上,這得益于NC-FinFET較低的界面態密度和較高的載流子遷移率.在這個器件中,HZO鐵電薄膜的厚度已經達到了 3 nm,為實現5 nm及以下節點高性能和低功耗晶體管性能需求提供了技術支持.Chen等[125]也對具有不同柵長和溝道寬度的硅基HZO NC FinFET進行了研究,發現當柵長是溝道寬度的十倍以上時,器件的 SS大都能低于60 mV/dec,這是因為柵長變大時,鐵電層對柵壓的放大作用增強,從而增強了柵電極對溝道的控制能力,改善了 SS.可以看到,在結合了鐵電材料之后,FinFET型器件的電流性能提升(~250%)比planar型器件的電流性能提升(~50%)更明顯,這得益于FinFET結構器件具有更強的柵控能力. 圖18 硅基 NCFinFET[123] (a) 器件截面 TEM 圖;(b) 鐵電 NCFinFET 的柵壓放大系數與柵壓的關系曲線;(c) 常規 FinFET 和鐵電NCFinFET的SS與柵壓的關系曲線Fig.18.Silicon based NC-FinFET[123]: (a) TEM cross-sectional image of NC-FinFET with TiN internal gate,HfZrO FE film and TiN gate;(b) the gate amplification coefficient as a function of VG for NC-FinFET;(c) SS as a function of VG for conventional Fin-FET and NC-FinFET. 圖19 (a)硅基鐵電 NCp-FinFET 截面 TEM 圖[124];(b) 源漏電流與柵長關系曲線[124]Fig.19.(a) TEM cross-sectional image of silicon based NC-p-FinFET[124];(b) IDS as a function of gate length[124]. Lee等[126]首次報道了GAA雙層堆疊硅納米線結構 Fe-NCFETs,器件采用 10 nm HZO 為鐵電層,表現出了優異的電學性能,其開關電流比超過 108,平均 SS 為 43.85 mV/dec,回滯電壓僅為2.77 mV.器件結構如圖20(a)所示,共柵堆疊納米線結構可以有效增強柵對溝道的控制能力,而且在保持器件特征尺寸不變的情況下增加了溝道的有效寬度,因此增大了器件的跨導和溝道電流,但是和單層溝道器件相比,其電流增幅小于兩倍,這是因為雙層溝道器件引入了更多的寄生電阻[127].他們還在HZO下面淀積了一層2 nm厚的ZrO2籽晶(圖20(b)),由HZO的X射線衍射(X-ray diffraction,XRD)曲線 (圖20(c))可看到,與沒有ZrO2籽晶層(灰色曲線),有ZrO2籽晶層(紅色曲線)HZO正交相的衍射強度增強了,因為ZrO2籽晶層可在HZO沉積的時候誘導正交相HZO的生成,提高了HZO的結晶性.這種采用ZrO2籽晶層誘導正交相HZO生成的方法省去了傳統HZO生長工藝中高溫結晶退火步驟,大大提高了器件的熱穩定性. 硅基Fe-NCFETs具有與CMOS工藝兼容性高和工藝成熟等優勢,器件也表現出了SS低、開關電流比大和性能穩定等優點,但是硅材料的載流子有效遷移率低,限制了晶體管開態電流的大小,所以人們對采用其他三維溝道材料的Fe-NCFETs進行了研究. 圖20 雙層堆疊硅納米線 GAA 結構 Fe-NCFETs[126] (a) 器件截面 TEM 圖;(b) 溝道部分高分辨率 TEM 圖;(c) HZO 層的掠入角XRD曲線Fig.20.Two-layer stacked silicon nanowire GAA Fe-NCFETs[126] : (a) TEM cross-sectional image of the device;(b) HRTEM of a portion of the channel;(c) the GIXRD spectrum for the as-deposited HZO layer. 4.1.2 鍺基材料溝道 鍺基材料具有很多優點,如鍺(Ge)的空穴遷移 率 為 1900 cm2·V–1·s–1,是 硅 的 空 穴 遷 移 率(430 cm2·V–1·s–1)的 5 倍左右[128],而且還可以通過摻入錫(Sn)引入應力從而進一步提高空穴遷移率,因此人們對Ge基NC-pFET進行了廣泛的研究. Zhou等[129]報道了第一個SS小于60 mV/dec的Ge基NC-pFET,他們采用HZO作為鐵電層分別制備 Ge溝道 NC-pFET和 Ge0.96Sn0.04溝道NC-pFET,其結構示意圖分別為圖21(a)和21(b),HZO層的厚度為6.5 nm.但是器件的性能并不理想,圖21(c)和 (d)分別是 Ge溝道 NC-pFET和Ge0.96Sn0.04溝道NC-pFET的轉移特性曲線圖,可以看到,器件的回滯電壓分別為 2.3 V 和 0.4 V,平均SS也僅為60 mV/dec左右,器件的開關電流比也僅為103左右,導致器件的靜態功耗大大增加,這是由于 Ge 帶隙較小 (Eg,Ge=0.66 eV),結間漏電流和帶間隧穿漏電流增大,因此器件的關態漏電流增大.而且與常規pFET相比,在VDD等于1 V時的源漏電流僅提高了20%,NC效應不明顯. Zhou等[130]將Ge0.96Sn0.04溝道NC-pFET中HZO的退火結晶溫度從400 ℃增大到500 ℃,改善了鐵電相HZO的結晶質量,提高了其Pr/Ec比值,在將SS降低到20 mV/dec以下的同時也將回滯電壓也降低到了 100 mV以下,而且與常規pFET相比,溝道電流改善比例提高到了30%.隨后,他們研究了Ge溝道NC-pFET中柵電容CG與跨導Gm的關系[131],發現CG-VG和Gm-VG曲線在相同的柵壓位置都出現了峰值,而且SS-IDS曲線有一個下降臺階,對應的VGS與CG-VG峰值柵壓是一樣的,而且峰值越大,下降臺階越明顯,進一步證明HZO介質層的NC效應可以有效改善器件的性能.但文獻[131]中只是對器件的性能改善做了表征,缺少對鐵電材料內在結構的研究,如果能將鐵電材料結構的改變及其相關機理研究清楚,將可以更好地指導器件的設計. 圖21 Ge 基- HZO NCP 型晶體管[129] (a) Ge 溝道器件結構示意圖;(b) Ge-Sn 溝道器件結構示意圖;(c) Ge 溝道器件轉移特性曲線;(d) Ge-Sn 溝道器件轉移特性曲線Fig.21.Germanium based HZO NC-pFET[129]: (a) Schematic diagram of the device with Ge channel;(b) schematic diagram of the device with Ge-Sn channel;(c) transfer characteristic curve of the device with Ge channel;(d) transfer characteristic curve of the device with Ge-Sn channel. Zhou等[132]對Ge基NC-pFET中鐵電層電容CFE和溝道電容CMOS之間的匹配進行了研究,在Ge溝道器件中發現了NDR效應,NDR效應來源于柵介質層電容與漏端電容的耦合,其耦合因子 ηGD的表達式為:ηGD=CGD/(|CFE|?CMOS) ,其中CGD表示柵與溝道的耦合電容.當器件沒有回滯時,即|CFE|>CMOS,此時隨著鐵電層厚度tFE和柵壓VGS的增大,ηGD增大,NDR 效應變明顯;當器件有回滯時,即|CFE| Alghamdi等[135]研究了柵壓掃描速度和掃描范圍對Ge納米線NC-pFET的SS和IDS的影響.當柵壓掃描范圍為 ±5 V時,只有在掃描時間超過25 μs的情況下才能在轉移特性曲線中觀察到回滯現象,而當掃描時間超過 25 μs時,隨著掃描時間的延長,回滯電壓反而變小,如圖22(a)和(b)所示.這是因為鐵電體中極化子的反轉速度較慢,當柵壓掃描速度過快時,極化子在柵壓掃描過程中沒有完成一個完整的反轉過程,所以觀察不到明顯回滯現象;而當掃描時間超過極化子的反轉所需的最小時間時,隨著掃描時間的延長,極化子能充分跟上掃描電壓的變化速度,所以回滯電壓減小.隨著柵壓掃描范圍的減小,IDS減小,而且出現回滯現象的最小掃描時間變長(圖22(c)),他們認為這可能是因為隨著最大柵壓減小,極化子的反轉速度變慢,因此導致極化子反轉所需最短時間變長,但是更明確的物理機制需進一步的理論和實驗分析. 圖22 鍺納米線 Fe-NCFETs[135] (a) 柵壓掃描范圍為 ±5 V 時在不同掃描時間下的轉移特性曲線;(b) 柵壓掃描范圍為±5 V時的回滯電壓與掃描時間關系曲線;(c) 不同柵壓掃描范圍下的ID,Max與掃描時間關系曲線Fig.22.Germanium nanowire NC-pFET[135]: (a) The transfer characteristic curve at different sweep times for ±5 V sweep range;(b)hysteresis versus sweep time for ±5 V sweep range;(c) maximum drain current versus sweep time for different sweep ranges. Ge基材料由于具有較高的空穴遷移率,因此被廣泛應用于NC-pFET,但是目前仍然存在一些關鍵問題,比如高頻下滯回現象明顯、由于Ge材料帶隙較小導致開關電流比小、GexSny溝道中難以實現Sn元素的高濃度摻雜以及與CMOS技術的兼容性問題等. 4.1.3 III-V 族化合物溝道 III-V 族 化 合 物 材 料 ,包 括 GaAs、 InAs、InGaAs和InSb等,具有較高的電子遷移率(如:μn,InAs=42000 cm2·V–1·s–1),是 Si電 子遷 移 率(1600 cm2·V–1·s–1)的十倍以上,因此被認為是nMOS溝道材料極具潛力的選擇[128]. Luc等[136]報道了第一個SS小于60 mV/dec的平面型In0.53Ga0.47As溝道Fe-NCFETs,其結構示意圖如圖23(a)所示,采用8 nm HZO作為鐵電層,在HZO與溝道之間有1 nm的Al2O3介質層,襯底為InP.他們研究了不同退火溫度和退火時間下的器件性能,發現當退火溫度為500 ℃以及退火時間為30 s時,器件的性能最好,此時器件的轉移特性曲線如圖23(c)所示,可以看到,當VDS為0.05 V 時,器件的最小 SS 達到 11 mV/dec,回滯電壓為 0.7 V,開關電流比為 105左右.2019 年,Chang等[137]報道了第一個Fin結構In0.53Ga0.47As溝道Fe-NCFETs,其結構示意圖如圖23(b)所示,器件的物理參數和之前報道的平面型器件類似.其轉移特性曲線如圖23(d)所示,當VDS為0.05 V時,最小 SS 為 23 mV/dec,回滯電壓為 0.2 V,傳輸性能與平面型器件相比有所改善,但是其開關電流比小于105,低于平面型器件,這可能是由于FinFET器件的表面態較多導致漏電流增大,從而降低了開關電流比,還需要深入研究以探明其內在機理,進一步提高III-V族溝道Fe-NCFETs的性能. III-V族化合物由于具有極高的電子遷移率,有望替代Si成為nMOS器件的溝道材料,因此也被用于n型Fe-NCFETs的研究,但是III-V族化合物與介質層之間的界面性能差和難以實現高濃度摻雜是目前存在的主要問題. 圖23 In0.53Ga0.47As溝道 Fe-NCFETs (a) 平面型器件的結構示意圖[136];(b) Fin 結構器件的結構示意圖平[137];(c) 平面型器件的轉移特性曲線[136];(d) Fin結構器件的轉移特性曲線[137]Fig.23.In0.53Ga0.47As channel Fe-NCFETs: (a) Schematic diagram[136] and (c) transfer characteristic curve of planar device[136];(b) schematic diagram[137] and (d) transfer characteristic curve of Fin device[137]. 4.1.4 碳納米管溝道 首個碳納米管Fe-NCFETs由Srimani等[138]報道,器件結構如圖24(a)所示,采用MFMIS結構,其中鐵電層為 10 nm HfAlO.與碳納米管MOSFETs(藍色曲線)相比,碳納米管Fe-NCFETs(紅色曲線)的電學性能更優異,圖24(c)為器件的轉移特性曲線,可以看到,加了HfAlO鐵電層之后,晶體管的SS有所提高,其中Fe-NCFETs的平均 SS為 55 mV/dec,而且柵極漏電流也減小了(圖24(d)).但是由圖24(b)中的電滯回線可以看到,HfAlO層的電滯回線不像鐵電體的電滯回線,反而更像由于內部金屬柵充放電導致的回滯現象.由于他們沒有對HfAlO的晶相結構進行研究,因此由于HfAlO的鐵電性而導致器件性能改善的說法需要進行進一步的實驗驗證.目前關于碳納米管Fe-NCFETs的實驗報道相對較少,其工作機理也尚未明確,仍需要進行更多的理論和實驗研究. 二維材料如過渡金屬硫族化物、烯類材料和黑磷等具有豐富的界面效應、高的電子遷移率、可調控的光電性能和低的光散射損失等優點[139].而且二維材料的厚度非常小(原子尺度),所以對于使用二維溝道材料器件,其理論特征長度非常小,可以有效地抑制短溝道效應從而獲得非常低的關斷電流,對于低功耗晶體管的實現是很有利的.因此二維材料被廣泛應用于Fe-NCFETs[140?143],器件也表現出低 SS (6.07 mV/dec)[33]和大開關電流比(>109)[144]等優異的電學性能. 4.2.1 過渡金屬硫族化物材料 Nourbakhsh等[108]于2017年首次報道了以MoS2作為溝道的Fe-NCFETs,器件采用Al摻雜HfO2作為鐵電層.他們對不同Al摻雜劑量和鐵電層厚度做了研究,發現當采用10 nm厚7.3% Al:HfO2的鐵電層時,器件表現出較好的電學性能,SS 降低到 55 mV/dec,回滯電壓為 17 mV,與僅用HfO2作為介質層的FET相比,其電壓放大了1.25 倍,SS 下降了 10 mV/dec,IDS增大了兩倍左右.但是 SS <60 mV/dec 只能維持 1 個電流數量級,這可能是熱噪聲導致的,而且他們沒有排除內部金屬柵的充放電效應對于SS的影響,因此提到的穩態NC導致SS降低是有待討論的. 圖24 碳納米管 Fe-NCFETs[138] (a) 器件橫截面 TEM 圖;(b) 電滯回線;(c) 轉移特性曲線;(d) 柵電流和柵壓的關系曲線Fig.24.Carbon nanotube Fe-NCFETs[138]: (a) TEM cross-sectional image;(b) Pr vs.E;(c) the transfer characteristic curve;(d) IGS as a function of VGS. 圖25 MoS2 鐵電 NC 體晶體管[145] (a) 器件結構圖;(b) VG=± 7 V 的轉移特性曲線;(c) VG=± 10 V 時的轉移特性曲線Fig.25.MoS2 Fe-NCFETs[145]: (a) Structure of the device;(b)transfer characteristic curve of VG=± 7 V;(c)transfer characteristic curve of VG=± 10 V. Yap等[145]報道了相同結構的Fe-NCFETs,如圖25(a)所示.他們指出,當掃描電壓為 ±7 V 時,轉移特性曲線表現出順時針回滯曲線(圖25(b)),這是由于MoS2/Si3N4界面層陷阱電荷充放電導致的;當掃描電壓增大到10 V時,轉移特性曲線表現出逆時針回滯曲線(圖25(c)),這是由于掃描過程中極化子的反轉導致的.當對器件施加脈沖電壓時也發現了同樣的情況,與瞬態電容理論模型分析得到的結果一致. McGuire等[33]采用 15 nm 厚的 Hf0.5Zr0.5O2作為鐵電層,制備了內部TiN金屬柵結構的MoS2Fe-NCFETs,SS 最小為 6.07 mV/dec,比常規 MoS2FET 的 SS(161 mV/dec)下降了 2 個數量級,而且在4個電流數量級內的平均SS為8.03 mV/dec.當改變介質層厚度、鐵電層厚度和源漏電壓時,都可以看到明顯的SS降低現象.但是由于內部金屬柵的存在,在所有掃描過程中都存在回滯現象,而且回滯電壓隨著測量頻率的增大而變大,表明導致器件SS降低的原因為瞬態NC,而不是穩態NC.人們也研究了背柵電壓模式[30]、柵介質層材料[144]、柵長[146]和低頻噪聲影響[147]等對MoS2 Fe-NCFETs的影響,發現器件均能表現出較低的SS,說明MoS2在Fe-NCFETs方面有極大的潛力. 除了MoS2之外,WSe2也被用作Fe-NCFETs溝道材料[140,148,149],其中Si等[140]分別制備了以Hf0.5Zr0.5O2作為鐵電層的MFIS型和MFMIS型WSe2Fe-NCFETs,如圖26(a)和 (b)所示.圖26(c)為MFIS型Fe-NCFETs轉移特性曲線,可以看到,當源漏電壓為0.1 V時,正向掃描亞閾值擺幅SSFor為 57.5 mV/dec,反 向 掃 描 亞 閾 值 擺 幅SSRev為 40.2 mV/dec,導致 SSRev小于 SSFor的原因是由于在反向掃描過程中,極化子的反轉會給柵極帶來一個額外的電壓降,從而進一步降低了器件的 SS.圖26(d)為MFMIS型 Fe-NCFETs轉移特性曲線,當源漏電壓為 0.1 V 時,SSFor和 SSRev分別為 41.2 mV/dec 和 14.4 mV/dec,由于內部金屬柵對鐵電層電壓放大作用均勻化,因此MFMIS型Fe-NCFETs的SS要比MFIS型Fe-NCFETs的SS低,但同時內金屬柵的充放電效應也導致其回滯電壓的增大. 4.2.2 石墨烯和黑磷 以石墨烯或黑磷作為溝道的Fe-NCFETs主要 采 用 如 P(VDF-TrFE)[141,142]、SrBi2NbO9[150]、PMN-PT[151,152]和 PbZrO3[153]等傳統鐵電材料,隨著材料制備工藝的改進,采用氧化鉿基鐵電體的二維石墨烯/黑磷Fe-NCFETs近來已有報道. Lee等[154]通過pALD在單層石墨烯上生長了5 nm厚的介孔結構HfxAlyO2,并研究了不同Al組分下的相關性能參數,如圖27所示.由圖27(b)可以看到,當 Al組分為 9.5%時,HfxAlyO2材料的相對介電常數達到最高值 (e=25),是純凈HfO2的相對介電常數 (e=17)的 1.5 倍,他們認為這是因為在這個組分下,HfxAlyO2的晶胞結構主要為四方相,而四方相HfxAlyO2的介電常數比單斜相和立方相HfxAlyO2的介電常數高.所以他們采用密度泛函理論分析了不同組分下HfxAlyO2的三個相之間的能量差值,如圖27(c)所示,當Al組分為7.9%—9.3%時,晶體結構為四方相,與實驗結果中的9.5%一致.然后,他們測試了以HfxAlyO2(9.5% Al) 作為鐵電層的 FET 的轉移特性曲線,如圖27(d)所示,可以看到,由于石墨烯材料獨特的帶隙結構,器件的開關電流比很小,僅為2.75,這對于低功耗晶體管是不利的.而且氧化鉿基材料只有在正交相下才能體現出鐵電性能,他們提到了四方相HfxAlyO2是不具有鐵電性的,因此這里的HfxAlyO2只是作為普通的介質層,而不具備鐵電體的效應,所以以氧化鉿基材料為鐵電介質層的石墨烯Fe-NCFETs仍需進一步研究. 圖26 WSe2 鐵電 NC 體晶[140] (a) MFIS 型器件結構圖;(b) MFMIS 型器件結構圖;(c) MFIS 型器件的轉移特性曲線;(d) MFMIS型器件的轉移特性曲線Fig.26.WSe2 Fe-NCFETs[140]: (a) Structure of MFIS device;(b) structure of MFMIS device;(c) transfer characteristic curve of MFIS device;(d) transfer characteristic curve of MFMIS device. 圖27 石墨烯- HfxAlyO2 晶體管[154] (a) 在石墨烯/二氧化硅襯底上沉積的 HfxAlyO2 薄膜;(b) HfxAlyO2 的相對介電常數;(c) 不同Al組分下HfxAlyO2三個相的能量差;(d) 轉移特性曲線(9.5% Al)Fig.27.Graphene-HfxAlyO2 transistor[154]: (a) HfxAlyo2 films deposited on graphene/SiO2 substrates;(b) relative dielectric constant of HfxAlyO2;(c) energy difference among three phases in HfxAlyO2 with different Al concentrations;(d) transfer characteristic curve. Tian等[155]于2019年首次報道了氧化鉿基黑磷 Fe-NCFETs,其結構如圖28(a)所示,采用內部Al金屬背柵電極以增強柵對溝道的控制能力,黑磷和Al金屬柵電極之間為5 nm厚的Al2O3介質層,然后在Al金屬柵上串聯一個HfZrO2厚度為20 nm的電容.圖28(b)為器件的轉移特性曲線,紫色曲線表示串聯了HfZrO2電容的Fe-NCFETs,紅色曲線表示沒有HfZrO2電容的傳統FET,可以看到傳統FET的曲線表現出回滯現象,這是由于黑磷和Al2O3界面層陷阱電荷的充放電導致的.與傳統FET相比,Fe-NCFETs由于NC效應的引入,亞閾值區域更陡峭,但由于鐵電回滯效應的影響,其回滯現象更明顯.從圖28(c)可以看到,Fe-NCFETs的SS雖然比傳統FET小,但由于黑磷和Al2O3界面層缺陷電荷較多,導致其SS不能低于 60 mV/dec,而且隨著測試次數的增加,SS 也逐漸退化,器件性能的保持度較差. 石墨烯和黑磷在理論上預測可作為Fe-NCFETs理想的二維溝道材料,但是實驗上的解釋仍不清晰,而且與過渡金屬硫族化合物Fe-NCFETs相比,其界面性能較差,SS 不能降低到60 mV/dec 以下,電流開關比很小 (<104),關于其實驗方面的報道也較少.因此,在實現性能優異的石墨烯和黑磷Fe-NCFETs之前,需要克服很多理論上和實驗上的困難. 圖28 黑磷鐵電 NC 體晶體管 [155] (a) 器件結構圖;(b) 轉移特性曲線;(c) 不同 Id 下的 SSFig.28.Black phosphorus Fe-NCFETs[155]: (a) Structure of the device;(b) transfer characteristic curve;(c) SS in different Id.. 與過渡金屬硫族化物、石墨烯和黑磷等二維材料相結合的Fe-NCFETs表現出了優異的電學性能,二維材料原子級別的厚度也為晶體管特征尺寸進入3 nm提供了可能.但是二維材料與柵介質層的界面性能較差,溝道表面缺陷態較多,在升高器件SS的同時也加重了回滯現象,這導致器件的功耗急劇增大,而且二維材料與傳統CMOS工藝兼容性較差.所以為了實現二維材料溝道Fe-NCFETs的商業應用仍需進行大量的實驗研究,目前主要有3個研究方向: (1)降低高k介質和二維材料的界面密度,以保持固有的高載流子遷移率;(2)實現源/漏區的高濃度摻雜以降低接觸電阻;(3)提高器件性能的穩定性. 表1是近幾年發表的采用氧化鉿基鐵電體的Fe-NCFETs的性能參數表,按照器件結構和溝道材料分類,列舉了器件的 SSmin、Hysteresis、Orders ofIDS、VD和Ion/Ioff等參數,其中 Hysteresis表示回滯電壓,Orders ofIDS表示 SS 小于 60 mV/dec的源漏電流數量級跨度,Ion/Ioff表示開關電流比.不同器件SSmin和Hysteresis之間的關系如圖29所示,為了實現器件在低功耗邏輯電路中的應用,須保持 SS小于 60 mV/dec以及 Hysteresis小于0.01 V,可以看到,只有一部分硅基 Fe-NCFETs可以滿足此條件,所以硅基Fe-NCFETs是目前最有可能替代傳統MOSFETs成為下一代低功耗晶體管的選擇. 作為未來CMOS理想的溝道材料需要滿足一些條件,比如具有合適的帶隙、低的缺陷態密度、高的載流子遷移率、與介質層的界面性能好、與CMOS技術兼容性高和成本低等,目前沒有任何一種材料滿足以上所有條件.因此,傳統CMOS技術正在進入一個新的階段,需要尋找新型材料和新的設計方案,以在這些條件之間尋找一個平衡,來滿足未來器件對溝道材料的要求. 圖29 實驗報道的 Fe-NCFETs的 SS 與 Hysteresis關系圖 (2D[30,33,108,140,144,146?148,155],Si[25,116,118,119,121,123?126],GeSn[129,130,134,156],InGaAs[136,137])Fig.29.SS versus Hysteresis of the reported Fe-NCFETs(2D[30,33,108,140,144,146?148,155],Si[25,116,118,119,121,123?126],GeSn[129,130,134,156],InGaAs[136,137]). 表1 實驗報道的 Fe-NCFETs的性能參數對比Table 1.Performance comparison of the reported Fe-NCFETs. 隨著晶體管特征尺寸進入10 nm,功耗增加變得不可忽視,與傳統 MOSFETs相比,Fe-NCFETs具有SS低、負DIBL等優點,提高了晶體管的開關電流比,極大程度地降低了器件的功耗,為實現晶體管尺寸的進一步縮小和摩爾定律的延續提供了選擇.其中,摻雜氧化鉿基鐵電材料的發現改善了傳統鐵電材料與CMOS工藝兼容問題,使得Fe-NCFETs的性能大大提高,因此近幾年來采用摻雜氧化鉿基鐵電材料的Fe-NCFETs被廣泛研究,器件的性能也大大提升.目前 Fe-NCFETs的應用主要集中于存儲器方面[145,157,158],其原理是基于鐵電材料處于兩個極化狀態時晶體管具有不同的電流數值,而鐵電層極化反轉導致晶體管表層處于不同狀態的特性,在新一代顯示屏——有源矩陣有機發光二極管中也具有應用潛力[139,159]. 但是在Fe-NCFETs大規模投入商業應用之前,仍需要解決以下幾個關鍵問題. 第一,Fe-NCFETs中的滯回現象.滯回現象的存在阻礙了邏輯晶體管的應用,而鐵電材料本身存在滯回的特性,因而在設計Fe-NCFETs時可以考慮從減小鐵電材料厚度、增大溝道的摻雜濃度以減小溝道電容、減小VDD和VG掃描上限和調節鐵電材料的參數等方面入手.但是要注意的是,由于在滯回電壓和SS之間存在權衡關系,因此在降低滯回電壓的時候將會增大SS. 第二,內部金屬電極引入的問題.采用內部金屬電極結構可以均勻鐵電層在溝道方向上的電勢放大效果,但極大地增加了器件的制造難度,對于器件尺寸的進一步減小是不利的,而且會導致柵極漏電流的增加,降低了器件的穩定性能.可以從柵電極結構的設計、柵電極材料的選擇以及制作工藝等幾個方面改進這個問題. 第三,納米尺度下面臨的一些問題.隨著晶體管特征尺寸進入10 nm,鐵電層的厚度也減小到了 3 nm 以下,Lee 等[160]指出將 1 nm 厚的 HZO鐵電薄膜集成在Fe-NCFETs上以獲得陡峭的SS是可行的.但是如何在納米尺度下有效地控制鐵電層的界面態密度是需要認真考慮的,小尺度下氧化鉿基鐵電體的電疇結構也需要進一步研究.而且,隨著器件尺寸的減小,量子效應變得不可忽略,如溝道電流的量子輸運現象[161?163],需要探明其微觀機制并結合利用,以指導材料和器件的設計,進一步發掘Fe-NCFETs的應用潛力. Fe-NCFETs作為一種新型低功耗器件,雖然目前在材料和工藝上仍然存在很多技術問題,但是隨著研究的深入,將成為下一代CMOS最具潛力的器件之一.2.2 鐵電材料分類

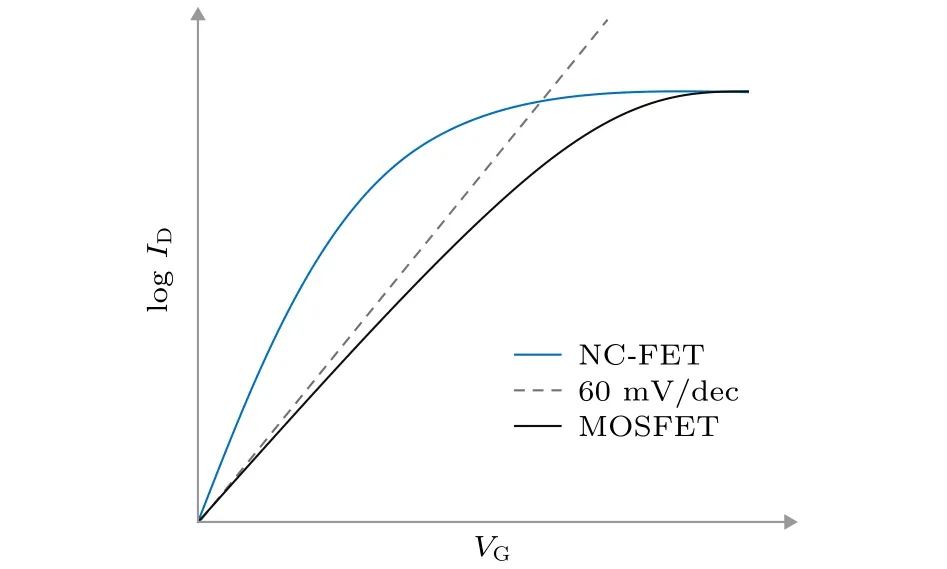

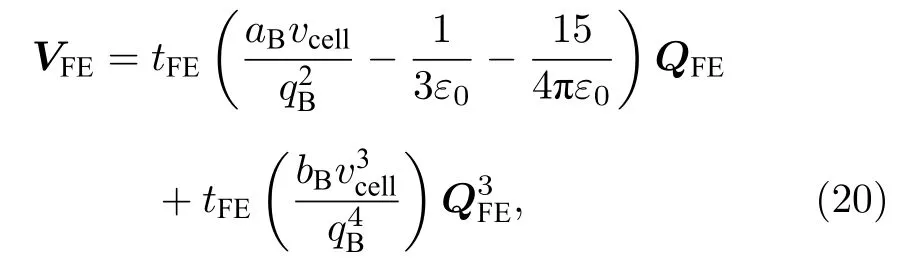

3 Fe-NCFETs的基本原理

3.1 不同柵介質層結構的Fe-NCFETs

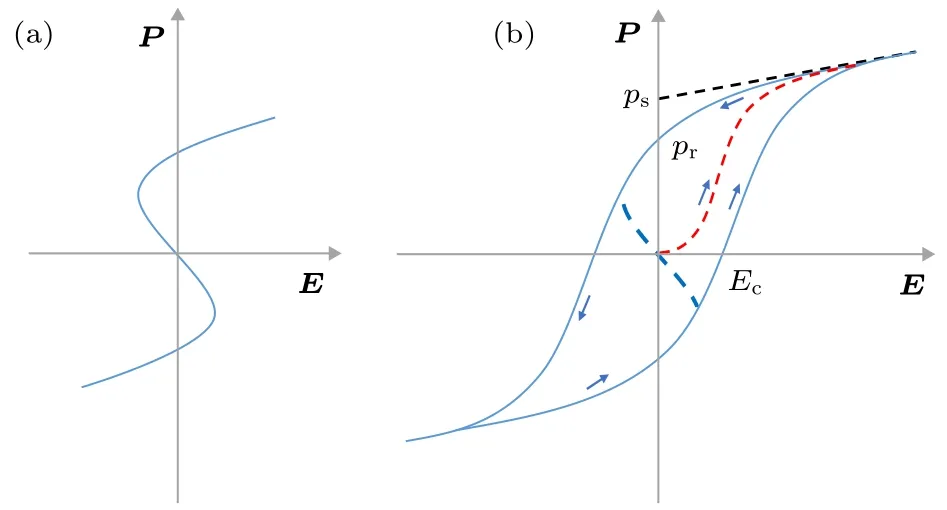

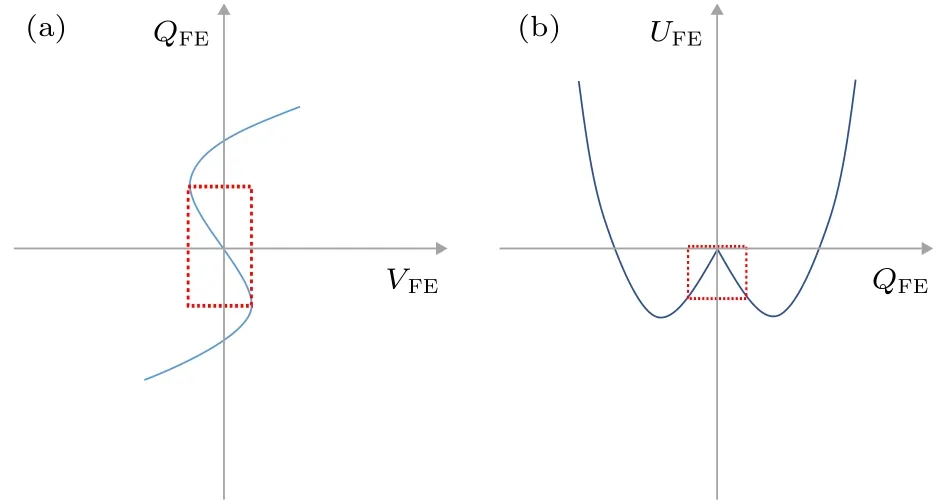

3.2 鐵電材料NC效應的微觀本質

3.3 NC器件的工作區域

4 Fe-NCFETs溝道工程研究進展

4.1 三維溝道

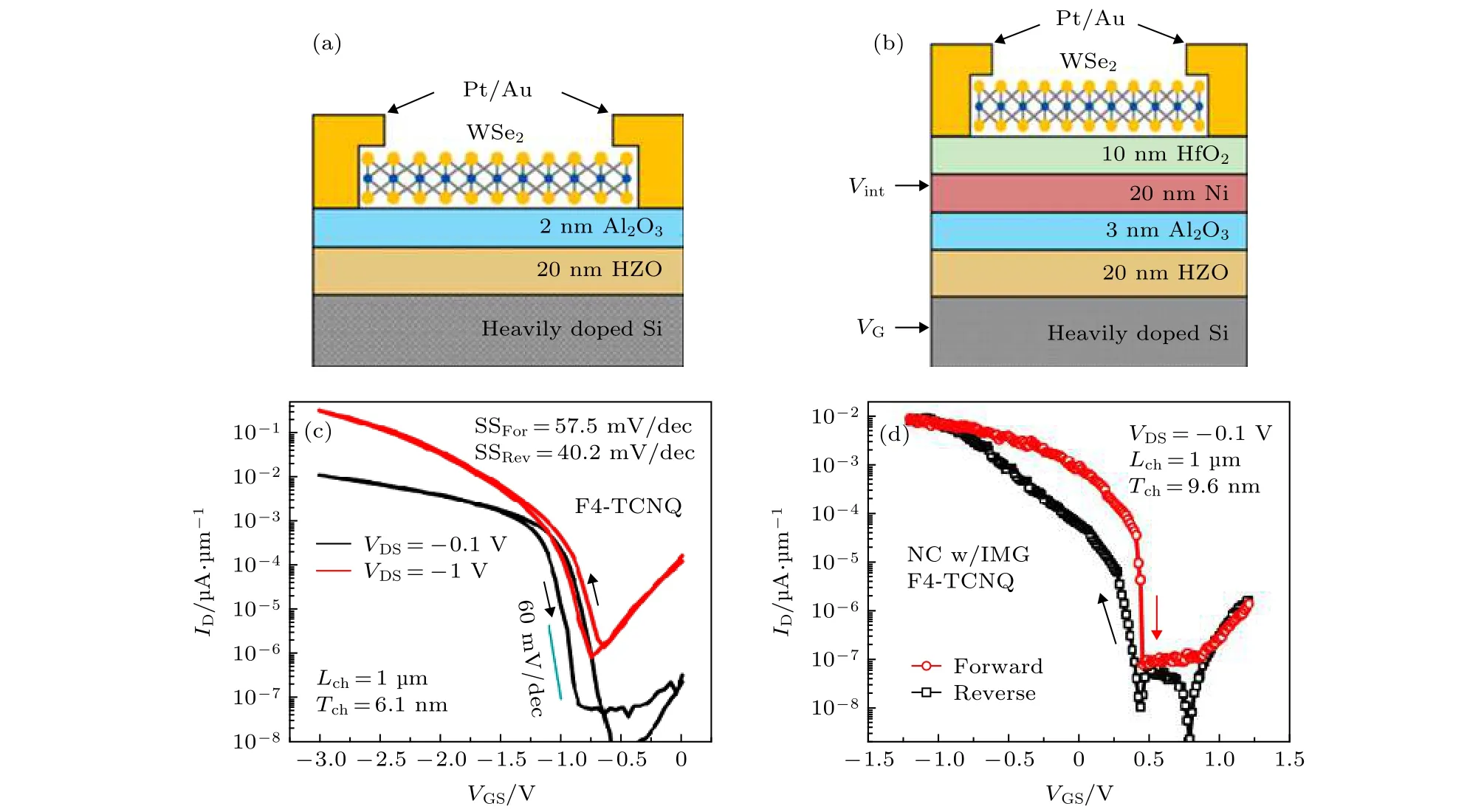

4.2 二維材料溝道

5 總結與展望