一種幅度調制下的成型濾波器實現方法

于茫

摘 要:針對通信系統成型濾波器實現過程中邏輯資源緊張的問題,提出了一種正弦曲線模板方法。利用該方法可以解決FPGA中占用大量LUT和DSP資源的問題,減少有效地址位數,提高尋址速度。該方法利用并行及流水線處理方式,提升了運算速度。最后通過仿真及頻譜儀測試,占用帶寬完全滿足國家標準。

關鍵詞:正弦曲線;成型濾波器;FPGA;MATLAB;仿真;ModelSim

中圖分類號:TP39文獻標識碼:A文章編號:2095-1302(2020)07-00-02

0 引 言

通信系統中信源輸出的信號會經過基帶處理、DAC器件、放大器、調制器、濾波器、衰減器、功率放大器……,最后到達天線負載輸出給信宿。基帶處理過程包括MAC層編碼、數據鏈路層編碼、調制編碼、濾波器設計等。而信源采用濾波器設計用以限制發送信號的帶寬,降低帶外干擾及帶內的碼間干擾[1]。

成型濾波器在FPGA有多種實現方案。

方案一:利用FIR算法,通過MATLAB中的濾波器仿真選取滿足系統要求的濾波器系數,然后把該組系數寫入FPGA中的FIR IP核內并仿真及驗證[2]。

方案二:為了節省邏輯資源,把MATLAB中仿真滿足系統要求而生成的FIR系數歸一化后存入ROM,按照分布式算法,對查找表進行切割處理,累加乘運算得到最終結果[3-4]。

方案三:CIC插值濾波器中只有加法器,無乘法單元,因此進行上變頻處理,滿足DVB-S系統要求[5]。

方案一的實現過程簡單明了,但邏輯的資源消耗最大,且要求FPGA器件具有大量DSP和LUT資源,支持FIR的IP;方案二相比方案一省卻了資源,但在實現過程中需要考慮參數歸一化的字長位數,每級乘法中需要考慮尾數截取的范圍,同時對ROM的存儲深度和存儲字長也有要求;方案三中信號字長位寬的增加會對級聯的加法器性能產生一定限制。隨著濾波器階數的增加,三種方案對邏輯資源的消耗將呈幾何級增加。

本文針對無線通信的幅度調制提出了一種新的成型濾波器設計方法,首先把正弦曲線模板生成的參數存入ROM,然后把調制編碼完成的信號與ROM表中的曲線參數進行累加乘運算,最終輸出波形。該法不僅限制了帶外干擾,節省了資源,而且占用帶寬滿足國家標準[6]。

1 正弦模板算法

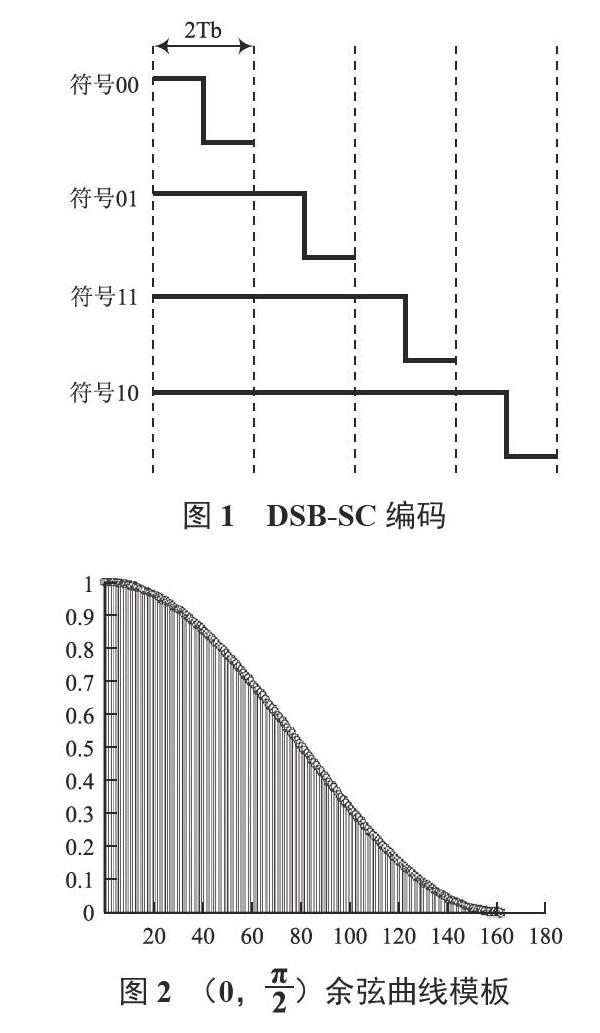

本文所闡述基帶處理系統FPGA的采樣頻率Fs為26 MHz,先對Fb進行TPP編碼(見圖1),Tb=6.25 μs,然后進行DSB調制編碼[6],最后經成型濾波器輸出給14 bit的DAC器件。具體實施步驟如下。

(1)選取標準正弦函數y=cos(t),t取(0,),y值用來表示信號的變化沿。計算Fb信號一個碼元持續時間內所需要的采樣點的個數N=Fs/Fb=162,構造y(n)=acos(2πxn)+b,已知y(0)=1,y(162)=0,a=b。求出y(n)=0.5cos((2πn)/324)+0.5,保留(0,162)區間的y值(圖2)。

把從MATLAB獲取的y(n)值按照16 bit量化取整,處理后的數據寫入FPGA的ROM。

(2)對輸出信號s(t)進行調制編碼,字長寬度與DAC器件保持一致,采用14 bit。碼元1取十進制數4095,二進數補碼為00_1111_1111_1111,碼元0取十進制數低電平值是-4 096,二進數補碼為11_0000_0000_0000。

(3)檢測到s(t)的沿變化(上升沿和下降沿),s(t)延遲兩拍輸出s(t)_2d,比較s(t)和s(t)_2d數值,當數值不同時找到s(t)的變化沿后啟動查找表。找到s(t)的變化沿后把s(t)當前值賦值給s_data_A寄存器,當前值對應的相反電平值賦給s_data_B寄存器。模塊中信號設置均采用16 bit字長,對小于16 bit的寄存器寬度,符號位進行擴展。計算出來的s_data_A與s_data_B的值賦值給s_data_AsubB寄存器。

(4)啟動查找表,每個采樣時鐘ROM地址加1直到N,但在s(t)的變化沿重新為ROM地址置0。每次從ROM讀取出來的數q乘以s_data_AsubB,結果為S_data_dsb_out。調制編碼碼元0按照-4 095取值,所以計算結果S_data_dsb_out需整體向上偏移4 096。

2 仿真及驗證

利用ModelSim對方法進行仿真驗證,成型濾波前后的數據如圖3所示。使用頻譜儀進行占用帶寬測試,如圖4所示。不進行濾波處理的信號占用帶寬約1.6 MHz,將嚴重影響其他信道的設備工作,而濾波后信號的占用帶寬[6]小于標準要求的250 kHz。

3 結 語

本文使用一種正弦模板算法實現成型濾波器的設計,并給出了ModelSim的仿真結果及頻譜儀測試的占用帶寬,驗證了該算法設計的正確性和可行性。采用該方法可以很好地設計無線通信系統中要求的成型濾波器。

參考文獻

[1]樊昌信,曹麗娜.通信原理[M].7版.北京:國防工業出版社,2012.

[2]郭勇,楊歡.基于IP核FIR濾波器的設計與FPGA實現[J].無線電工程,2017(1):79-82.

[3]洪炳镕,趙林.利用系數函數ROM查找表設計的數字濾波器硬件[J].軍事通信技術,1987(4):55-60.

[4]吳鳳輝,遲永剛,鄭宇希,等.一種改進DA算法的成型濾波器設計[J].哈爾濱工業大學學報,2016(5):32-35.

[5]張文坡,常亮,史麗榮.DVB-S中可變插值率CIC濾波器設計及其FPGA實現[J].現代電子技術,2018,41(11):103-104.

[6]中國國家標準化委員會.GB/T 29768-2013,信息技術 射頻識別 800/900 MHz 空中接口協議[S].2013.

[7]張龔,謝文博.基于DSP Builder的FIR濾波器設計[J].物聯網技術,2016,6(5):33-35.

[8]文明.基于FPGA的高速并行濾波器設計與實現[J].現代導航,2018(5):382-386.

[9]邵浩,何忠秋.減少脈沖成形濾波器系數個數的高效算法[J].應用科技,2014(6):35-40.

[10]龔業勇.高清晰度電視VSB調制器及頻譜成形濾波器的設計[D].北京:北京大學,1998.