簡易數字電子時鐘的設計

高偉元,楊 棟,李盼亮,高 晗,丁 鵬

(甘肅農業大學機電工程學院,甘肅 蘭州 730070)

隨著科技水平的不斷發展進步,數字集成電路的應用范圍也越來越廣闊,生活中有許多應用數字集成電路的東西,比如生活中常見的數字電子時鐘。數字電子時鐘具有的基本功能為能準確計時,顯示時、分、秒、可實現自動校正、具有整點報時以及復位功能,數字電子時鐘的設計可以使我們更好的掌握課本內的理論知識,以理論結合實際,應用知識解決日常生活的問題,以及體驗科技給我們生活帶來的便利。

1 設計思路

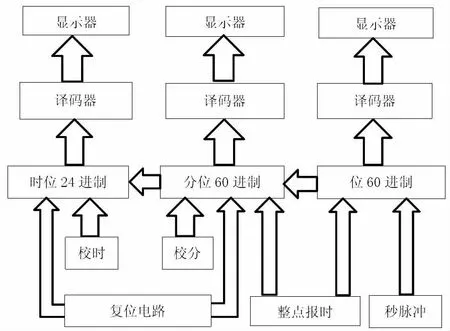

數字電子時鐘的核心就是秒脈沖發生器和進制電路,通過秒脈沖發生器產生的秒脈沖給秒計數電路計數脈沖,然后在通過進制電路給分、時計數電路計數脈沖,進而達到秒計數電路每60s向分計數電路進一位,然后自動清零;分計數電路每60min向時計數電路進一位,然后自動清零;時計數電路每24h自動清零的目的。由于需要校準時間和芯片的鎖存功能,需要為電路的分和時計數電路設計復位功能和校正功能。具體數字電子時鐘框圖如圖1所示。

圖1 電子時鐘框圖

2 模塊電路的設計

2.1 秒脈沖電路模塊

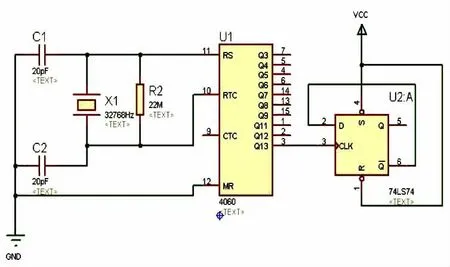

1Hz的計數脈沖是通過32768Hz的石英晶振經過14分頻和2分頻所得,具體電路如圖2所示。

圖2 秒脈沖電路

2.2 秒計數和分計數電路模塊

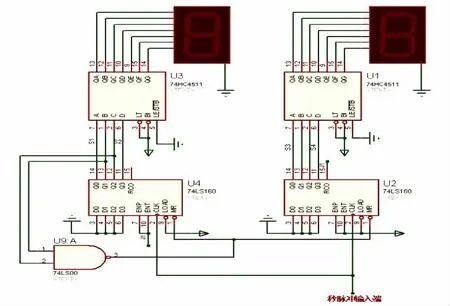

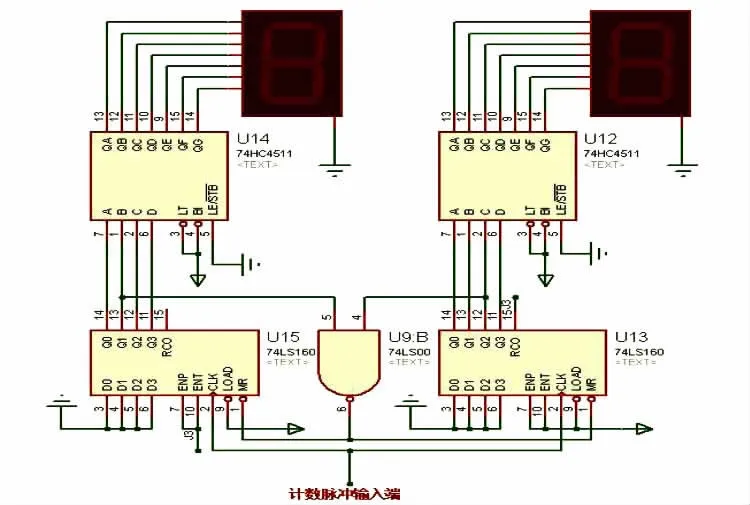

秒計數電路模塊采用反饋清零法,即利用74LS160芯片的異步清零端,當秒計數電路到達60(01100000B)時,用秒計數電路十位輸出端的Q1,Q2的高電平加與非門對兩片芯片的步清零端加低電平進行清零。具體電路如圖3所示。

圖3 秒計數電路模塊

分計數電路模塊和秒計數電路模塊功能類似,接法也類似,均采用反饋清零法。

2.3 時計數電路模塊

時計數電路模塊也采用反饋清零法,即利用74LS160芯片的異步清零端,當時計數電路到達24(00010100B)時,用時計數電路十位輸出端的Q1和個位的輸出端Q2的高電平加與非門對兩片芯片的步清零端加低電平進行清零。具體電路如圖4所示。

圖4 時計數電路模塊

2.4 總體電路設計

通過秒脈沖發生器產生的秒脈沖給秒計數電路時鐘脈沖,秒計數電路在60s的時候給分計數電路一個脈沖的上升沿,讓分計數電路每60s自動加1,進而給分計數電路每60s一個上升沿的時鐘脈沖,然后在通過分計數電路在60min的時候給時計數電路一個脈沖的上升沿,讓時計數電路每60min自動加1,進而給時計數電路每60min一個上升沿的時鐘脈沖。對于復位和校正功能,可以利用74LS160芯片的清零端對分進制電路和時進制電路進行復位,利用秒脈沖給分計數電路和時計數電路進行自動校正。

當數字電子時鐘的分計數和秒計數電路到59(01011001B)分 59(01011001B)秒時,蜂鳴器響起,進行一秒鐘的整點報時操作,即需要兩個四輸入與門和兩輸入與門,當分計數、秒計數電路的十位的Q2、Q0和個位的Q3、Q0同時為高電平時,給蜂鳴器一個高電平,蜂鳴器響起。具體電路如圖5所示。

圖5 總體電路圖

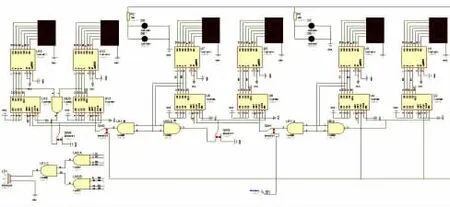

3 電路仿真

在用Proteus電路仿真過程中要注意,由于模擬晶振會占用大量的CPU運算空間,會導致電腦卡頓和仿真的結果不準確,所以在實際仿真的過程中可以將振蕩電路部分取掉,雙擊4060芯片,直接給4060芯片設置輸入脈沖為32768Hz,或者直接給秒脈沖輸入端給軟件的秒脈沖。仿真電路如圖6所示。

圖6 仿真電路圖

4 誤差與分析

1)石英晶振產生的脈沖在經過4060芯片的14分頻之后會出現波形的嚴重失真,會對秒脈沖有較大影響,導致計數出現誤差。經過波形的測試,發現10分頻之后,波形會逐漸出現失真,分頻越高失真越大,所以可以先采用4060芯片對脈沖進行10分頻,然后在對脈沖進行6分頻,以此來改善秒脈沖的波形。

2)在實物仿真中,會發現校時的時候,打開或者關閉單刀雙擲開關,會導致計數數字出現隨意跳動的問題,這是因為開關的抖動,導致校時不準確,因此可以加入施密特觸發器來防止開關抖動造成的校時不準確的問題。