混合可重構的DES算核高效能口令恢復方案

李 斌,周清雷,斯雪明,馮 峰

(1.鄭州大學信息工程學院,河南 鄭州 450001;2.數學工程與先進計算國家重點實驗室,河南 鄭州 450001)

1 引言

數據加密是信息安全的重要手段,密碼技術是網絡安全與保密的核心和關鍵。DES(Data Encryption Standard)作為最有代表性的分組加密算法,包括DES Crypt和3DES,對系統性能要求低,易于軟硬件加速實現,被應用于各種保密通信之中[1,2],如網絡協議、數據加密、智能卡加密、系統加密等。為有效恢復出以DES為核心加密的數據,提供電子取證,并測試DES的各種破譯攻擊,提供安全性研究,對DES算法的計算加速和恢復策略,顯得至關重要。在國外,對DES算法的恢復定制了專用的crack.sh平臺和設備(https:∥crack.sh;https:∥www.sciengines.com),Hashcat(https:∥hashcat.net/hashcat)提供了各種DES密碼算法的恢復計算。在國內,也出現了各種DES專用恢復設備,其以ASIC實現的方式(http:∥www.jn-ljjx.com)極大提高了DES的性能。其次,針對DES算法的高速并行攻擊,利用FPGA可靈活實現多種結構,兼顧性能和功耗[3 - 5],具有明顯優勢。最后,為了提高安全性,DES經常與RSA、Hash函數等聯合使用,包括含有鹽值Salt的DES Crypt和3DES算法,這也給為恢復加密數據帶來了一定困難。

顯然,對于DES的計算,CPU和GPU只能依靠多核心和頻率的提升來加速,且GPU功耗較高。而ASIC僅能支持單個DES應用的恢復,缺失了一定靈活性。其次,DES算法應用眾多,需要靈活的架構和不同恢復策略支持,以提高恢復效率。最后,對于聯合使用多種密碼算法的DES加密機制,是否可繞過部分過程,直接對DES進行破解,并據此恢復其他數據,也亟待研究。

擬態計算依托可重構技術,通過剖析應用的計算特征,依據盡可能高效的原則,構建出合適的處理結構,并隨著處理負荷的變化,主動進行結構變更,以達到“應用決定結構,結構決定效能”的目的。為進一步提高DES的性能和可擴展性,結合擬態計算的思想,本文提出了一種混合可重構的DES算核高效能口令恢復方案。通過對DES算法的深入剖析,形成可重構的算核[6],并以全局異步局部同步GALS(Global Asynchronous Local Synchronous)架構對算核進行互連,建立混合結構,提高了計算速度、能效比和靈活性。其次,優化并設計了高速口令生成算法,以匹配DES的高速口令輸入需求,并針對不同應用提出了各種恢復策略,提高了恢復效率。最后,通過實驗對比了不同計算部件DES算法的性能,并驗證了本文方案的有效性。

2 DES應用及算法分析

2.1 DES應用場景

(1)網絡協議。目前大多數網絡協議中仍以DES為核心加密算法,如LM、NTLM v1、Kerberos 5[7]、VPN、IPSec、FTD等協議。以VPN為例,目前仍有60%以上的VPN使用PPTP隧道協議[8],以DES進行通信加密傳輸。但是,國內出現了大量的“翻墻”軟件,有自由門、極速安全VPN、蝙蝠VPN等。不法之徒利用這些網絡協議,通過私自架設服務器,在國內傳播不良信息,并將重要數據備份在國外服務器上,給電子取證和犯罪審查造成了巨大的阻礙。

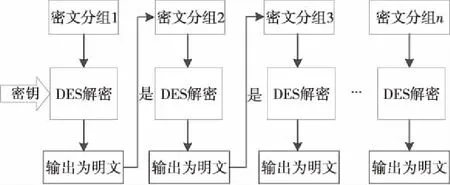

(2)數據恢復。對于DES分組加密算法,有ECB、CBC、CFB、OFB這4種常用加密模式。其中,由于ECB加密模式簡單,且利用并行化處理,目前被廣泛使用。作為DES解密數據的突破口,ECB加密模式也是本文研究的重點。當獲取到DES密文后,可以采用并行逆向計算的方式[9],嘗試用各種不同的口令恢復同一數據段,并以解析到明文輸出為判斷條件,直到找到唯一正確的密鑰。顯然,這對DES加密數據的安全性及其變種改進算法的抗攻擊性測試具有重要意義。

(3)系統恢復。DES算法在智能卡[10]、芯片[11]和操作系統[12]等領域仍被廣泛應用著,以此來實現關鍵數據的保密,如IC卡與POS間的雙向認證、金融交易系統和Linux/Unix系統登錄認證。通過調試跟蹤工具,如OllyDBG、DDMS等,可以跟蹤軟件的內存讀寫和程序執行狀態,進而獲取有用信息,為恢復加密數據提供支持。對于智能卡和芯片,目前則更多是依賴差分功耗分析DPA(Differential Power Analysis)[13]進行破解。但是,DPA也需要輸入n次口令,并對每次產生的功耗進行分析,所以DES的計算性能至關重要。

2.2 DES算法分析

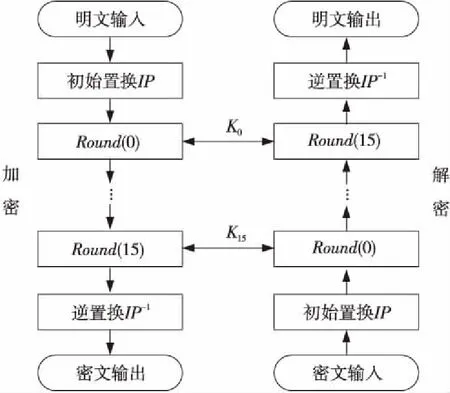

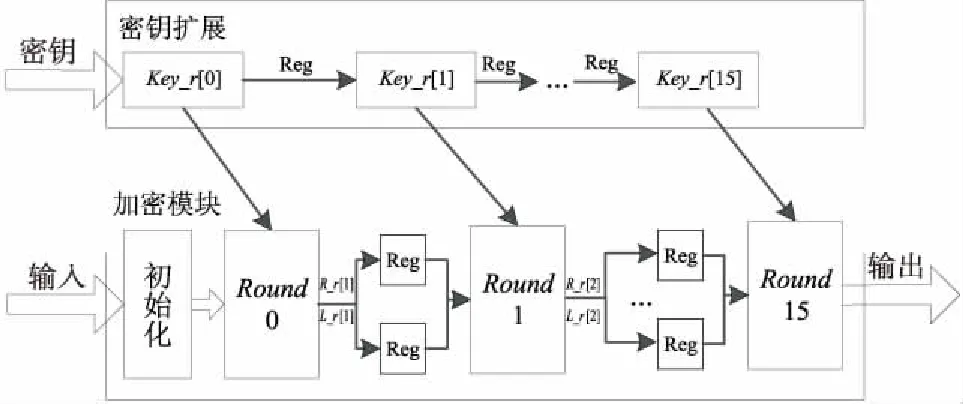

DES算法是一種單密鑰分組密碼算法,以64 bit的密鑰對64 bit的數據分組進行加密,輸出64 bit的密文。明文數據塊首先經過初始置換IP,再使用16個擴展后的子密鑰進行16輪迭代編碼,最后經過一個逆初始置換IP-1,輸出密文,可表述如下:DESm=IP(m)→Round(K0),Round(K1),…,Round(K15)→IP-1。DES解密過程與加密類似,只需要對迭代過程逆序使用子密鑰即可,第1輪使用K15,第2輪使用K14,依次類推,即有:DES-1m=IP(m)→Round(K15),Round(K14),…,Round(K0)→IP-1。DES加/解密流程如圖1所示。

Figure 1 DES encryption/decryption process圖1 DES加/解密流程

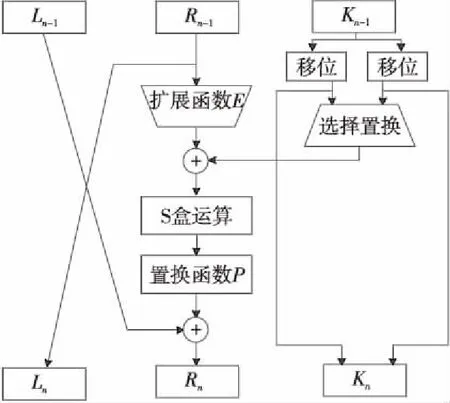

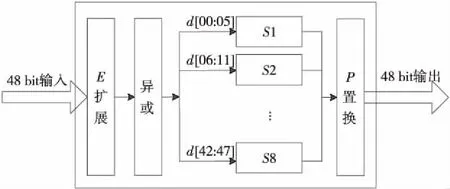

DES加密的核心是16輪迭代循環,64 bit明文在經過初始置換后,被分為L0和R0共2個32 bit的數據塊;然后R0與子密鑰K0進行乘積變換,得到F(R0,K0);再與L0異或得到L0⊕F(R0,K0),隨后使用Ln=Rn-1,Rn=Ln-1⊕F(Rn-1,Kn-1)重復迭代過程。其中,F包括:擴展函數E、按位異或、S盒運算和置換函數P這4個功能模塊。對于密鑰擴展,56 bit的密鑰被分成2個28 bit的半密鑰,每個半密鑰經過循環左移處理,并通過選擇置換,產生48 bit的子密鑰。DES單輪加密流程如圖2所示。Rn-1先由擴展函數E擴展到48 bit,然后再與擴展后的48 bit的子密鑰Kn-1按位異或,得到8組6 bit的數據。這8組數據再進入6 bit輸入4 bit輸出的S盒S1,S2,…,S8,得到32 bit的數據。最后經過置換函數P,得到32 bit的輸出。

Figure 2 Single round encryption process圖2 單輪加密流程

由以上分析可以看出,DES算法具有如下特點:(1)數據通路簡單,都是位級的線性變換;(2)16輪核心迭代完全相同,且每輪迭代均為線性變換;(3)DES是分組密碼算法,參與運算的數據塊前后沒有相關性[14],因而可以將循環展開,形成流水線;(4)DES每輪參與運算的子密鑰可以提前生成。

雖然基于FPGA對DES算法有了眾多優化[15-17],但其僅優化了算法本身,并未對算法在各種應用場景中的使用進行分析。為進一步提高DES算法的應用靈活性和可擴展性,本文結合擬態計算算核的設計思想,以有限規模的硬件解決DES算法多領域應用,并采用全局異步局部同步GALS的架構,實現芯片級的多維可重構,進而高效地實現DES各種應用的口令恢復。

3 方案優化與設計

3.1 算核模型

擬態計算以算核為基本功能單元,其規模受解算目標的應用驅動,可按應用所需重構成不同數量、粒度和功能的算核,進而可獲得更高的單元利用率,兼顧高效計算和靈活性。因此,算核是一種計算粒度可變的計算結構,對于提高計算系統的效能和資源利用率具有重要意義。

算核的計算模型可表示為:CK=(VE,ED,PR,ME,CO,GR),其中VE={ve1,ve2,…,ven},表示算核的集合;ED={edij|edij=vei,vej,vei,vej∈VE,1≤i,j≤n},稱為有向邊集,表示算核之間數據依賴先后關系及串并行關系;PR={pr1,pr2,…,prn},代表算核的串行計算量;ME={me1,me2,…,men},代表算核所需內存容量或硬件寄存器資源;CO={co1,co2,…,con},代表每條邊eij上的通信量;GR={gr1,gr2,…,grn},表示計算粒度,粒度大小受輸入輸出數據和串、并行實現方式影響。

圖3所示為算核重構的示意圖。其中I1~I5為輸入算核,A1~A4、D1~D4、F1~F4為中間算核,O1~O5為輸出算核。通過每條路徑上算核的重構連接得到了一定的運算功能。那么,針對DES口令恢復算法,以片內邏輯塊、IP核、功能函數、算法等形成算核,利用FPGA細粒度可重構器件,通過觸發器FF(Flip Flop)和查找表LUT(Look Up Table)等實現串并混合的計算結構,可獲取更好的可擴展性和執行效率。

Figure 3 Reconstruction of the computing kernel圖3 算核重構

3.2 整體架構

DES口令恢復算法主要由口令生成、DES算核和對比邏輯構成,并由主控模塊與上位機通信,完成任務的初始化與配置。其中DES算核支持動態可重構,可根據用戶配置信息,重構成不同功能和結構的算核。同時,采用GALS架構放置多個算子模塊,各個算子獨立執行,可支持同一掩碼多個任務或不同掩碼同一任務等多種恢復模式。當某個算子找到正確口令時,由多路復用器MUX(MUltipleXer)進行仲裁輸出,并傳遞給上位機,其整體框架如圖4所示。

Figure 4 Password recovery overall framework of DES computing kernel圖4 DES算核口令恢復整體框架

基于算核模型,采用粗細粒度的混合結構,以重構IP置換、密鑰拓展、輪運算等模塊,形成串行、并行、流水線等多種執行方式,以及加密、解密等多種不同的DES算核。同時,配以不同的口令生成策略和對比模塊,滿足不同應用的計算需求。基于擬態計算的DES口令恢復,其流程如算法1所示。

算法1DES口令恢復算法

輸入:FPGA配置信息、任務信息和口令策略。

輸出:正確密鑰key。

1.由FPGA配置信息,載入對應的比特流文件,并完成任務和口令的配置。

2.While(HasNextKey)do

3.key=GenerateNextKey(口令策略);

4.d=DES(key);

5.If( 對比驗證通過 )

6.Returnkey;

7.EndIf

8.EndWhile

從算法1中可以看出,以DES為核心算法的口令驗證流程較為簡明。通過口令生成模塊產生key,并代入DES算核逐一驗證,如果計算出的結果和驗證串相同,即找到了對應的正確key。

3.3 DES算核優化

為滿足不同應用的需求,這里對DES算核的串行實現進行了優化,以減少資源占用,提高布線成功率。同時,使用全流水架構實現DES的高速并行計算,以空間換取時間,最大化算法的吞吐量和性能。

3.3.1 串行結構

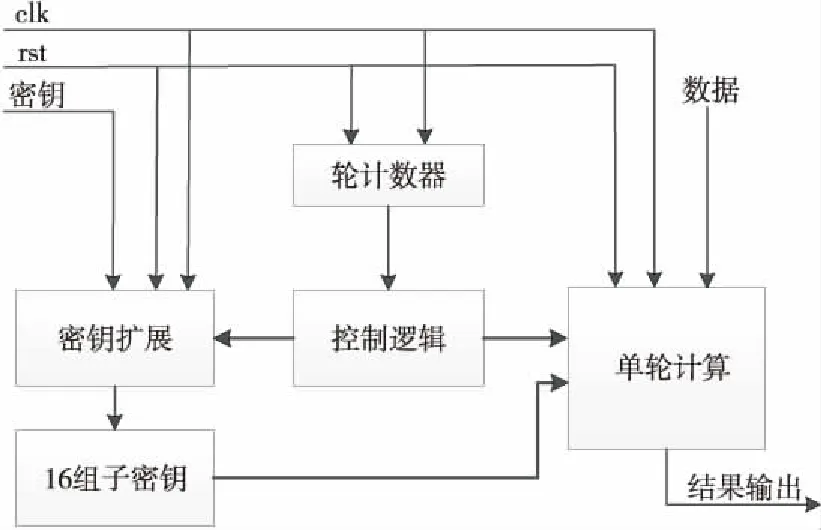

由于DES解密是加密的逆過程,只有密鑰使用的順序相反,中間操作完全相同。因此,為實現統一的DES加/解密算法,在密鑰擴展時,只并行計算一次,并得到16組Key。然后,通過狀態機控制,根據當前迭代的輪數,選擇對應的Key。這樣不僅節省了資源,還簡化了設計。圖5所示為DES串行加/解密的結構圖。

Figure 5 DES serial structure圖5 DES串行結構圖

圖5中,密鑰拓展采用assign連續直接賦值,并由16個寄存器數組保存,可在1個時鐘周期內執行完成。單輪計算也采用assign賦值,可在1個時鐘周期內完成,并將結果保存在寄存器中,由狀態機控制,向下傳遞。整個DES加/解密串行需要17個時鐘周期,其中數據輸入占用1個時鐘,計算過程占用16個時鐘,并在最后一次計算完成后,直接輸出結果。

3.3.2 全流水架構

在使用FPGA以全流水架構實現DES算法時,需要將單輪計算實例化16次,并使用寄存器數組存儲每輪的計算結果,然后順次傳遞。由于參與運算的數據和密鑰是連續的,因此在密鑰擴展時,需要在1個時鐘周期內生成16組數據對應的密鑰,并參與16輪計算。如圖6所示,采用位寬為48 bit的寄存器數組Key_r[0:15]存儲擴展后的密鑰,數據在經過初始化后,由寄存器數組L_r[0:15]和R_r[0:15]依次進行存儲。

Figure 6 DES pipeline architecture圖6 DES流水線架構

當流水線開始工作時,在第1個時鐘周期對第1組數據進行初始化和密鑰擴展,生成Key_r[0],然后參與第1輪運算,產生結果L_r[1]和R_r[1]。在第2個時鐘周期,Key_r[0]會進行密鑰擴展生成Key_r[1],并和L_r[1]、R_r[1]參與第2輪計算,產生結果L_r[2]和R_r[2]。同時,第2組數據會進行初始化和密鑰擴展操作,生成新的Key_r[0],并參與第1輪計算,產生新的L_r[1]和R_r[1]。以此類推,直至16輪迭代計算完成,然后依次輸出16組數據的加密結果。顯然,每組數據都要經過16個時鐘周期才能計算出結果。但是,當流水線滿負荷工作時,每個時鐘周期都會產生輸出,相比于串行DES算法,其處理速度提高了16倍,具有很高的計算性能。

由于FPGA屬于位級計算部件,非常適合與或非、異或、移位等操作。而DES運算中,正好含有大量的位級運算,但在每輪運算中需要8個S盒參與運算,S盒的優化顯得十分重要。S盒是一個十分復雜的非線性函數,可以使用多重case,以LUT和MUX進行實現;還可以使用卡諾圖進行適當化簡,得到邏輯表達式,然后使用硬件語言描述;或者直接使用BRAM(Block Random Access Memory)進行S盒存儲。前2種方法規模較小,適宜特定硬件平臺。第3種方法隨著硬件工藝的提升,對擁有豐富BRAM資源的FPGA非常適用。

本文采用第3種方法,以BRAM存儲S盒,不僅可以充分利用FPGA資源,還可平衡LUT、寄存器和BRAM的使用,有利于FPGA布局布線。優化后的DES單輪結構如圖7所示。

Figure 7 DES single round structure圖7 DES單輪結構

3.4 高速口令生成算法

文獻[18]通過對大量真實口令集的統計分析,指出口令的頻率分布符合Zipf分布,為評估口令猜測攻擊模型提供了理論基礎。由于DES破解速度十分快,結合口令的Zipf分布,只需采用窮舉策略,即可滿足恢復的要求。如果采用字典進行破解,傳輸帶寬將成為計算瓶頸。同時,由于字典通常只包括常見的弱口令,且無法涵蓋所有口令,必然存在口令遺漏的情況。本文方案優化并實現了掩碼攻擊和奇偶概率攻擊,縮短了計算時間。

3.4.1 掩碼攻擊

對于DES算法,其口令長度固定為8 B,因此采用全空間的掩碼攻擊。相比于暴力窮舉攻擊,掩碼攻擊可對口令的每一位進行配置,使攻擊更加有效。為充分發揮FPGA計算效率,使多個算子并行計算,將掩碼口令劃分為2部分,其中一部分用來產生口令前綴,另一部分用來窮舉余下的口令。這樣,就可將不同的口令前綴分配到多個算子,并將口令前綴和余下窮舉的口令組合形成完整的口令輸入DES進行計算。其過程如算法2所示。

算法2掩碼口令生成算法

輸入:口令配置信息pwd_config[7:0][0:7],pwd_fix[0:7]。

輸出:候選口令password[7:0][0:7]。

1.Fori= 0 to 7do

2.password[i] = Null;

3.index[i] = 0;

4.Endfor

5.While(True)do

6.Fori= 0 to 7do

7.If(pwd_fix[i] == 1)∥該位為已知明文

8.password[i] =pwd_config[i];

9.Else∥全空間窮舉

10.password[i] =AllCharSet(index[i]);

11.EndIf

12. 判斷第i位索引index[i]是否需要進位或歸0

13.Endfor

14. 輸出password;

15. 如果index[0,…,7]全為0,跳出While循環;

16.EndWhile

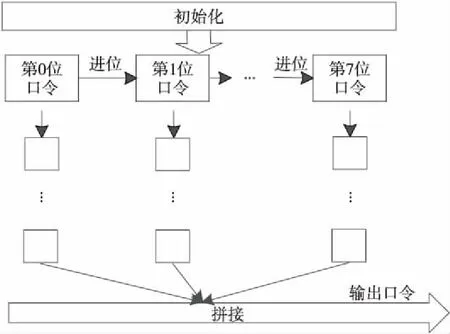

顯然,算法2可以以流水線的方式實現,在算法中的第1~4行可在1個時鐘周期內完成初始化,第6~13行可使用8個模塊并行計算,并將口令第i(0≤i≤7)位對應的字符同時輸出,然后在1個時鐘周期內完成拼接并輸出,如圖8所示。

Figure 8 Mask password generation pipeline 圖8 掩碼口令生成流水線

此外,口令生成的速度在某些情況下會成為計算的瓶頸,需要進行深度優化。本文采用2級流水線的方法,將原流水線隔斷為2個獨立的流水線,1個模塊工作在低頻,另1個模塊工作在高頻,并將低頻流水線生成的口令,通過異步FIFO傳輸給高頻模塊,高頻模塊再對低頻模塊生成的口令進行補位擴充操作,并產生最終的口令。經該方法優化后,掩碼攻擊最高每秒可產生400M個口令。

3.4.2 奇偶概率攻擊

對于DES算法的64 bit密鑰,其中8 bit是奇偶校驗位,只有56 bit參與計算。因此,只需從0到256-1窮盡56 bit所有密鑰,即可達到百分之百破解率。進一步,結合統計學分析,采取先窮舉偶數,再窮舉奇數的規則,以優先恢復出其中的部分口令,達到事半功倍的效果。同時,放置多個算子并行計算,每個算子分配不同的密鑰前綴,以提高攻擊性能。奇偶概率攻擊口令生成算法如算法3所示。

算法3奇偶概率口令生成算法

輸入:口令配置key_config[17:0]。

輸出:候選口令key[55:0]。

1.key_high[17:0] =key_config[17:0];

2.key_low[37:0] = 0;

3.While(True)do

4.If(key_low== 38’hFFFFFFFFE)

5.key_low= 1;

6.Else

7.key_low=key_low+2;

8.EndIf

9.If(key_low== 38’hFFFFFFFFF)

10.Break;

11.EndIf

12.key= {key_high,key_low}。∥拼接生成key

13.EndWhile

3.5 恢復策略

3.5.1 協議密鑰恢復

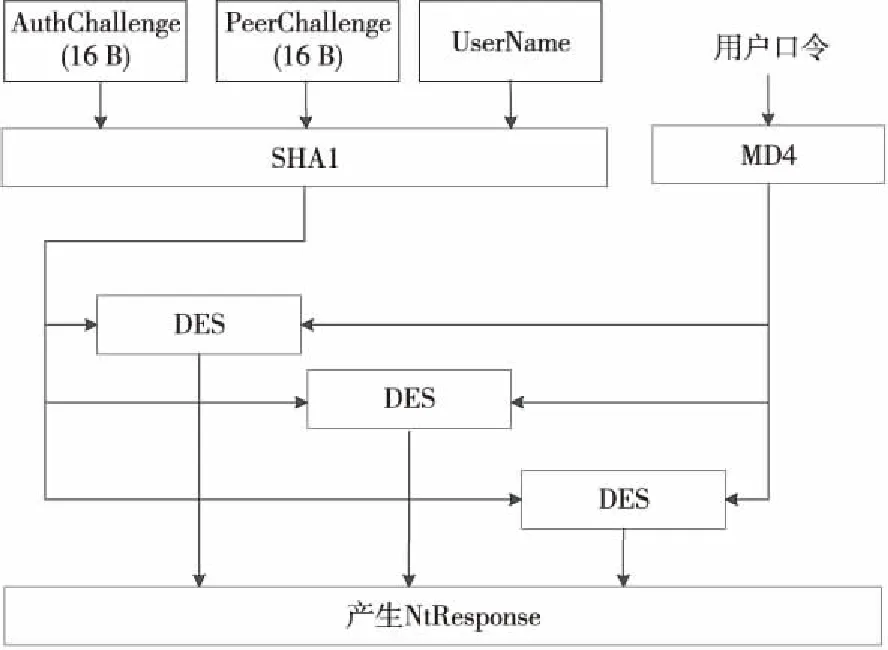

網絡協議授權過程中,Hash+DES的方式仍被廣泛應用著,它以用戶口令輸入Hash函數,并將產生的結果經過處理作為DES加密的密鑰,以此保護用戶數據安全。如圖9所示,詳細給出了VPN PPTP使用微軟Ms CHAP v2身份認證的過程。

Figure 9 Ms CHAP v2 authentication process圖9 Ms CHAP v2認證過程

客戶端和服務端會分別由Ms CHAP v2身份認證過程產生各自的NtResponse,并在服務端進行對比驗證,如果2個NtResponse一致,則驗證成功,否則驗證失敗。從圖9中的流程可以看出,在截獲協議交互信息后,可以通過窮舉用戶口令產生NtResponse,并與截獲的NtResponse進行對比,如果一致,則找到了正確的口令。進一步,由于用戶口令范圍極廣,16 bit的全字符空間約有PwdNum=9516個口令,而DES密鑰空間為KeyNum=256,顯然,PwdNum要遠大于KeyNum,采用奇偶概率攻擊是十分有效的方法,且對DES密鑰空間搜索可以達到100%的破解率。由此,還可直接對3個DES進行密鑰奇偶概率攻擊,還原MD4哈希值,并據此恢復其他加密數據。最后,對諸如此類的網絡協議,如LM、NTLM v1、Ms CHAP v1、Kerberos 5等,都可以用類似方法進行密鑰恢復。

3.5.2 數據密鑰恢復

對于使用DES加密數據的恢復,在得到足夠多密文的情況下,可以用口令逐一嘗試,并以輸出明文為判斷條件,當連續得到np組明文時,即找到了唯一的正確口令。對于DES ECB模式的口令恢復如圖10所示。

Figure 10 DES ECB decryption diagram圖10 DES ECB解密示意圖

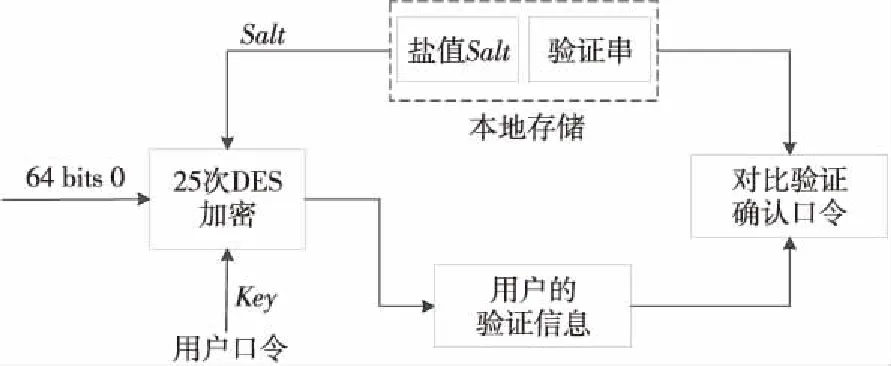

由于ASCII碼表中有256個字符,其中95個為可顯示字符,則DES解密全為明文的概率為q=(95/256)8≈3.60×10-4。全口令空間大小為488(去除奇偶校驗位重復的字符),只有一個正確口令的概率為p=1/(488)≈3.55×10-14。如果連續解密成功4組數據,有q4≈1.67×10-14,且q4 在服務器領域,Linux/Unix系統由于其開放性、公開性和可移植性等優勢,被絕大多數用戶使用。但是,其帶來諸多便利的同時,安全問題也隨之而來。其中DES Crypt作為用戶身份認證加密算法仍被使用著。DES Crypt算法使用鹽值Salt作為參數,完成對用戶口令的加密。例如,特征串“s2JQ85JElCMeU”,其中“s2”為Salt值,“JQ85JElCMeU”為加密后的驗證信息。整個過程需要25次DES迭代,如圖11所示。 Figure 11 Linux/Unix user password verification process圖11 Linux/Unix用戶口令驗證過程 由于DES口令輸入為8個字符,因此用戶口令空間為958,可以使用掩碼進行全空間搜索,以達到100%的破解率。進一步,對循環迭代使用DES或DES Crypt算法的其他軟件、密碼機或系統都可進行類似的口令恢復。 對于以DES為核心的口令恢復算法,可以用四元組表示PWRC={PWD,CORE(DES),CMP,SRP},其中,PWD表示口令,可以是掩碼攻擊、奇偶攻擊或字典攻擊產生的口令;CORE(DES)表示以DES為核心的算法,可以是DES的變形算法或其他算法的組合,如DES Crypt、Hash+DES、2次DES迭代組合等;CMP表示結果對比;SRP表示存儲正確口令。 為了有效支持各種應用場景的DES恢復,對PWRC進行可重構設計,如圖12所示。圖12中深灰色表示粗粒度可重構模塊[19],各模塊間由FIFO互連。采用基于算核的映射方式,在PWD、CORE(DES)、CMP各階段選擇不同的算核進行靈活重構,形成應用。其次,改變FIFO位寬和深度銜接各個模塊,完成異步時鐘域的同步和數據傳輸。最后,以參數配置的形式實例化多個算子,適配多種FPGA并提高了資源利用率。針對網絡協議、數據和系統的口令恢復,給出如下幾種重構結構,如表1所示。 Table 1 Reconstruction structure description of each application表1 各應用重構結構說明 本文實驗的硬件平臺是4核FPGA集成加速卡,芯片型號為XILINX公司的xcku060,其查找表LUT資源為331 680,FF寄存器資源為663 360。軟件平臺為集設計、仿真、綜合、布線、生成于一體的Vivado軟件。實驗通過對DES口令恢復算法的各模塊進行深度優化,給出了資源占用及各種重構方案,使最終算法在吞吐量、運行速度、資源利用率等方面有了較大的提升。其次,與CPU、GPU和其他方案進行了性能對比分析。最后,給出了各種應用及口令策略的恢復效率分析。 表2所示為DES口令恢復算法主要算核的資源占用情況。從表2中可以看出,各模塊占用資源較少,完全滿足算核的設計要求,可重構成各種結構,并布局多個模塊并行計算,滿足不同應用的需求。表3所示為4種典型應用的DES算核重構方案及實現情況。從表3中可以看出,每個應用不僅充分利用了FPGA資源,工作頻率還均在360~400 MHz,具有非常高的性能。 Table 2 Implementation of each module表2 各模塊實現情況 Table 3 Typical application of DES computing kernel reconstruction and implementation表3 典型應用DES算核重構及實現情況 首先,給出了本文DES實現方案與其他方案的對比,如表4所示,其中吞吐量的計算公式為:吞吐量=輸入位寬×頻率。從表4中可以看出,本文實現的17級流水線DES方案較其他方案具有更高的吞吐量。 Table 4 Comparison of the scheme in this paper with other schemes表4 本文方案與其他方案對比 其次,以VPN DES為例,使用FPGA加速卡與使用CPU、使用GPU在性能、功耗和能效比方面進行了對比,結果如表5所示。其中CPU型號為NVIDIA Intel i5-7500(4核,3.40 GHz),GPU為GTX 1080(2 560核,1 860 MHz),軟件測試平臺為hashcat v3.60。能效比計算公式為:能效比=性能/功耗,顯然能效比越高越好。 Table 5 Performance comparison among platforms FPGA,CPU and GPU 表5 FPGA、CPU和GPU平臺上性能對比 從表5中可以看出,使用FPGA的速度分別是使用CPU和GPU的2 353.14倍和14.19倍,使用GPU的速度是使用CPU的165.81倍。使用FPGA的能效比分別是使用CPU和使用GPU的584.96倍和11.02倍,使用GPU是使用CPU的53.08倍。無論是從速度還是能效比,使用FPGA都要優于使用CPU和GPU。一方面由于DES算法主要為邏輯運算,非常適合FPGA實現。另一方面,基于算核的設計方法充分利用了FPGA資源,提高了FPGA計算頻率,具有明顯的優勢。 最后,給出了單個FPGA隨DES算核個數增加及加速卡隨FPGA個數增加的功耗變化情況,如圖13和圖14所示。從圖13和圖14中可以看出,板卡空載功耗約為64.48 W,每個算核的功耗約為0.3 W,整個加速卡的功耗約為276.32 W。顯然,基于算核的實現方式,在保證了DES性能的同時具有較低的功耗,適合大規模使用。 Figure 13 FPGA power consumption changes with the increasement of DES computing kernels圖13 FPGA隨DES算核增加的功耗變化 Figure 14 Accelerator card power consumption changes with the increasesment of FPGAs圖14 加速卡隨FPGA個數增加的功耗變化 針對DES ECB加密模式,使用掩碼模式攻擊,對數據進行恢復。當連續np組解密后的數據都為明文時,即可判斷解密成功。表6給出了各種口令組合使用單個加速卡掩碼攻擊的恢復時間。 Table 6 DES ECB mask attack recovery time表6 DES ECB掩碼攻擊恢復時間 從表6中可以看出,對于常用的數字+字母組合口令,使用加速卡進行恢復,僅需要8.88 s的時間,對數字+字母+特殊字符的組合口令,最長也僅需要177.90 s。顯然,對于DES ECB加密模式數據的恢復,本文方案基本可以做到實時恢復,效率十分可觀。 對于Linux/Unix系統口令的恢復,每次初始化計算時會先將口令左移1 bit,但參與DES Crypt計算的仍為56 bit有效密鑰。這樣,可以統計分析移位后的字符,并直接使用移位后的字符作為新的字符表,再去除其中重復的字符,以此來減少口令空間。同時,由于DES Crypt需要循環迭代25次,使用掩碼攻擊,其恢復時間會增加25倍。 搭建服務器集群,每個服務器配有8個加速卡,以VPN PPTP為恢復對象,采用奇偶概率攻擊,窮舉0~256-1所有56 bit密鑰,表7所示為隨著服務器個數的增加,其恢復時間的變化。 Table 7 Password recovery time on server cluster 表7 服務器集群上口令恢復時間 從表7中可以看出,當服務器集群規模為16時,加速卡可在0.58 h內窮盡56 bit全部密鑰空間,達到100%的恢復效率。而crack.sh系統含有48塊 XILINX Virtex-6 LX240T FPGA,需要26 h才能窮盡56 bit密鑰空間,文獻[4]在120塊XC7S100 FPGA規模下,也需要19 h。對大量VPN的恢復任務,本文服務器集群可保證短時間內的有效恢復,為電子取證提供了強力支撐。 本文提出的混合可重構的DES算核多應用口令恢復方案,以DES算核為研究對象,設計并優化了串行、全流水結構的DES算核。然后,基于統計學原理,給出了掩碼攻擊和奇偶概率攻擊,提高了應用口令恢復效率,并給出了不同應用場景下的恢復策略。最后,通過深入剖析各應用的特征,以DES算核的變結構組合,適配各種應用。實驗結果表明,該方案可重構出的DES算法在性能、資源、功耗等方面具有明顯優勢,較使用CPU和GPU有10倍以上的提升。同時,結合口令恢復策略,可在較短時間內恢復出原始口令。 進一步,基于算核的設計思想,為定制ASIC芯片提供了理論基礎和技術支持。可將口令生成、密鑰擴展、串行DES、流水線DES、對比模塊等算核在ASIC芯片內部規劃布局,通過配置信息完成相應算法的切換,并獲取更高的計算性能。基于算核可重構的ASIC DES算法實現,也是下一步的研究方向。3.5.3 系統口令恢復

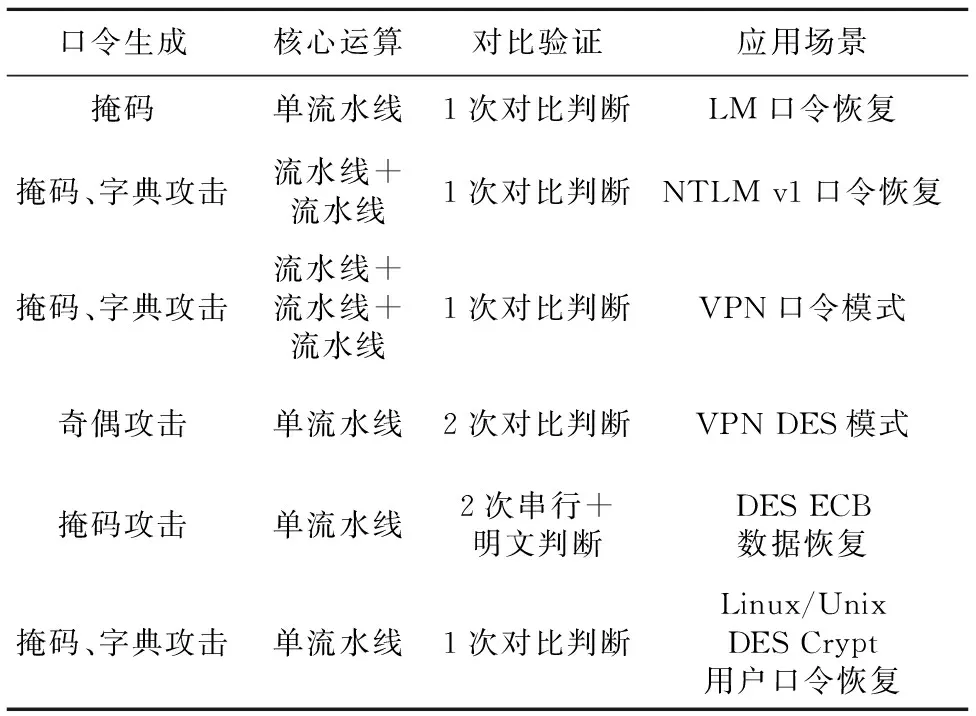

3.6 DES算核的重構

4 實驗結果與分析

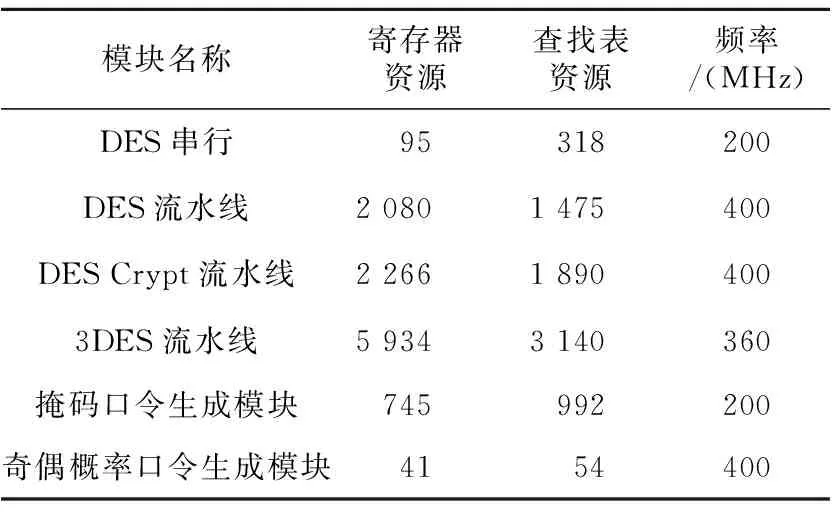

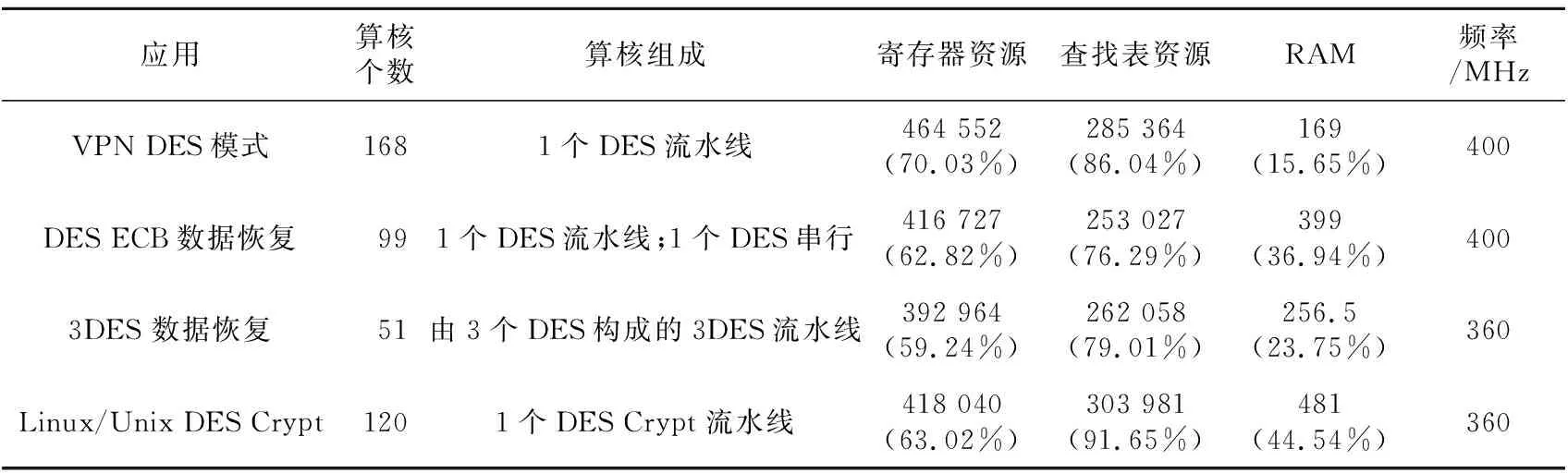

4.1 各模塊實現

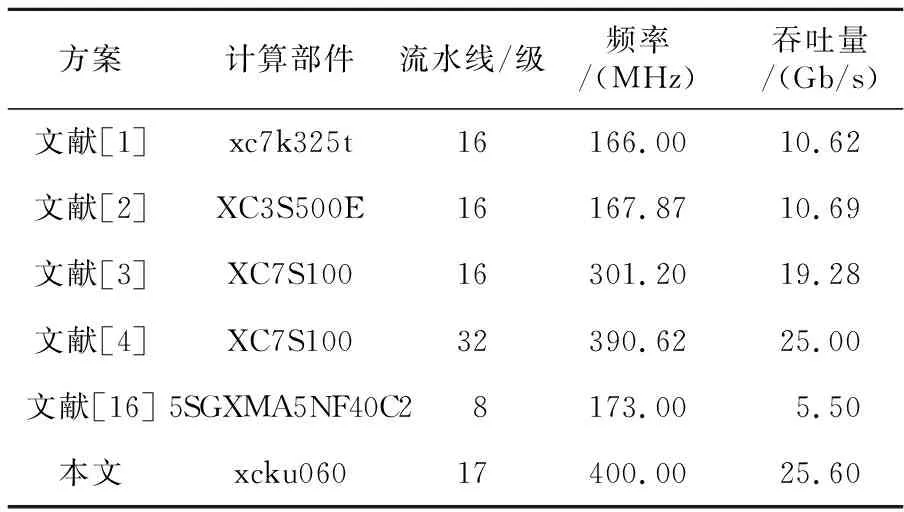

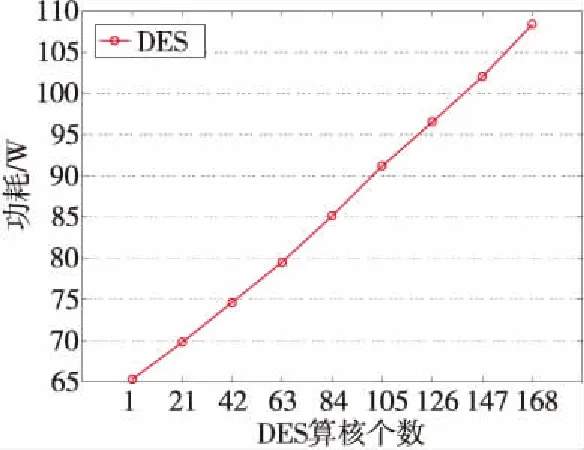

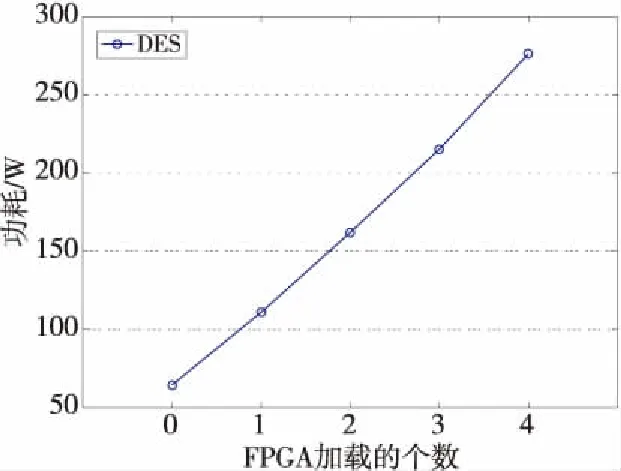

4.2 性能對比分析

4.3 口令攻擊分析

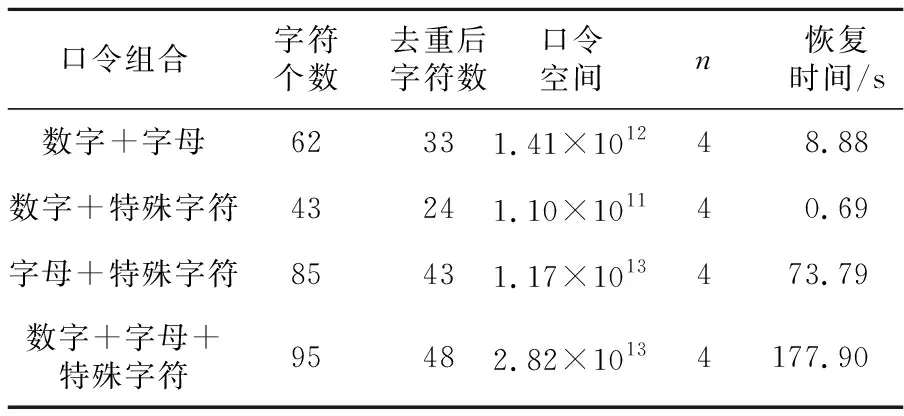

4.3.1 掩碼模式攻擊

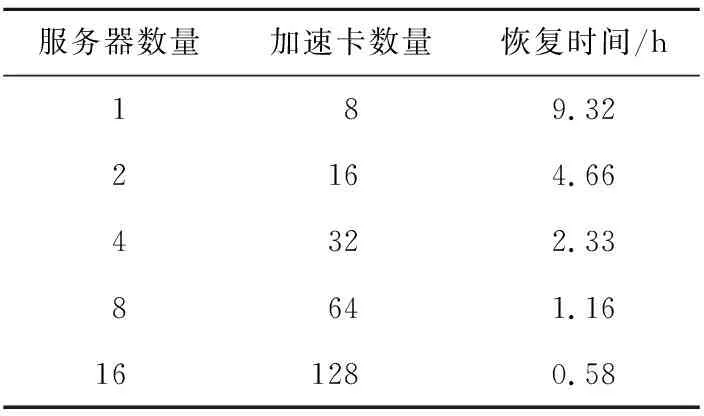

4.3.2 奇偶概率攻擊

5 結束語