裝配應力對芯片可靠性的影響分析

黃煒,吳昊

(中國電子科技集團公司 第二十四研究所,重慶 400060)

引言

半導體器件發生失效往往伴隨有多種應力的綜合影響,其中通常是機械應力起到先決和誘導的作用[1]。

隨著器件尺寸的不斷縮小,硅有源區面積的縮小,機械應力對器件的影響越來越顯著,產品在圓片加工、芯片封裝、元器件裝配等過程中均會受到機械應力,可能引起芯片可靠性甚至電性能的惡化。且芯片裝配后出現的失效,由于無法完整將芯片從組件上分離,給故障定位帶來一定困難。

本文選取兩種典型半導體芯片裝配過程中機械應力導致電性能失效的案例,對機械應力引起芯片失效的分析方法進行剖析,并提出芯片裝配過程中注意事項。

1 失效案例1

失效樣品為某款TR組件波控電路芯片,該芯片在裝配后首次上電測試出現多只電性能異常,表現出反轉功能異常,且單只故障現象均不一致。同批次芯片在以往裝配過程中未出現過電性能異常。

為定位本次多只芯片裝配后電性能異常故障點,選取1只典型樣品,進行外觀目檢、EMMI定位、微探針測試、IV測試、OBIRCH定位、SEM檢測、FIB等故障定位過程,定位故障點,分析排查故障原因。

首先采用較低放大倍數(10倍)光學顯微鏡對其進行外觀檢查,無異常;然后對失效品進行密封、X射線檢測,均合格,表明失效品封裝無缺陷;排除封裝方面問題后;對其進行機械開封,暴露出內部芯片。

1.1 內部目檢

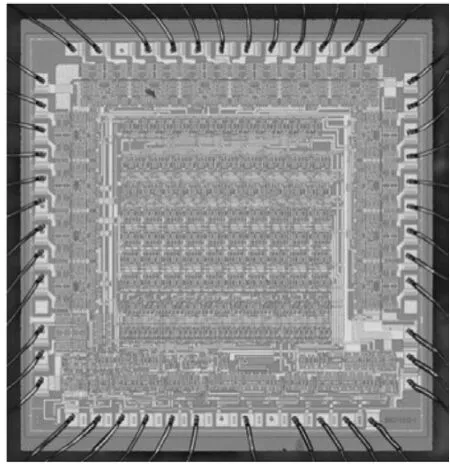

為觀察開封后內部芯片結構是否存在異常,采用較高放大倍數(100~500倍)光學顯微鏡對失效芯片進行內部目檢,未發現明顯異常,檢查結果如圖1、圖2所示。

1.2 EMMI定位

為檢測故障芯片內部故障點,在加電條件下采用微光顯微鏡((Emission Microscope, EMMI)高靈敏度光傳感器來檢測芯片表面發出的光子,輸出光發射圖像,將該圖像與candence中芯片的版圖、線路圖進行對比,確定異常發光點位置,通過逐一排查,結合失效模式,推測發光點原因,判斷發光點是否故障點,完成故障定位。據此來達到定位缺陷的目的。

通過對比試驗圖像與芯片版圖結構、線路結構發現,在正常上電情況下,失效芯片較正常芯片多觀測到1個異常發光點,如圖3所示,該異常點位于芯片二級鎖存器某中間級。

1.3 微探針IV測試

結合線路原理與EMMI試驗結果,初步定位故障處結構,采用微探針測試該二級鎖存器故障點處對VDD端口IV特性,掃描不同電平下試驗點電流值,與合格產品對比,如圖4所示,發現試驗點對VDD存在異常低電阻特性,表明該二級鎖存器處存在漏電通路,無法實現正常電平翻轉功能。

1.4 OBIRCH故障定位

激光熱效應激勵電阻變化方法(Optical Beam Induced Resistance Change,OBIRCH)是采用激光束加熱芯片,通過檢測試驗點電流變化情況,定位漏電流在芯片上的具體物理位置。為準確定位該二級鎖存器結構中PMOS、NMOS晶體管故障部位,對其OBIRCH結果分析,發現故障點處PMOS器件的柵極與VDD之間存在一個漏電流點,OBIRCH結果如圖5所示。

1.5 異常漏電流點SEM檢查

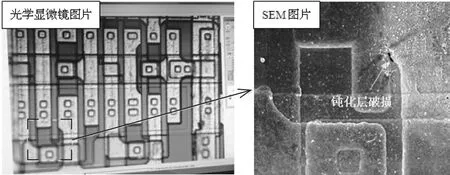

考慮光學顯微鏡放大倍數級及清晰度的限制,選擇采用掃描電子顯微鏡(Scanning Electron Microscope,SEM)針對OBIRCH異常漏電流點區域進行檢查,芯片放大至10 000倍可明顯發現一個鈍化層破損,如圖6所示。

1.6 FIB剖面結構分析

圖1 失效樣品外觀

圖2 失效樣品外觀

圖3 失效樣品EMMI結果

圖4 故障點對VDD IV特性

鈍化層覆蓋于芯片最表面,為檢測該破損鈍化層縱向深度,判斷其對芯片功能的影響,針對異常漏電流點處的鈍化層破損,采用(聚焦離子束Focused Ion beam,FIB)進行切面分析。切面分析顯示在鈍化層破損周圍產生微裂紋,其中一條微裂紋斜向上延伸到鈍化層頂部,另一條微裂紋斜向下延伸到有源區,導致PMOS的柵極與VDD產生漏電流,如圖7所示。

1.7 小結

由故障定位結果可知,本次故障芯片鈍化層破損產生的微裂紋延伸到有源區,導致PMOS的柵極與VDD產生漏電流,芯片表現出電性能異常。

2 失效案例2

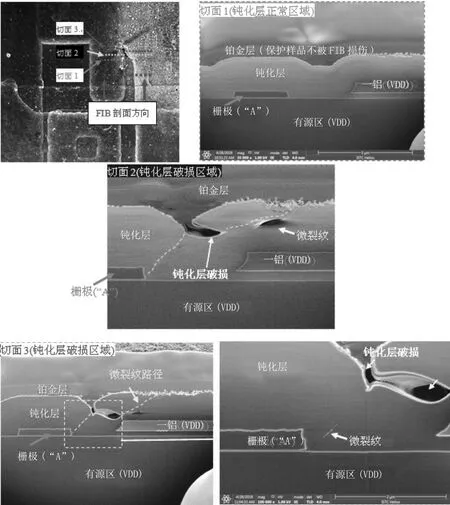

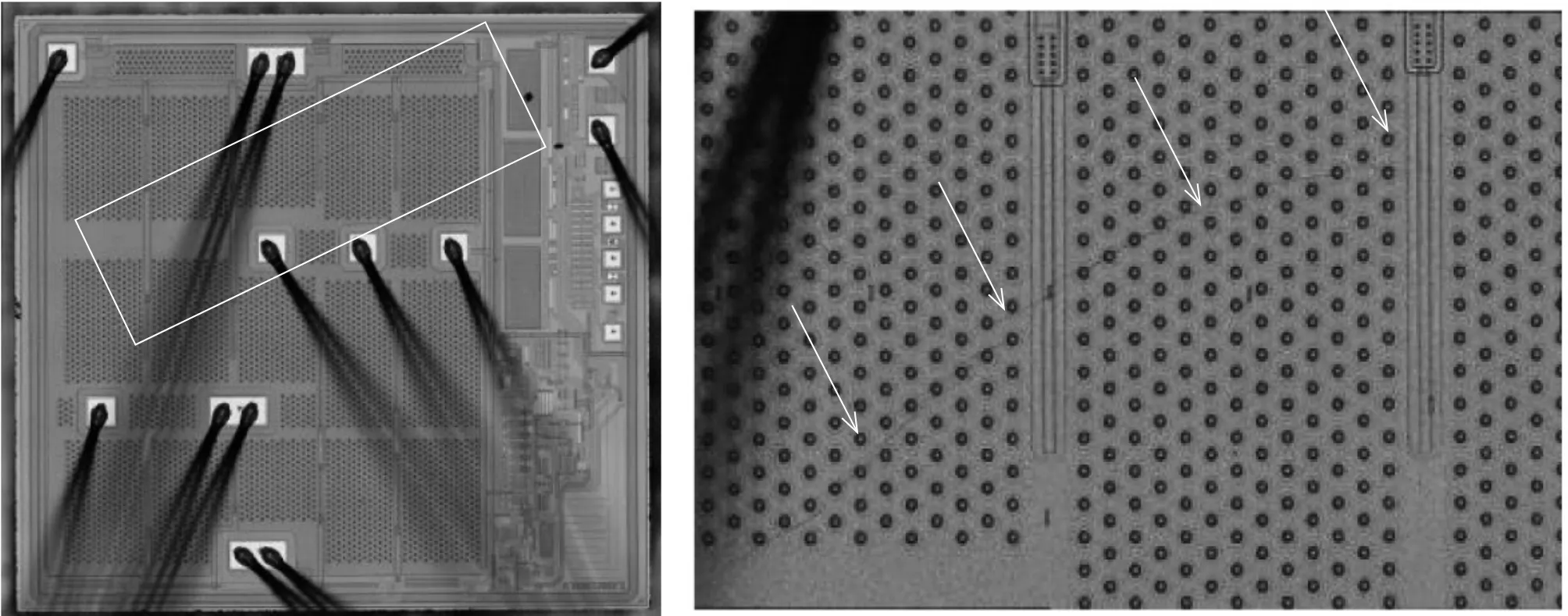

失效樣品為某款大電流低壓差線性調整器產品,該產品在圓片電探針測試、封帽前產品電測試均合格,封帽后溫度循環、恒定加速度試驗后出現大比例電性能失效,且故障現象不一致,大多數故障產品均表現出靜態電流增大現象。

該產品采用FPP1010-05管殼封裝,內部采用鉛錫銀焊料燒結,對多只故障產品開帽后進行外部目檢(光學顯微鏡,放大倍數100-500倍),發現芯片表面均存在不同程度的微裂紋,位置隨機[2,3],選取1只樣品裂紋如圖8所示。

圖5 故障點OBIRCH結果

該裂紋導致芯片內部器件間隔離度下降,電性能上體顯出漏電流增加,其機理與失效案例1相似,但故障現象更為明顯。

3 原因分析

從機械可靠性的角度考慮,影響產品失效的因素可概括為應力和強度,其中應力是引起產品失效的各種因素的統稱,強度是產品抵抗失效的各種因素的統稱。通常作用于器件的應力包括載荷(力、力矩、轉矩等)、位移、應變、溫度、磨損量、電流、電壓等,而強度即包括承受上述各種形式應力的能力[2]。

圖6 異常漏電流點處的鈍化層破洞

圖7 鈍化層破損區域FIB剖面結構分析

圖8 鈍化層破損區域

通過對故障芯片經歷進行排查,分析導致本次芯片鈍化層破損產生的微裂紋的原因是貼片、燒結過程中應力不匹配導致。貼片、燒結過程異常機械或溫度應力作用于芯片,施加在鈍化層上,甚至延伸至鈍化層下的金屬層,由于金屬層可塑性較鈍化層強,因此金屬層不易產生裂紋,但金屬層的形變將加劇鈍化層產生裂紋。

該種異常的機械應力可通過調整貼片設備吸頭力、吸頭尺寸、燒結溫度等參數進行改善[4]。

4 結論

由前述兩個失效案例可知,對于機械應力引起產品電性能失效,其特點是電性能失效故障現象不一致,同批次加工產品故障比例較高,通常伴隨著靜態電流(漏電流)增大現象[5,6],即芯片內存在漏電通道。

故障分析首先需定位漏電流點,對于光學顯微鏡無法直接定位的芯片,結合EMMI、SEM、OBIRCH等定位手段,定位故障點后,根據故障形貌,綜合產品經歷,分析失效原因,并進行相應整改,優化工藝結構。