TFT-LCD白點不良機理研究及改善

劉 信, 高玉杰, 郭 坤, 楊 志, 程 石, 林鴻濤, 毛大龍,盛子沫, 趙 劍, 吳 偉, 郭會斌, 江 鵬

(1. 武漢京東方光電科技有限公司,湖北 武漢 430040;2. 北京京東方顯示技術有限公司,北京 100176)

1 引 言

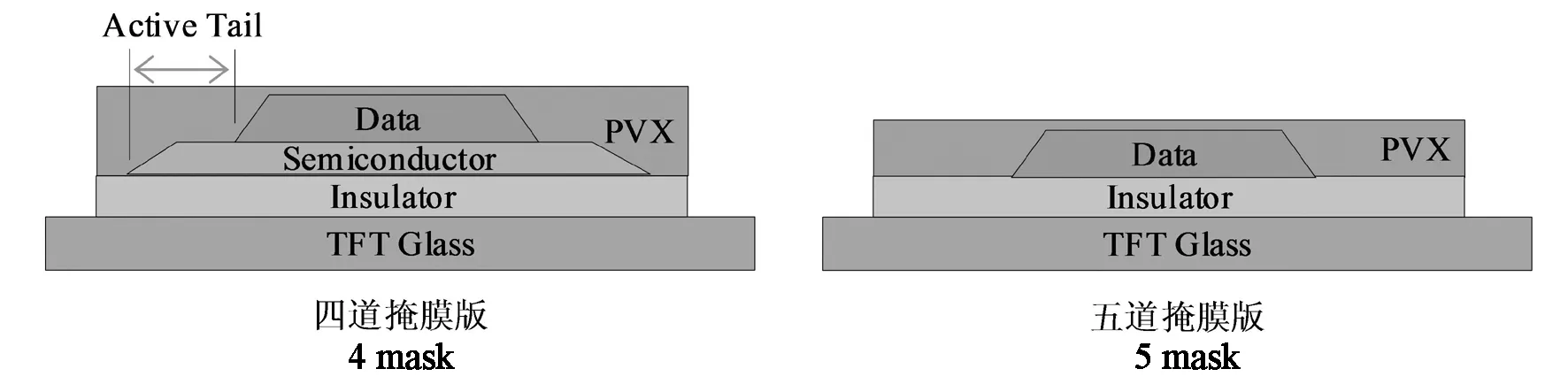

隨著生活水平提升,人們對顯示器的品質需求越來越高,高分辨率、高刷新頻率、高對比度、高亮度等高端產品逐漸占領市場。高端產品開發必然帶來成本和周期的上升,進而影響企業收益,因此各企業不斷采取各項措施來降低產品開發和生產成本[1-2]。四道掩膜版工藝是各工廠為降低生產成本而普遍采用的一種曝光工藝,相比于五道掩膜版工藝,減少了一道光刻工藝,即有源層和數據線采用一道掩膜版完成,用半曝光替代全曝光,減少工藝流程,提升工廠產能,增加產品收益。但四道掩膜版工藝會使數據線下方存在有源層,在顯示器使用時,光照會使有源層導電,等效于數據線寬度增加[3-4]。高端產品的設計,在考慮工藝波動的情況下,其走線寬度和間距均處于極端值,四道掩膜版工藝帶來的實際數據線寬度增加加重了液晶顯示器的負載,影響產品畫質及良率,本文研究的白點不良就是其中的一例。

對于任何一種高端顯示器的開發,產品性能和良率一樣重要。本文主要研究了四道掩膜版工藝導致白點不良的原因,通過光照和高溫實驗,明確了不良發生的機理。同時研究了柵極和源極的耦合電容及子像素存儲電容對白點不良的影響,通過工藝調整相應的幾何尺寸和膜厚,解決白點不良,為后續高端產品的四道掩膜版設計及工藝提供了可行性方案。

2 實 驗

實驗選擇尺寸和分辨率相同的模組,將其分為4組,用于光照實驗。選用不同工藝模組產品A、B、C、D研究柵/源極電容與白點的關系;模組產品B、E用于研究子像素存儲電容與白點的關系。

2.1 直流實驗

TFT-LCD正常顯示時,柵極和數據信號均為交流電。對于數據信號,本實驗將柔性電路板除掉,酒精清洗各向異性導電膠,在焊盤(Bonding Pad)涂上銀漿,外接直流電源,可實現數據信號為直流電。該樣品采用柵極驅動功能集成在陣列基板上的GOA(Gate Driver on Array)設計[5-6],將GOA所有信號CLK/STV/VDDO/ VDDE/VGL等設置為高電壓,可實現柵級直流信號。實驗時觀察并記錄白點現象等級。

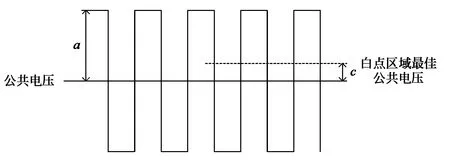

2.2 光照實驗

第1組(1-1#~1-3#)為參考組,TFT朝下放置(正常放置),被背光源照射;第2組(2-1#~2-3#)彩膜朝下放置(翻轉放置),被背光源照射;第3組(3-1#~3-3#)在正常放置情況下,將白點區域下方用黑色墊片遮擋,樣品背光源光照;第4組(4-1#~4-3#)在正常放置情況下,將白點以外其他區域下方用黑色墊片遮擋,樣品背光源光照。以上實驗每隔24 h進行觀察,以上分別記錄白點現象等級。

2.3 高溫存儲實驗

將完成光照實驗的第1組樣品(1-1#~1-3#)放入高溫爐中,溫度為150 ℃,每隔2 h,進行現象觀察,記錄白點現象等級。

3 結果與討論

3.1 電信號對白點的影響

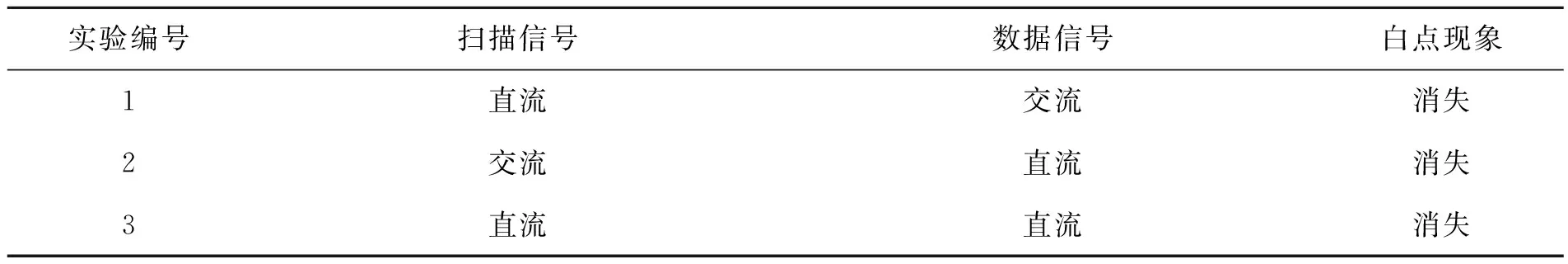

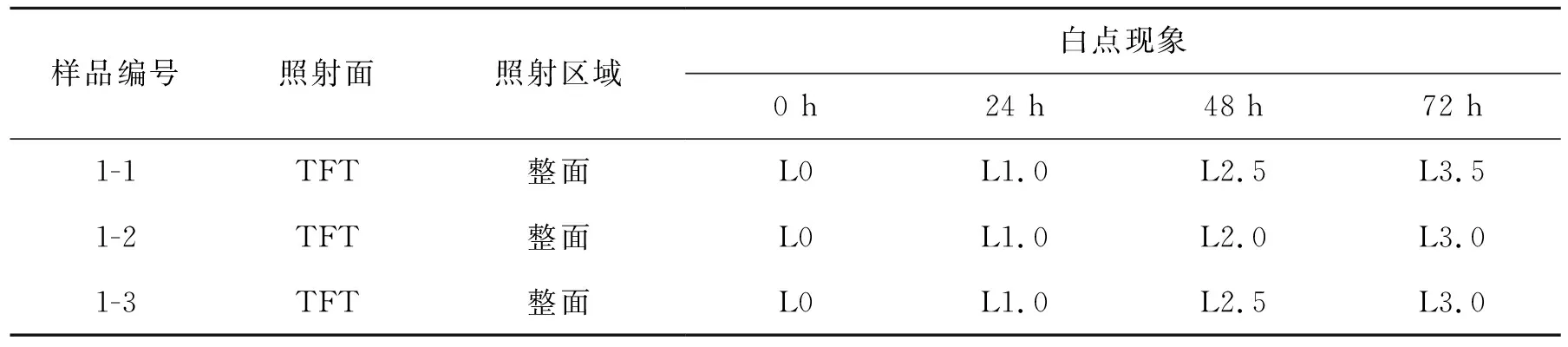

為研究掃描/數據信號對白點不良的影響,本文設計了不同組合的信號加載到顯示屏上,觀察白點現象,其結果如表1所示。

表1 掃描/數據信號與白點現象的關系Tab.1 White dot phenomenon vs. gate/data signal

從表1可以看出,施加直流掃描信號時,白點消失。相比于交流,直流無電壓跳變,可以消除數據線與掃描線的電容對像素電壓的影響,即反沖電壓(ΔVp)[7-8]的影響。施加直流數據信號時,白點消失,此時掃描信號仍為交流,ΔVp的存在會影響像素電壓,但數據信號處于直流,即使掃描信號處于關閉狀態,由于漏電流的存在,像素仍處于一定的充電狀態,可以抵消大部分由于ΔVp不同導致的像素電壓差異。另外,同時給掃描/數據線施加直流信號,白點依然消失。以上實驗結果說明,白點不良是由于存在ΔVp,導致白點與其他區域的像素電壓不同,使其最佳公共電壓不一致,從而出現黑白的差異,導致白點,以下做詳細說明。

如圖1所示,公共電壓的電位是依據屏內多數像素閃爍程度確定的,可以認為對于多數像素,公共電壓的電位是在綜合考慮了ΔVp和漏電流的基礎上,保證了像素的正負幀電壓的對稱(大小設為a)。但對于白點區域,由于該區域的ΔVp與其它區域存在差異,因此白點區域與其他區域的最佳公共電壓存在差異(設為c,可正可負)。

圖1 像素與公共電極間的電壓示意圖Fig.1 Schematic illustration of the voltage between the pixel and the common electrode

本樣品為常黑模式,像素電極與公共電壓之間的有效電壓越大,像素的亮度越高。因此,對于正常區域和白點區域,像素亮度可以分別用式(1)和式(2)定性地表示。

正常區域亮度:

a2+a2=2a2

(1)

白點區域亮度:

(a+c)2+(a-c)2=2(a2+c2)

(2)

顯然,白點區域亮度高于正常區域亮度,因此該區域發白。

3.2 光照/溫度對白點的影響

我們研究了照射不良樣品的不同區域,白點的變化情況,并對其中部分樣品進行了高溫存儲實驗,結果見表2和表3。

表2 光照條件與白點現象的關系Tab.2 White dot phenomenon vs. light conditions

續 表

表3 高溫老化與白點現象的關系Tab.3 White dot phenomenon vs. high temperature aging

從表2、3可以看到,TFT朝下放置狀態下被背光源照射,白點不良逐漸減輕;彩膜朝下放置狀態下被背光源照射,白點不良無變化。同時,背光源照射白點外區域,白點現象無變化;照射白點區域,白點現象消失。從中不難看出,不良受彩膜基板黑矩陣下TFT基板上有源層光照導電性能的影響。將白點消失樣品進行高溫存儲,白點均復現。從該實驗可以看出,白點區域有源層受Staebler-Wronski效應影響,改變有源層的導電性,ΔVp發生變化又得到了還原,使白點在光照下消失,在高溫下復現。

Staebler-Wronski效應現象為a-Si∶H在可見光持續照射下,暗電導率和光電導率會隨時間的增加而下降,在150 ℃以上的溫度下退火可恢復。采用電子自旋共振進行測試,發現在光照情況下,a-Si∶H中的懸掛鍵(Dangling Bond,DB)信號強度增加。針對非摻雜的a-Si∶H,導帶的電子遷移率比空穴電子遷移率大得多,電流主要通過電子傳輸形成。隨著光照的進行,DB密度逐漸增加,靠近費米能級的深能級和其態密度均增加,導帶內躍遷電子的壽命減少,導致光導率減小。在a-Si∶H中,光的電導率與遷移率和載流子壽命的乘積成正比,光的照射對遷移率的影響非常小,因此載流子壽命的減少是光電導率降低的主要原因。另外,在光照射下,躍遷的帶間距內態密度增加。在光照射前,躍遷帶間距中央靠近導帶側的費米能級向價帶方向移動,所需的活化能增加,因此暗電導率也減少。

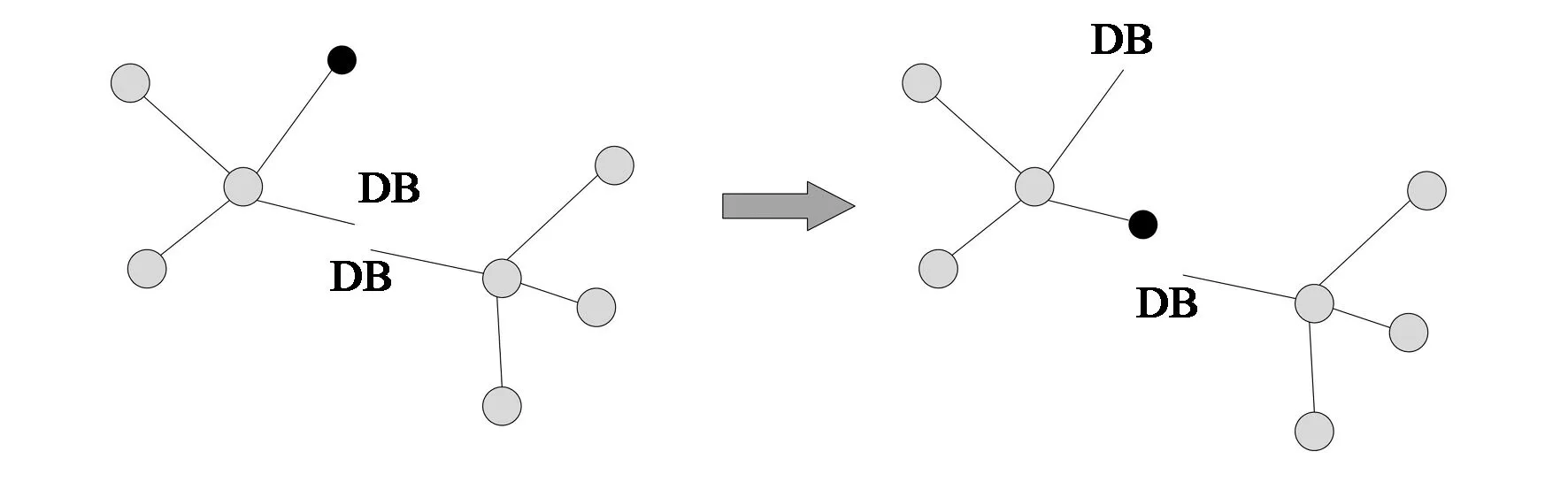

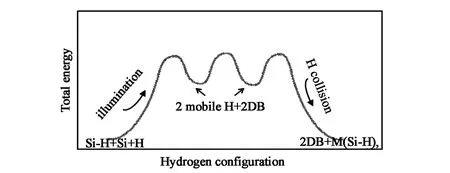

對于Staebler-Wronski效應產生的機理,國內外主要有3種解釋模型。一是弱鍵斷裂模型(圖2),其機理為Si—Si弱鍵中的Si原子存在一個Si—H鍵,當兩個載流子在弱Si—Si鍵附近復合時,其中部分能量以聲子的非輻射方式釋放出來,使膜中的Si—Si弱鍵斷裂,形成兩個臨時懸掛鍵,為了達到更穩定的亞穩狀態,鄰近原子會在小范圍內發生重構,其中一個Si原子的Si—H轉向懸掛處,從而增加了懸掛鍵缺陷態密度[8]。二是“氫玻璃”模型(圖3),在光照下,H從Si—H鍵中脫離出來并在a-Si∶H中移動,這種移動的H造成了弱Si—Si的熱力學斷裂,從而形成兩個懸掛鍵缺陷,增加了懸掛鍵缺陷態密度[9-10]。三是氫碰撞模型(圖4),光照射下,誘導Si—H鍵斷開,形成1個懸掛鍵和1個可移動的H原子,當兩個可自由移動的H原子在運動過程中在弱Si—Si鍵附近發生碰撞時,弱的Si—Si鍵斷裂,形成了亞穩的不可移動的化合物(Si—H)2,增加了2個懸掛鍵,因此造成了H的聚集和懸掛鍵的增多,導致懸掛鍵缺陷態密度增加[11]。

圖2 弱鍵斷裂模型中 Staebler-Wronski效應微觀機理Fig.2 Microscopic mechanism of the SW effect in SJT model

圖3 “H 玻璃”模型中懸掛鍵形成示意圖Fig.3 Schematic illustration of dangling bond formation corresponding to H-glass model

圖4 氫碰撞模型示意圖Fig.4 Schematic illustration of hydrogen collision model

3.3 柵/源極電容和存儲電容對白點不良的影響

通過實驗研究,白點是由于該區域的ΔVp與鄰近區域差異導致,結合ΔVp的計算公式:

(3)

對于掃描信號確定的產品,ΔVp主要受到TFT基板各耦合電容、液晶電容及存儲電容的影響,其中柵/源極耦合電容的影響較大。本文主要研究了柵/源極電容和存儲電容對白點不良的影響。

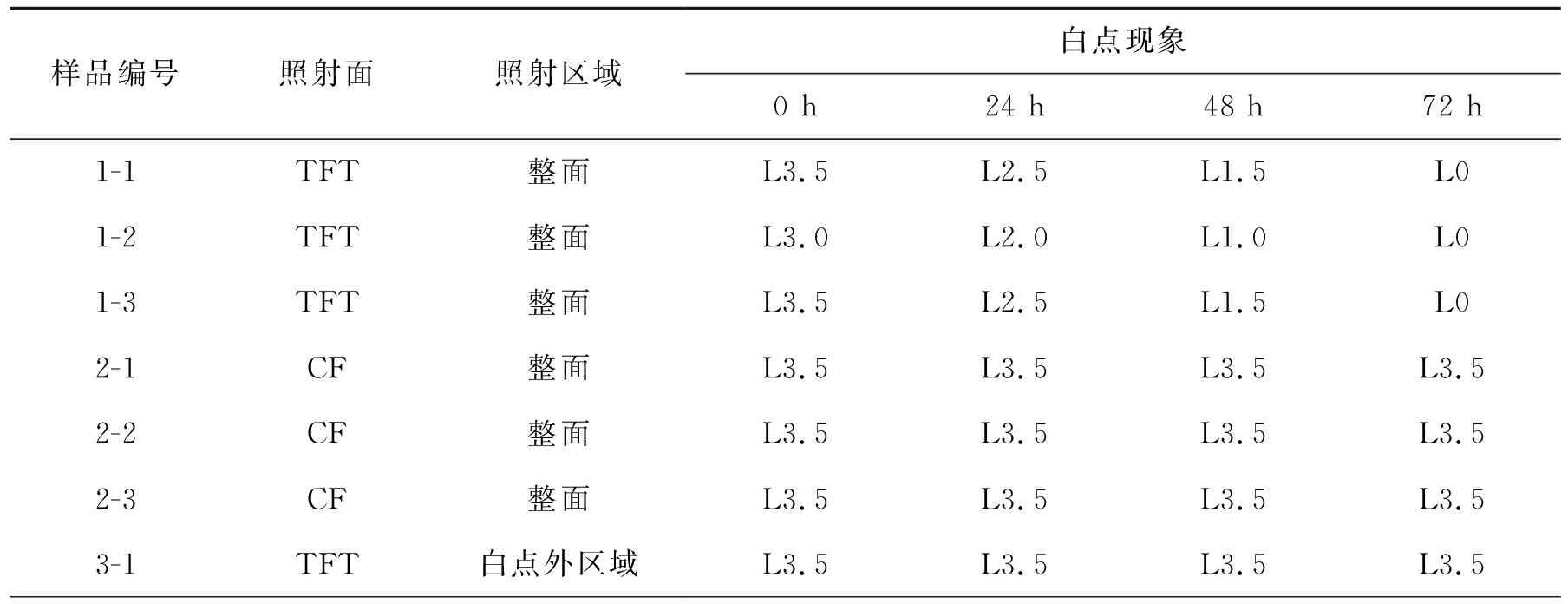

3.3.1 柵/源極電容對白點不良的影響

柵/源極電容為TFT開關舌頭處源極與柵極的耦合產生,對于四道和五道掩膜版,如圖5所示,主要區別為數據線下方是否存在有源層,結合平行板電容公式:

(4)

圖5 信號線下有無半導體截面圖Fig.5 Sectional view of the data line with/without amorphous silicon layer

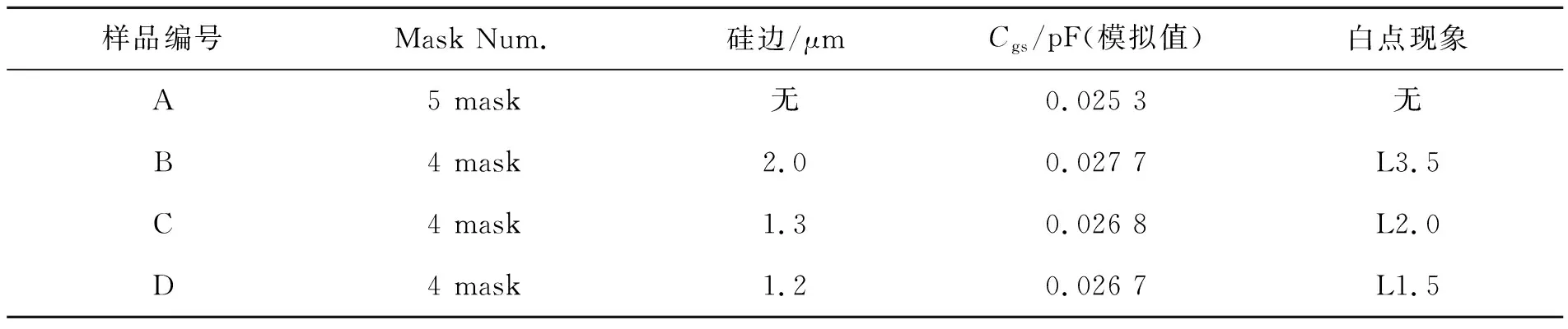

其大小主要受到源極寬度和柵絕緣層厚度影響,源極寬度體現為數據線側邊保留的有源層,即硅邊。本文主要研究了不同的硅邊寬度對白點的影響,其結果如表4所示。

表4 硅邊寬度與白點現象的關系Tab.4 White dot phenomenon vs. active tail width

從表4可以看出,隨著硅邊的減小,由于數據線與掃描線的交疊面積減小,使柵極和源極耦合電容減小,白點逐漸減輕,如果有源層和數據層采用兩道掩膜版,即無硅邊,可以完全消除白點不良,但采用兩道掩膜版,將增加開發成本,減少工廠產能。因此,兼顧經濟效益,選擇方案為有源層和數據線采用一道掩膜版,降低硅邊寬度,硅邊寬度受限于工藝,會存在一個極限值。在本實驗中,硅邊為1.2 μm時,白點基本不可見,品質可接受。

3.3.2 存儲電容對白點的影響

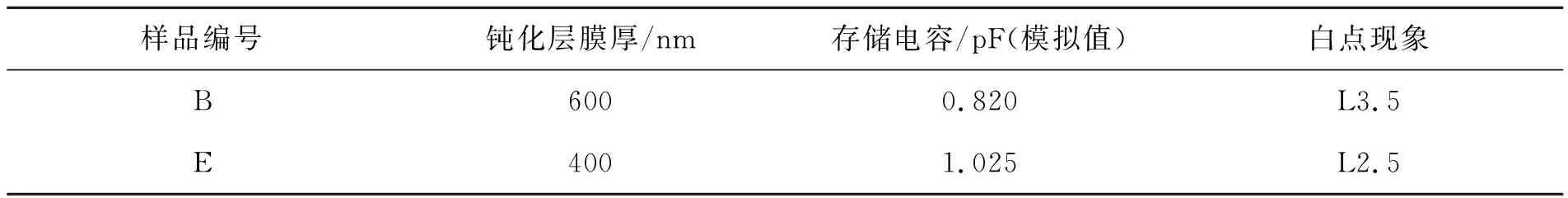

像素存儲電容受像素和公共電極的交疊面積、兩者之間距離的影響,本文探究了不同鈍化層厚度對白點不良的影響。

從表5可得,隨著鈍化層厚度降低,像素和公共電極距離減小,存儲電容逐漸增大,ΔVp減小,白點不良程度逐漸減輕,但無法解決白點不良,存儲電容提升會增加充電相關的問題,對于高端產品不太建議采用。因此,對于白點不良,建議仍然采用鈍化層 600 nm。

表5 鈍化層膜厚與白點現象的關系Tab.5 White dot phenomenon vs. PVX thickness

4 結 論

白點不良的產生,與有源層膜質和ΔVp存在直接關聯性。白點區域有源層膜質與其他區域存在導電差異(這種差異性是由設備原因導致,目前還無法從設備方面消除),導致ΔVp有差異。通過持續光照白點消失實驗和高溫老化白點復現實驗,直接證明了白點的消失是由于有源層在背光源照射下發生了Staebler-Wronski效應,電導率降低,減小了導電差異性,從而證明了白點產生的原因是有源層不同區域膜質與ΔVp的差異性。工藝上通過調整硅邊寬度和鈍化層厚度,來減小ΔVp值,改善白點不良。硅邊寬度由2.0降低到1.2 μm可以解決白點不良。本研究成果對產品的效益提升及Staebler-Wronski效應的現象提供了重要的指導作用。