一種基于CMOS工藝的91.6~93.2 GHz壓控振蕩器設(shè)計(jì)

李 嵬,劉 杰,呂金杰,劉 軍,蘇國(guó)東,3

(1.中國(guó)電子科技集團(tuán)公司信息科學(xué)研究院,北京 100086;2.杭州電子科技大學(xué)射頻電路與系統(tǒng)教育部重點(diǎn)實(shí)驗(yàn)室,浙江 杭州 310018;3.毫米波國(guó)家重點(diǎn)實(shí)驗(yàn)室,江蘇 南京 210096)

0 引 言

毫米波具有大帶寬、波束窄、穿透力強(qiáng)等優(yōu)點(diǎn),極大推動(dòng)了毫米波技術(shù)在通信、雷達(dá)、生物監(jiān)測(cè)等領(lǐng)域的發(fā)展。基于W波段(75~110 GHz)研制的固態(tài)集成電路是毫米波應(yīng)用技術(shù)的硬件基礎(chǔ),作為諸多固態(tài)集成電路模塊之一的壓控振蕩器實(shí)現(xiàn)了直流信號(hào)到交流信號(hào)的轉(zhuǎn)化,是毫米波通信系統(tǒng)本振電路、雷達(dá)系統(tǒng)信號(hào)產(chǎn)生電路中的核心器件。隨著互補(bǔ)金屬氧化物半導(dǎo)體(Complementary Metal Oxide Semiconductor,CMOS)工藝技術(shù)的進(jìn)步,CMOS晶體管的截止頻率和最大振蕩頻率已達(dá)到赫茲頻段(300 GHz~10 THz),為毫米波壓控振蕩器的研制奠定了工藝基礎(chǔ),進(jìn)一步推動(dòng)硅基毫米波壓控振蕩器的研究及產(chǎn)業(yè)應(yīng)用推廣[1-3]。目前,硅基毫米波頻段壓控振蕩器(Voltage Control Oscillator,VCO)在提升工作頻率方面的研究主要集中在2個(gè)方面。一種是通過(guò)基波VCO的方式直接產(chǎn)生毫米波信號(hào)[1,4-5],另外一種是將基波VCO產(chǎn)生的信號(hào)通過(guò)倍頻的方式間接產(chǎn)生毫米波信號(hào)[2-3]。此外,還可以采用開(kāi)關(guān)電感或開(kāi)關(guān)電容的方式來(lái)拓展VCO的調(diào)諧范圍。隨著電路工作頻率的提高,硅基無(wú)源器件的品質(zhì)因子進(jìn)一步降低,導(dǎo)致VCO相位噪聲惡化;同時(shí),調(diào)諧范圍的提升對(duì)變?nèi)莨艿娜葜底兓秶岢龈叩囊螅M(jìn)一步惡化了基波VCO的相位噪聲。因此,在確保VCO電路具有適中調(diào)諧范圍的前提下,提升毫米波基波VCO電路的相位噪聲具有一定的難度和挑戰(zhàn)。

本文提出一種基于變壓器結(jié)構(gòu)的高品質(zhì)因子電感(Transformer-Based Inductor,TB_IND),有助于改善VCO電路的相位噪聲,并采用金屬氧化物半導(dǎo)體(Metal Oxide Semiconductor,MOS)開(kāi)關(guān)與變?nèi)莨芟嘟Y(jié)合的策略,確保VCO電路調(diào)諧范圍的同時(shí)進(jìn)一步改善其相位噪聲。基于65 nm CMOS工藝,設(shè)計(jì)了一款工作頻率為91.6~93.2 GHz的VCO,可應(yīng)用于W波段的通信系統(tǒng)、雷達(dá)系統(tǒng)、生物監(jiān)測(cè)等系統(tǒng)。

1 VCO電路結(jié)構(gòu)及設(shè)計(jì)方案

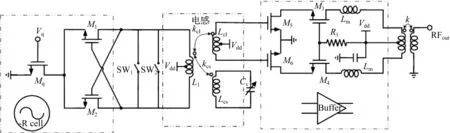

CMOS工藝的截止頻率和振蕩頻率雖然已進(jìn)入太赫茲頻段,但設(shè)計(jì)一個(gè)良好性能的毫米波VCO依然存在不小的挑戰(zhàn)。首先,在毫米波頻段中,晶體管的器件模型與實(shí)際測(cè)量值之間的擬合度存在差異,設(shè)計(jì)加工后的VCO易出現(xiàn)頻率偏移、調(diào)諧范圍變窄和相位噪聲惡化等問(wèn)題;其次,由于CMOS場(chǎng)效應(yīng)管的低輸出功率和低柵氧擊穿電壓,難以實(shí)現(xiàn)VCO的高輸出功率;再次,隨著頻率的提高,硅工藝的襯底損耗、金屬的趨膚效應(yīng)等易造成無(wú)源器件的品質(zhì)因子降低,從而導(dǎo)致諧振電路的品質(zhì)因子降低,惡化VCO電路的相位噪聲;最后,隨著電路工作頻率的提高,CMOS場(chǎng)效應(yīng)管的本征增益反而降低,直接導(dǎo)致毫米波VCO的負(fù)阻單元器件尺寸增加,抵消了諧振單元品質(zhì)因子降低所產(chǎn)生的影響,加大了毫米波頻段的基波VCO的設(shè)計(jì)難度。基于以上因素,本文設(shè)計(jì)了一款CMOS毫米波VCO電路,其原理圖如圖1所示。

圖1 CMOS毫米波VCO電路原理圖

圖1中,VCO電路由負(fù)阻單元-R Cell(由M1,M2,Mq組成),TB_IND,MOS開(kāi)關(guān)陣列(SW1,SW2),變?nèi)莨?Cv),輸出Buffer(由M3—M6組成)和輸出匹配電路構(gòu)成。其中,負(fù)阻單元采用經(jīng)典的交叉耦合負(fù)阻單元維持VCO穩(wěn)定的輸出毫米波信號(hào)。TB_IND采用變壓器的初級(jí)線(xiàn)圈作為電感(L1),與變?nèi)莨蹸v以及MOS開(kāi)關(guān)共同構(gòu)成的VCO電路的諧振單元;次級(jí)線(xiàn)圈I(Lcs)接可變電容,通過(guò)變?nèi)莨苋葜档母淖冇绊懘渭?jí)線(xiàn)圈Lcs和初級(jí)線(xiàn)圈L1之間的耦合,進(jìn)而改變諧振頻率。次級(jí)線(xiàn)圈II(Lcl)通過(guò)磁耦合將VCO的輸出信號(hào)輸入到Buffer電路;VCO通過(guò)輸出Buffer電路與負(fù)載之間相連,有效降低了負(fù)載電阻對(duì)VCO電路中負(fù)阻單元的影響,確保VCO電路與外電路相連時(shí)依然能穩(wěn)定輸出毫米波信號(hào)。為了方便電路測(cè)試,本文設(shè)計(jì)的片上變壓器實(shí)現(xiàn)了信號(hào)差分轉(zhuǎn)單端的功能,該變壓器與電感Lm構(gòu)成匹配網(wǎng)絡(luò),使得輸出Buffer和50 Ω負(fù)載阻抗達(dá)到更好的匹配。

2 VCO電路設(shè)計(jì)

從宏觀上來(lái)區(qū)分,圖1所示的VCO電路設(shè)計(jì)分為有源電路單元設(shè)計(jì)和無(wú)源元件設(shè)計(jì)兩部分。有源電路單元包含負(fù)阻單元和輸出驅(qū)動(dòng)電路,無(wú)源電路元件包含電感、MOS開(kāi)關(guān)、變?nèi)莨堋⑵献儔浩鳌鬏斁€(xiàn)等器件。

2.1 有源電路

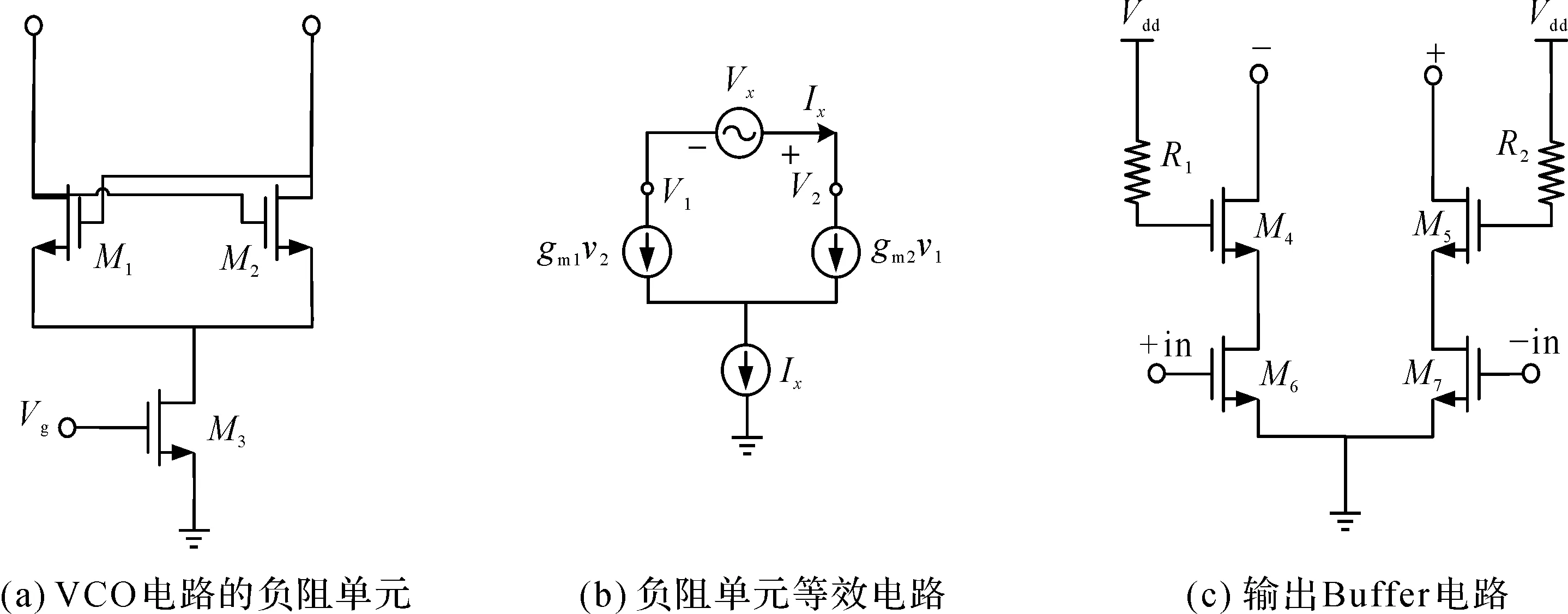

圖2給出了本文設(shè)計(jì)的VCO電路的負(fù)阻單元、負(fù)阻單元的等效電路和輸出Buffer電路。

圖2 VCO負(fù)阻單元及其等效電路、輸出Buffer電路

負(fù)阻單元采用經(jīng)典的交叉耦合差分單元如圖2(a)所示,主要用于補(bǔ)償諧振單元及其他與負(fù)阻單元相關(guān)電路的損耗,維持VCO交流信號(hào)的穩(wěn)定輸出。負(fù)阻單元由交叉耦合對(duì)場(chǎng)效應(yīng)管M1,M2及尾電流源場(chǎng)效應(yīng)管M3共同組成,其中M3可以改善交叉耦合對(duì)場(chǎng)效應(yīng)管所產(chǎn)生的輸入共模信號(hào)對(duì)電路的影響。此外,將M3的柵極設(shè)計(jì)為獨(dú)立供電端子,在電路測(cè)試時(shí),通過(guò)調(diào)節(jié)M3的柵極電壓來(lái)改變交叉耦合對(duì)場(chǎng)效應(yīng)管的電流,進(jìn)而改變負(fù)阻單元的阻抗。負(fù)阻單元的等效電路如圖2(b)所示,當(dāng)交叉耦合對(duì)場(chǎng)效應(yīng)管的總柵寬一致時(shí),負(fù)阻單元的阻抗為:

(1)

式中,gm為晶體管的跨導(dǎo)。通過(guò)對(duì)場(chǎng)效應(yīng)管M1,M2相關(guān)參數(shù)的選擇,使得交叉耦合對(duì)場(chǎng)效應(yīng)管形成的跨導(dǎo)略微高于VCO諧振單元的跨導(dǎo),從而保證VCO在起振后,能盡快輸出穩(wěn)定的交流信號(hào)。同時(shí),晶體管選擇時(shí),需要進(jìn)一步考慮晶體管本身的寄生電容,寄生電容會(huì)降低VCO的振蕩頻率,減小VCO的調(diào)諧范圍。本文設(shè)計(jì)中,M1和M2的單指柵寬為1.0 μm,總柵寬為24.0 μm;尾電流源管M3的單指柵寬為2.0 μm,總柵寬為80.0 μm。

電路工作頻率進(jìn)入毫米波頻段后,MOS場(chǎng)效應(yīng)管的柵-漏寄生電容對(duì)晶體管的影響愈發(fā)重要。在VCO的輸出Buffer設(shè)計(jì)中,如未將柵-漏寄生電容的影響考慮在內(nèi),極有可能因?yàn)樨?fù)載阻抗反向加載到VCO的負(fù)阻單元端口,導(dǎo)致VCO停振或者相位噪聲增加。因此,本文設(shè)計(jì)采用共源共柵放大器結(jié)構(gòu),如圖2(c)所示。與共源電路相比,共源共柵電路具有更大的輸出電阻,具有較高的反向隔離度,其輸出阻抗為:

Ro=gm4×ro4×ro5

(2)

式中,gm4為晶體管M4的跨導(dǎo),ro4和ro5分別為M4和M6的輸出電阻。

經(jīng)過(guò)優(yōu)化仿真,圖2(c)中,M4和M5的總柵寬選為6.4 μm,M6和M7的總柵寬選為12.0 μm。

2.2 無(wú)源器件

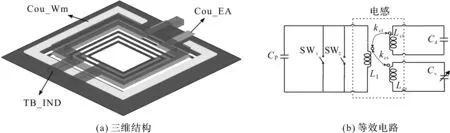

在VCO電路設(shè)計(jì)過(guò)程中,無(wú)源器件主要分為L(zhǎng)C諧振網(wǎng)絡(luò)和輸出匹配網(wǎng)絡(luò)。隨著電路工作頻段的逐漸增大,尤其進(jìn)入毫米波頻段后,場(chǎng)效應(yīng)管、電感、傳輸線(xiàn)等的寄生參數(shù)(電阻、電容、電感等)在電路中的影響逐步增加,器件之間的互擾增加,影響電路的性能。因此,設(shè)計(jì)時(shí)需充分考慮寄生參數(shù)無(wú)源器件與電路中其它器件之間的相互影響。通常情況下,低頻VCO電路設(shè)計(jì)時(shí),MOS開(kāi)關(guān)、變?nèi)莨堋⒇?fù)阻單元及輸出Buffer電路均接在電感的端口。但在毫米波VCO設(shè)計(jì)中,這種連接方式使得器件之間的互耦增強(qiáng),從而影響電路的性能。此外,目前的電磁仿真工具并不能準(zhǔn)確估量場(chǎng)效應(yīng)管在不同直流偏置下的相互耦合情況。因此,本文設(shè)計(jì)了一種基于片上變壓器結(jié)構(gòu)的高品質(zhì)因子電感,在參與諧振電路的同時(shí),通過(guò)線(xiàn)圈之間的磁耦合將振蕩信號(hào)輸送至輸出Buffer,并在版圖設(shè)計(jì)時(shí),將變?nèi)莨馨嵋浦磷儔浩鞯拇渭?jí)線(xiàn)圈的接口。TB_IND的3微結(jié)構(gòu)圖及其等效電路如圖3所示。

圖3 TB_IND的三微結(jié)構(gòu)圖及其等效電路

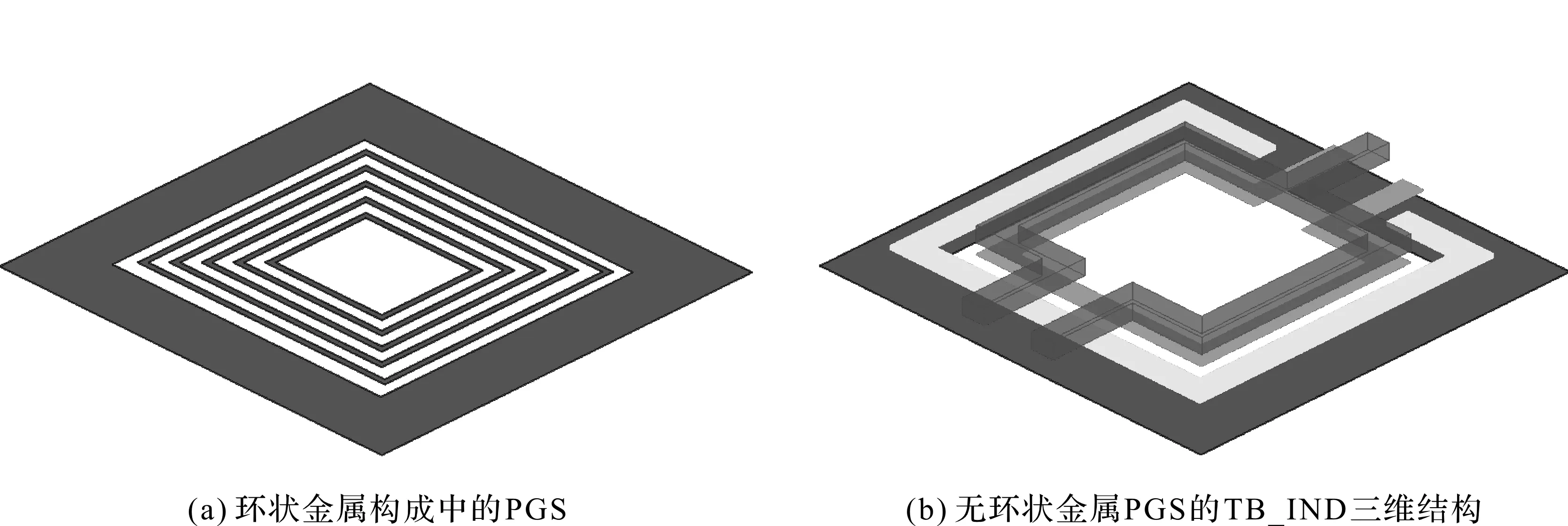

圖3(a)中,Cou_Wm線(xiàn)圈和Cou_EA線(xiàn)圈為變壓器的次級(jí)線(xiàn)圈,分別接輸出Buffer和變?nèi)莨埽儔浩鞯某跫?jí)線(xiàn)圈(TB_IND)則為諧振網(wǎng)絡(luò)中的電感。為了便于分析,圖3(b)給出TB_IND的等效電路拓?fù)浣Y(jié)構(gòu),其中Cp為交叉耦合單元及開(kāi)關(guān)管的寄生電容,Cd為輸出Buffer的寄生電容,Cv為變?nèi)莨艿碾娙荩闹性O(shè)計(jì)的VCO電路的輸出頻率由電感L1、次級(jí)線(xiàn)圈的互感及Cp,Cv和Cd映射到初級(jí)線(xiàn)圈的電容共同決定。為了提高基于變壓器的電感的品質(zhì)因子,電感的初級(jí)線(xiàn)圈采用工藝中的厚金屬(金屬層M8,銅,厚度為3.3 μm),用于降低金屬的損耗,同時(shí)采用一種改進(jìn)型屏蔽地[6]來(lái)降低襯底損耗,該屏蔽地采用底層金屬M(fèi)1設(shè)計(jì)的環(huán)狀金屬構(gòu)成,TB_IND的PGS與無(wú)環(huán)狀金屬PGS的TB_IND三維結(jié)構(gòu)如圖4所示。圖4(a)中,由楞次定律可知,電感上的變化電場(chǎng)會(huì)在金屬環(huán)上感生電流,而金屬環(huán)之間亦會(huì)感生電流。金屬環(huán)之間的感生電流方向相反,從而形成了相互減弱的磁場(chǎng),減弱了對(duì)電感的影響,改善了電感的品質(zhì)因子。

圖4 TB_IND的PGS和無(wú)環(huán)狀金屬PGS的TB_IND三維結(jié)構(gòu)圖

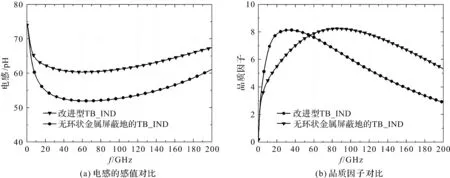

通過(guò)電磁仿真方法,評(píng)估本文提出的TB_IND和無(wú)環(huán)狀金屬屏蔽地的TB_IND的電感感值和品質(zhì)因子,結(jié)果如圖5所示。從圖5(a)可以看出,電感在200 GHz范圍內(nèi)未出現(xiàn)諧振點(diǎn),滿(mǎn)足VCO電路設(shè)計(jì)時(shí)的指標(biāo)要求;從圖5(b)可以看出,文中提出的TB_IND在W波段的品質(zhì)因子約為8.25,較無(wú)環(huán)狀金屬屏蔽地的TB_IND的品質(zhì)因子提高了約20%,說(shuō)明改進(jìn)型TB_IND可有效改善VCO電路的相位噪聲。

圖5 TB_IND與無(wú)環(huán)狀金屬PGS的TB_IND隨頻率變化

在VCO電路設(shè)計(jì)過(guò)程中,輸出匹配網(wǎng)絡(luò)主要通過(guò)片上變壓器和微帶線(xiàn)來(lái)實(shí)現(xiàn)。片上變壓器采用了邊緣耦合結(jié)構(gòu),為了減小金屬損耗,初級(jí)線(xiàn)圈和次級(jí)線(xiàn)圈均采用頂層金屬(M8)設(shè)計(jì)而成。微帶線(xiàn)的信號(hào)線(xiàn)亦采用工藝中的頂層厚金屬(M8)設(shè)計(jì)以降低金屬損耗。同時(shí),為了減小襯底的渦旋電流對(duì)無(wú)源器件品質(zhì)因子的影響,采用底層金屬(M1)作為輸出匹配網(wǎng)絡(luò)中的傳輸線(xiàn)和片上變壓器的屏蔽層,以提高信號(hào)在匹配網(wǎng)絡(luò)中的傳輸效率。此外,片上變壓器在實(shí)現(xiàn)阻抗匹配的同時(shí)實(shí)現(xiàn)了差分信號(hào)轉(zhuǎn)單端的功能,方便在片測(cè)試。

3 版圖與仿真實(shí)驗(yàn)

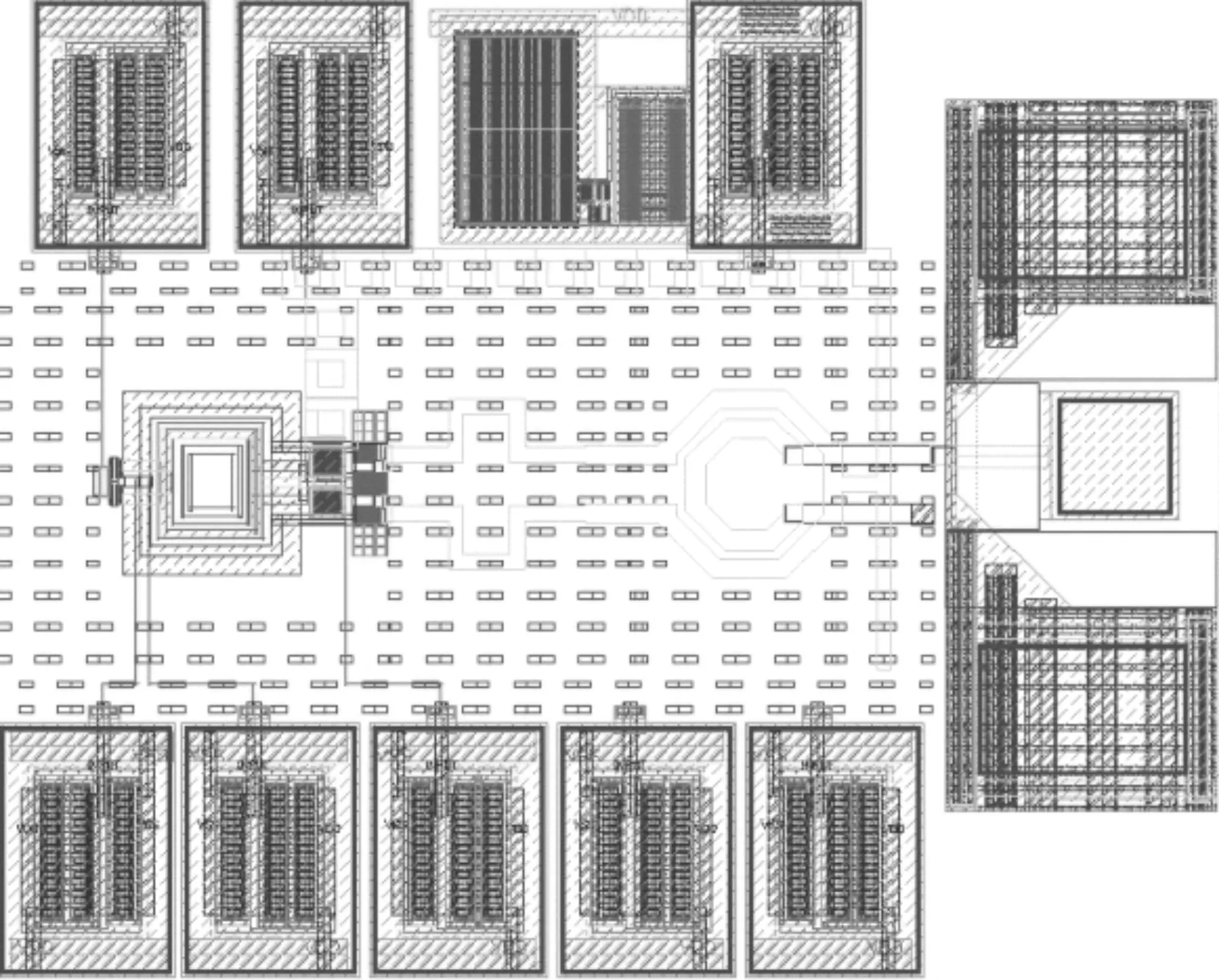

圖6 VCO電路版圖

基于65 nm CMOS工藝,本文設(shè)計(jì)了一款工作頻率為91.6~93.2 GHz的VCO,版圖如圖6所示。電路版圖設(shè)計(jì)中,充分考慮對(duì)稱(chēng)性,并根據(jù)仿真結(jié)果對(duì)版圖進(jìn)行優(yōu)化。VCO電路中使用的GSG焊盤(pán)、電感、傳輸線(xiàn)和片上變壓器等無(wú)源器件均進(jìn)行了電磁仿真評(píng)估,并與有源器件結(jié)合,完成設(shè)計(jì)。為了提高無(wú)源器件的品質(zhì)因子,電路中的電感、傳輸線(xiàn)均采用工藝中的頂層厚金屬,變壓器采用邊緣耦合結(jié)構(gòu),初/次級(jí)線(xiàn)圈均采用頂層厚金屬銅。同時(shí),采用工藝中提供的底層金屬M(fèi)1作為屏蔽地,有效提高了無(wú)源器件的品質(zhì)因子。信號(hào)通路及直流通路上均采用ESD保護(hù)。VCO電路芯片的大小為0.2 mm×0.2 mm。

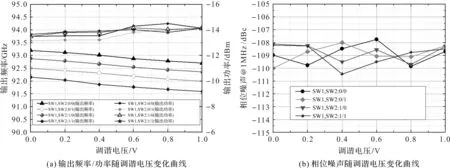

通過(guò)2組MOS開(kāi)關(guān)與變?nèi)莨芄餐瑢?shí)現(xiàn)VCO的頻率調(diào)諧。2組MOS開(kāi)關(guān)共有4種組態(tài),擴(kuò)展了VCO的調(diào)諧范圍。本文的VCO設(shè)計(jì)中,采用小尺寸變?nèi)莨軄?lái)實(shí)現(xiàn)頻率調(diào)諧,其容值變化范圍小,在結(jié)合MOS開(kāi)關(guān)共同調(diào)諧時(shí)需要保證每個(gè)開(kāi)關(guān)態(tài)的調(diào)諧頻率具有一致性,故設(shè)計(jì)的VCO調(diào)諧范圍為1.6 GHz,工作頻率范圍為91.6~93.2 GHz,VCO的輸出功率大于-14.5 dBm,在偏離諧振頻率10 MHz處的相位噪聲優(yōu)于-107.7 dBc/Hz。圖7給出了MOS開(kāi)關(guān)工作在0/0,0/1,1/0和1/1狀態(tài)時(shí),VCO的輸出頻率、輸出功率及相位噪聲隨調(diào)諧電壓變化的情況。

圖7 開(kāi)關(guān)1/2工作在4種狀態(tài)下的輸出頻率/功率、相位噪聲隨調(diào)諧電壓變化曲線(xiàn)

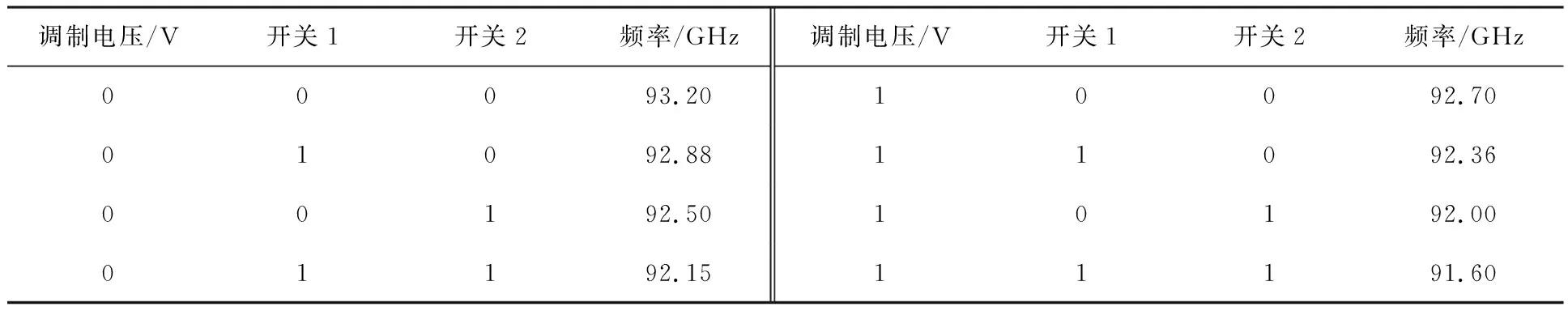

在4種狀態(tài)下,VCO輸出的交流信號(hào)的頻率隨調(diào)諧電壓、開(kāi)關(guān)狀態(tài)變化情況如表1所示。從表1可以看出,結(jié)合變?nèi)莨艿娜葜底兓琈OS開(kāi)關(guān)的每種開(kāi)關(guān)態(tài)可實(shí)現(xiàn)不小于0.45 GHz的調(diào)諧范圍,同時(shí)考慮工藝加工偏差等因素,在各個(gè)開(kāi)關(guān)態(tài)的頻率范圍有所交疊,VCO電路實(shí)現(xiàn)了1.6 GHz的頻率調(diào)諧范圍,且輸出頻率在開(kāi)關(guān)的4種狀態(tài)下均能連續(xù)調(diào)諧。

表1 VCO輸出頻率隨調(diào)諧電壓、開(kāi)關(guān)狀態(tài)變化表

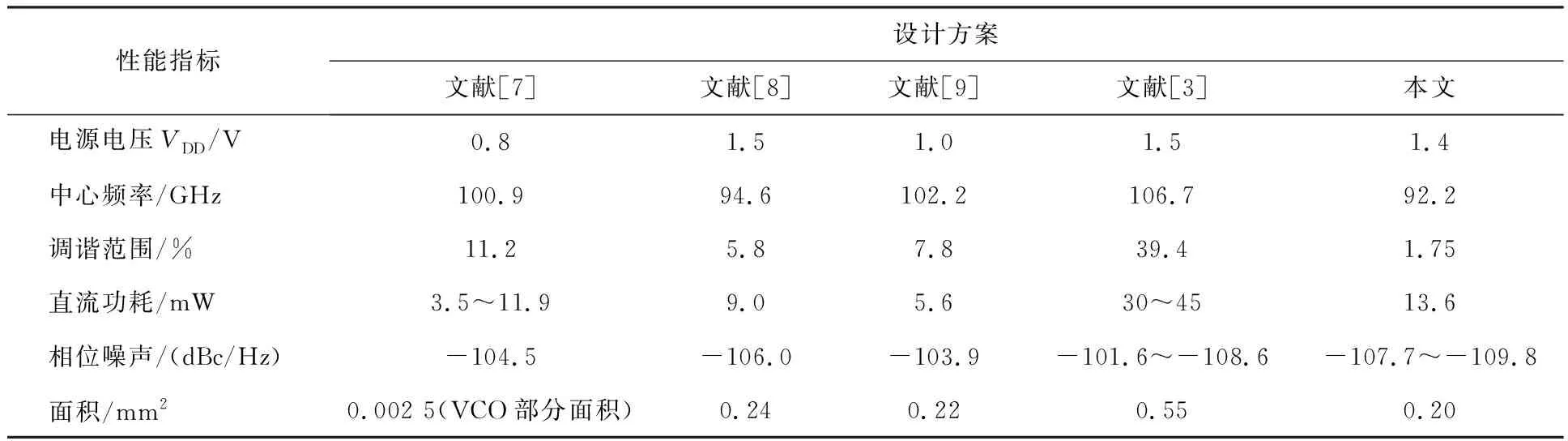

選取近年來(lái)基于65 nm CMOS工藝設(shè)計(jì)的W波段的VCO設(shè)計(jì)方案進(jìn)行比較,不同設(shè)計(jì)方案的性能參數(shù)如表2所示。

表2 基于65 nm CMOS工藝的VCO設(shè)計(jì)方案性能對(duì)比

從表2可以看出,和其他設(shè)計(jì)方案相比,本文提出的VCO設(shè)計(jì)方案的相位噪聲達(dá)到-107.7~-109.8 dBc/Hz,在相位噪聲方面具有一定的優(yōu)勢(shì)。

4 結(jié)束語(yǔ)

基于65 nm CMOS工藝,本文提出了一種基于變壓器結(jié)構(gòu)的具有高品質(zhì)因子的電感設(shè)計(jì)方案,在此基礎(chǔ)上,設(shè)計(jì)了一款工作頻率為91.6~93.2 GHz的VCO電路,改善了VCO電路的相位噪聲,拓展了VCO電路的頻率調(diào)諧范圍,為應(yīng)用于通信、雷達(dá)、生物檢測(cè)等系統(tǒng)的窄帶信號(hào)產(chǎn)生電路提供設(shè)計(jì)參考。后續(xù)計(jì)劃進(jìn)一步研究提高電感品質(zhì)因子的方法,在確保諧振網(wǎng)絡(luò)品質(zhì)因子的同時(shí)提高VCO電路的頻率調(diào)諧范圍。