基于門極放電補償的串聯IGBT有源驅動電路

周 野 王 旭 鮮 亮 楊 丹

(1. 東北大學信息科學與工程學院 沈陽 110819 2. 南洋理工大學能源研究院 新加坡 627590)

0 引言

隨著電力電子應用高功率、高電壓方向的發展,對半導體開關器件的耐壓等級及可靠性的要求也隨之升高。相比于碳化硅(SiC)、氮化鎵(GaN)等新興寬禁帶半導體器件,傳統硅(Si)基IGBT在耐壓等級、成本及技術成熟性等方面仍具有較大的優勢,并仍廣泛應用于高壓直流輸電、列車牽引變流器及大規模風力發電系統中[1-4]。然而,這些場合通常需要數百kV甚至上千kV的高電壓[2],單只IGBT無法滿足承壓需求,串聯IGBT的應用成為解決該問題的一種選擇,串聯IGBT應用過程中各IGBT間電壓平衡也成為近年來研究的熱點。針對該問題,文獻[5-15]給出了不同的解決方案,根據其作用方式的不同,主要分為以下三類:

(1)無源緩沖電路[5-8]。該方法主要通過在IGBT集射極或集柵極間并聯無源器件以實現先關斷器件過電壓能量的吸收,進而實現保護及均壓功能。該方法成本低、可靠性高。但緩沖電路自身的損耗限制了該方法在高頻高效率場合的應用,即使采用文獻[7-8]所述的帶有能量反饋功能的緩沖電路結構,開關瞬態時間的延長所引起的IGBT自身損耗的增加仍不能被忽視。

(2)電容耦合驅動[9-11]。該方法僅采用單只驅動電路結合耦合電容便可實現串聯器件整體通斷控制。由于上部IGBT驅動電量來源于下部IGBT集電極電位變化所引起的耦合電容充放電,因而驅動時間差異不可避免,雖然通過適當的電容值選取可以削弱該時間差異的影響,但該驅動方式對串聯器件數量及開關占空比仍有一定的限制[10]。另外,驅動電壓的不同造成部分IGBT長時間工作于有源區,開關損耗的增加也會影響其使用壽命。

(3)有源門極驅動[12-15]。該方法通過實時控制IGBT門極驅動電壓、電流以改變其開關瞬態特性,配合相應控制算法實現各IGBT間的承壓均衡。文獻[12]以集柵極間鉗位電路作用時間為依據實時調節驅動信號發出時刻,在實現過電壓保護的同時完成電壓平衡控制。文獻[13]通過阻容分壓及高速光耦實現承壓采樣并據此調節驅動信號發出時刻。上述兩種方式均需要控制級與驅動級間額外的隔離單元,增加了電路的復雜性及共模干擾[16]。此外,相應的平衡算法增加了變流器主控器負擔,對主控器頻率及存儲提出了更高的要求。文獻[14]提出了一種基于參考電壓跟隨的閉環驅動電路。然而,為確保控制的精確性,電路參數選取要求較高,不當的閾值選取會影響控制的穩定性與可靠性。文獻[15]提出了一種基于額外電流源的有源驅動方式,通過檢測IGBT所處開關階段的時長,逐步改變門極電流的大小以實現均壓控制。然而,該方法監測變量較多,開關瞬態時長的檢測對驅動核心控制芯片及AD-DA轉換芯片帶寬要求較高,增加了電路的成本與復雜度。

為實現串聯IGBT間電壓均衡的同時避免上述方法存在的問題,本文提出了一種基于門極電量補償的有源驅動電路。該電路具有如下優點:

(1)通過在傳統電壓驅動基礎上附加輔助電路實現均壓控制,無需額外的電源與信號隔離。

(2)輔助電路控制周期與開關周期相同。因此,低成本低頻控制芯片(如51單片機)即可滿足要求,降低了電路成本。

(3)輔助電路不會降低IGBT開關速度,避免了器件損耗的增加。

(4)驅動電路間彼此獨立,沒有串聯數量限制。

本文在介紹該驅動電路工作原理的同時給出詳細的參數設計原則,并基于仿真與實驗驗證了該驅動在串聯IGBT電壓平衡控制上的有效性與適用性。

1 電路結構與原理

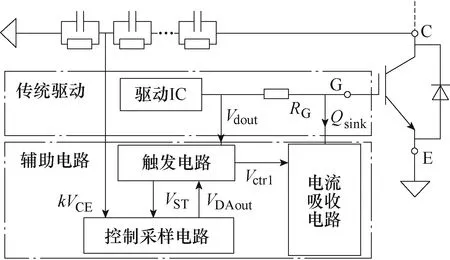

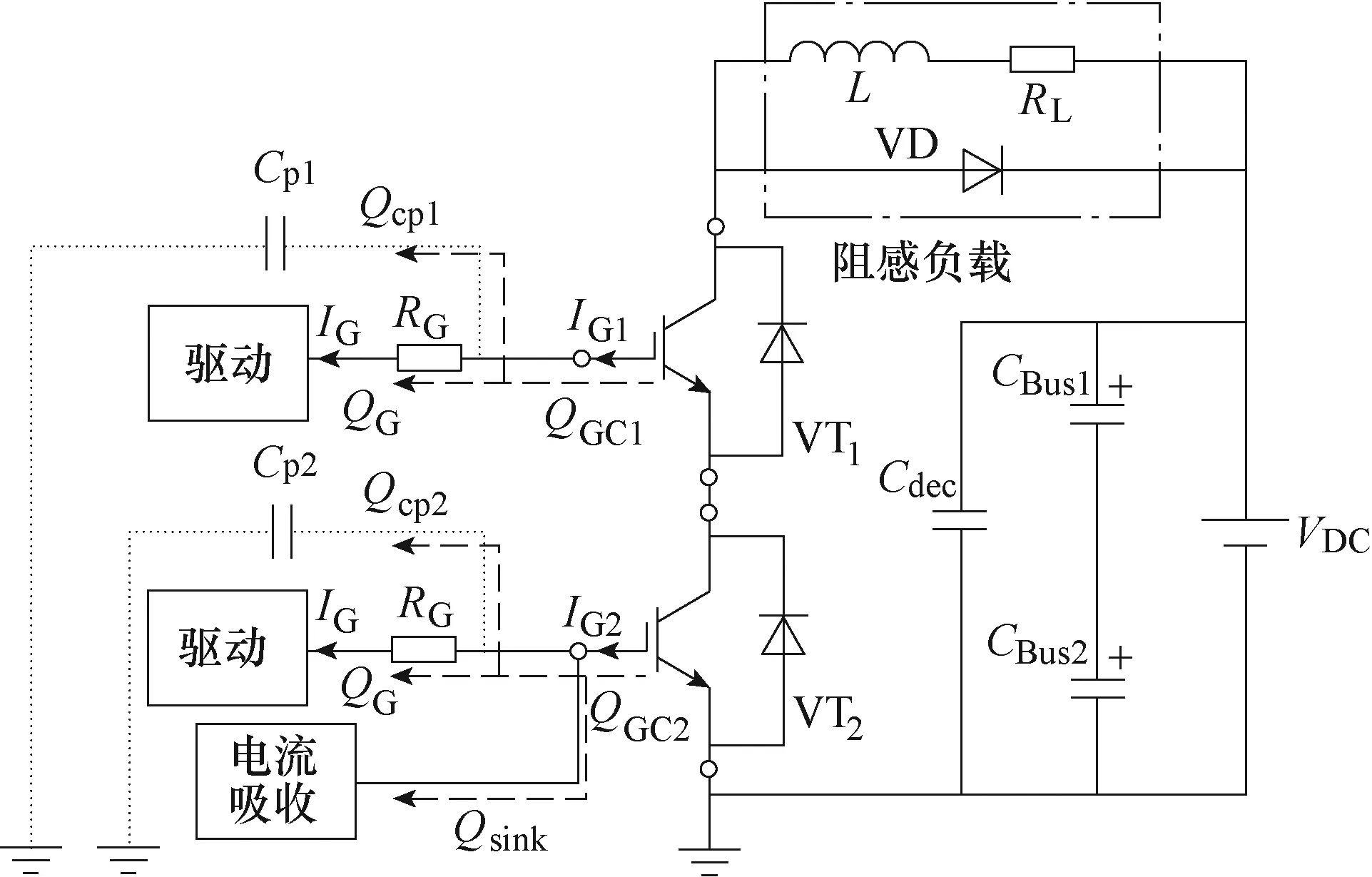

本文所提出的有源驅動電路框圖如圖1所示,其通過在傳統驅動電路基礎上附加輔助電路以實現均壓控制。其中傳統驅動電路由驅動IC及門電阻RG構成,依據開關信號實現通斷控制。輔助電路由電流吸收電路、觸發電路及控制采樣電路三部分構成。其各自功能如下:

電流吸收電路于IGBT關斷瞬態對其輸入電容Ciss產生額外吸收電量Qsink,進而調節IGBT關斷瞬態特性。Qsink的大小由觸發電路輸出Vctrl決定。

觸發電路依據驅動IC輸出電壓Vdout的下降沿來確定Qsink生成時刻。同時,發出信號VST觸發控制采樣電路對IGBT實時承壓VCE進行采樣,并將其生成的控制量VDAout于IGBT關斷瞬態以脈沖Vctrl的形式傳遞給電流吸收電路。

圖1 有源驅動電路框圖 Fig.1 Block diagram of the proposed active gate drive

控制采樣電路根據采樣得到的VCE值判斷IGBT是否過電壓,并依據VCE的大小生成相應的控制量VDAout以實現一個開關周期內的均壓調節。各部分電路的實現形式及其工作過程如下所述。

1.1 電流吸收電路

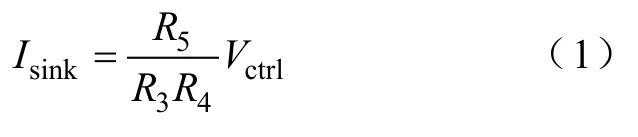

圖2所示為基于Wilson電流鏡結構的電流吸收電路。Vctrl為輸入電壓,其值由輔助電路另外兩部分決定。高速運算放大器OP與三極管VQ1~VQ4構成鏡像電流源,其輸出電流Isink用以產生額外吸收電量Qsink,對于固定的電路元件,Isink的大小由Vctrl的值決定,其關系滿足

圖2 電流吸收電路 Fig.2 The schematic circuit of the current sink

設Vctrl作用時間為tctrl,則該時段內電流吸收電路電源VE吸收的電量Qsink為

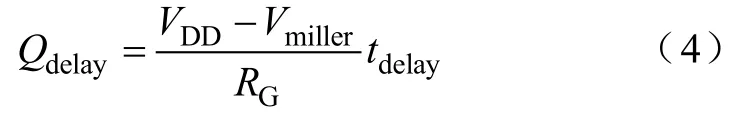

為說明電流吸收電路對串聯IGBT關斷承壓的影響,本文給出其作用下的兩只IGBT串聯測試電路如圖3所示,其中RL、L及續流二極管VD構成阻感負載,VT1與VT2為串聯的兩只IGBT且參數完全一致,Cp1與Cp2為驅動IC及其供電電源內部寄生電容[16],IG1與IG2為VT1與VT2門極放電電流,IG為驅動IC吸收電流,VDC為直流母線電壓源,RG為柵極外部電阻。根據關斷過程電壓電流狀態,電流吸收電路影響下串聯IGBT關斷過程從t0~t4可分為四個階段,如圖4所示。其過程分析如下:

圖3 基于兩只IGBT串聯的測試電路 Fig.3 Test circuit based on two series-connected IGBTs

圖4 電流吸收電路影響下串聯IGBT關斷波形 Fig.4 Turn-off waveforms of series-connected IGBTs with the current sink circuit

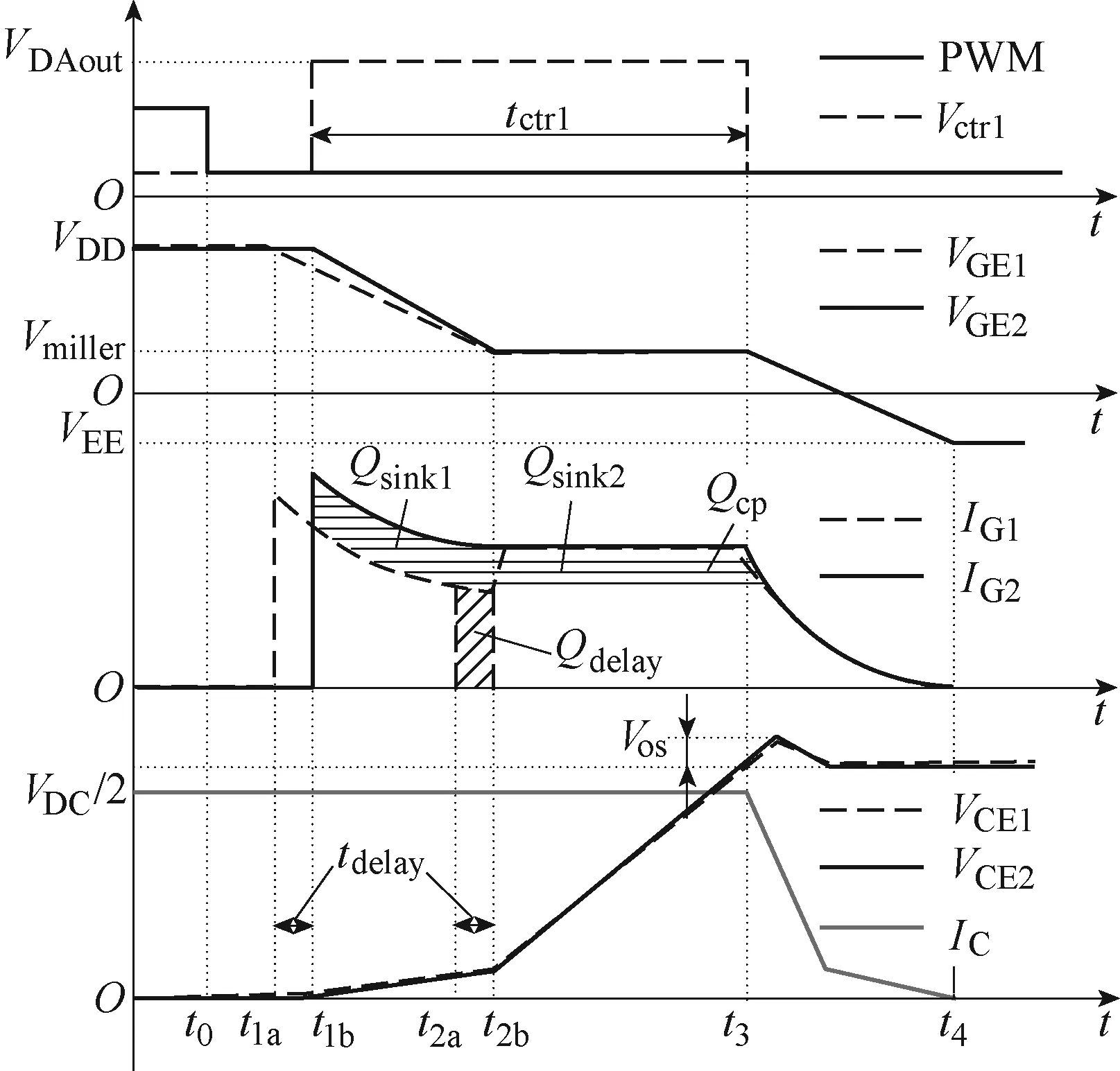

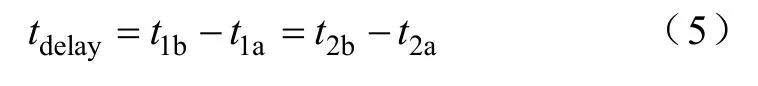

1)t0~t1b。t0時刻,驅動輸入脈沖寬度調制 (Pulse Width Modulation, PWM)信號由高至低,而此時驅動輸出電壓不會馬上降低,這是因為驅動IC均存在一定的傳輸延遲,對于不同種類驅動IC其延遲由數十ns至數百ns不等。同時,由于制造工藝的不同,即使相同型號驅動IC其延遲時間也存在一定差異,設VT1驅動延遲小于VT2驅動延遲且相差為tdelay,則門極電壓VGE1較VGE2提前降低,VT1輸入電容Ciss1首先開始放電。

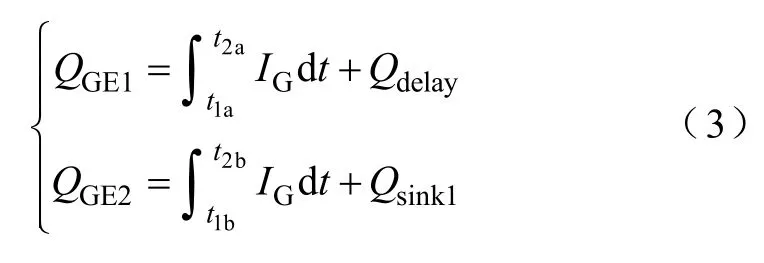

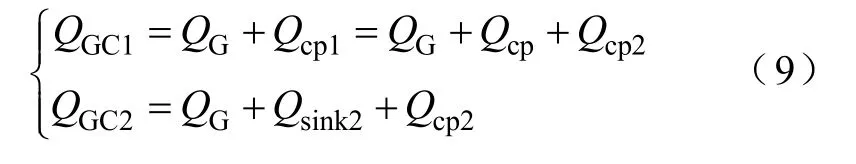

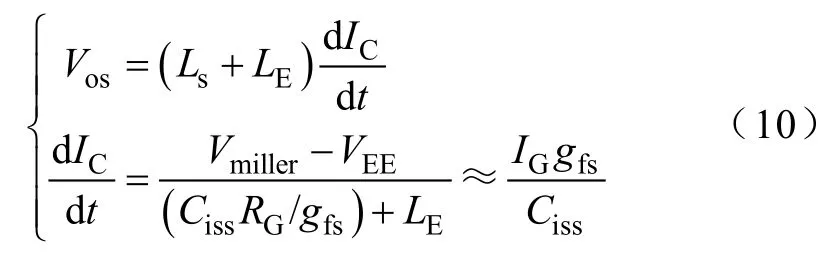

2)t1b~t2b。t1b時刻,VT2門極電壓VGE2也開始下降,同時電流吸收電路控制電壓Vctrl由0上升至VDAout,電流吸收電路開始工作并產生額外放電量Qsink1。此階段Ciss1與Ciss2的放電量QGE1與QGE2分別為

式中,Qdelay為上一階段關斷延遲tdelay在這一階段顯現出的門極放電偏差,其值為

式中,Vmiller為米勒平臺電壓;VDD為正驅動電壓。同時tdelay滿足

額外的放電量Qsink1將加快VT2輸入電容Ciss2的放電速率,雖然VGE2晚于VGE1開始下降,但在Qsink1的作用下其將與VGE1同時降至Vmiller。

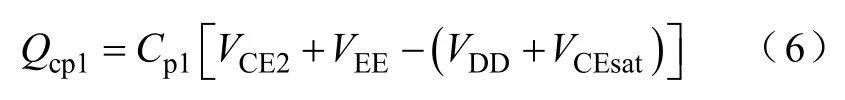

3)t2b~t3。t2b時刻,VT1與VT2集射極電壓VCE1與VCE2開始上升,而VCE2的上升將引起VT1門極對地電位的快速升高,進而為VT1門極對地寄生電容Cp1充電,其充電量為

式中,VEE為負驅動電壓;VCEsat為IGBT開通飽和壓降。同時,VT2門極對地電容Cp2充電量為

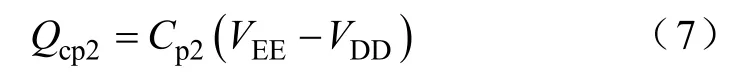

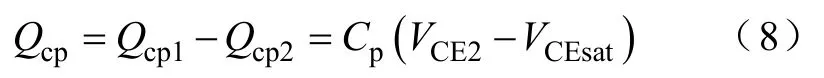

令Cp1=Cp2=Cp,由式(6)與式(7)可得,Qcp1與Qcp2的差值Qcp為

若驅動IC所吸收的電量相同,則Qcp在該階段將引起Ciss1與Ciss2放電量的偏差。在電流吸收電路作用下,該階段Ciss1與Ciss2的放電量QGC1與QGC2分別為

式中,QG為驅動IC吸收電量;Qsink2為電流吸收電路在這一階段額外吸收電量。

4)t3~t4。該階段VT1與VT2承壓已達到關斷穩態值,Vctrl重新降為0,電流吸收電路不再工作。集電極電流IC開始下降,由于主回路及器件雜散電感的存在,感生電壓在VCE上形成幅值為Vos的電壓尖峰[15,17],其值滿足

式中,Ls與LE分別為主回路雜散電感與IGBT射極寄生電感;gfs為器件跨導。由式(10)可知,Vos的大小與關斷瞬態IC下降速率有關,而IC下降速率與IG正相關,由于此階段內電流吸收電路不再作用,故其不會影響關斷尖峰電壓值。此階段門極電壓從閾值降至VEE,串聯IGBT關斷完成。

由IGBT開關過程輸入電容充放電定義可知,IGBT關斷過程中所需關斷電量QGoff[18]為

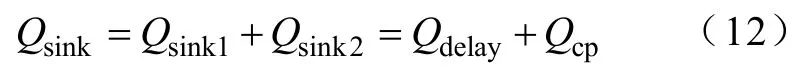

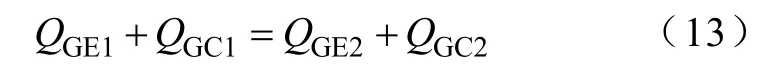

由式(3)、式(9)、式(11)可知,若滿足

則有

即VT1與VT2關斷過程輸入電容放電量QGoff1與QGoff2滿足

由文獻[17]分析可知,對于特性完全相同的串聯IGBT,關斷過程中輸入電容的放電量影響其關斷瞬態特性及穩態承壓。因此,關斷瞬態輸入電容放電量的一致性是確保其關斷承壓均衡的重要因素。據式(12),若使電流吸收電路額外吸收電量Qsink等于驅動輸出延遲及驅動寄生電容所引起的放電偏差Qdelay與Qcp之和,則可實現電壓平衡。

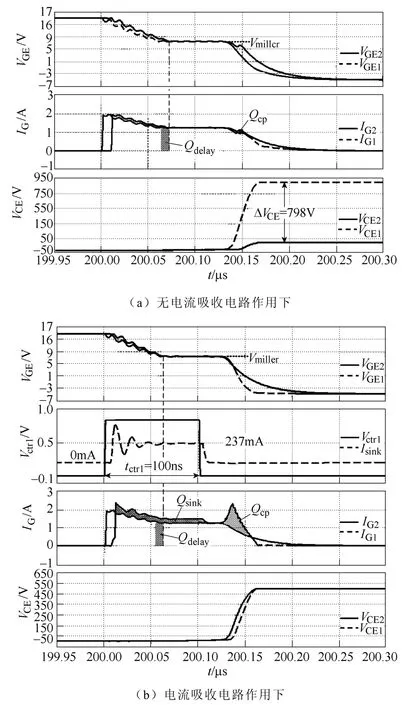

為驗證門極放電量對串聯IGBT關斷承壓的影響及電流吸收電路的均壓作用,本文給出基于LTSpice的兩只IGBT串聯仿真結果如圖5所示,其仿真電路結構與圖3一致,仿真元器件及其參數見表1及表2。

由圖5a可以看出,沒有電流吸收電路作用時,10ns的關斷延時所造成的串聯IGBT門極放電偏差Qdelay將引起798V的承壓差。由于該情況下,下管VT2承壓VCE2非常小,據式(8)可知,此時寄生電容Cp所引起放電偏差Qcp也如圖5a所示,其值很小不足以影響關斷瞬態特性。

圖5b所示為電流吸收電路作用下串聯IGBT關斷瞬態相關波形。可以看出,Vctrl控制下的吸收電 流Isink所生成電量Qsink用以補償放電偏差Qdelay及Qcp。在其作用下,VCE1與VCE2在關斷穩態時幅值基本一致,電壓平衡得以實現。需要注意的是,與圖5a相比,該情況下Qcp的值隨著VCE2的升高而增大,與前文理論分析一致。

圖5 串聯IGBT關斷瞬態仿真波形 Fig.5 Simulation waveforms of the series-connected IGBTs during a turn-off transient

表1 主功率回路仿真參數 Tab.1 The simulation parameters of power circuit

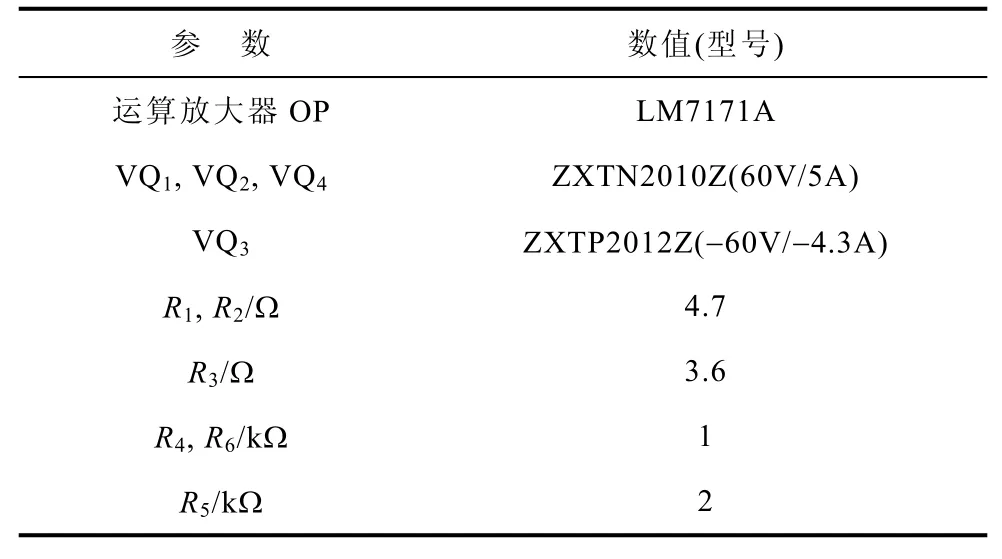

表2 電流吸收電路仿真參數 Tab.2 The simulation parameters of current sink circuit

1.2 觸發電路

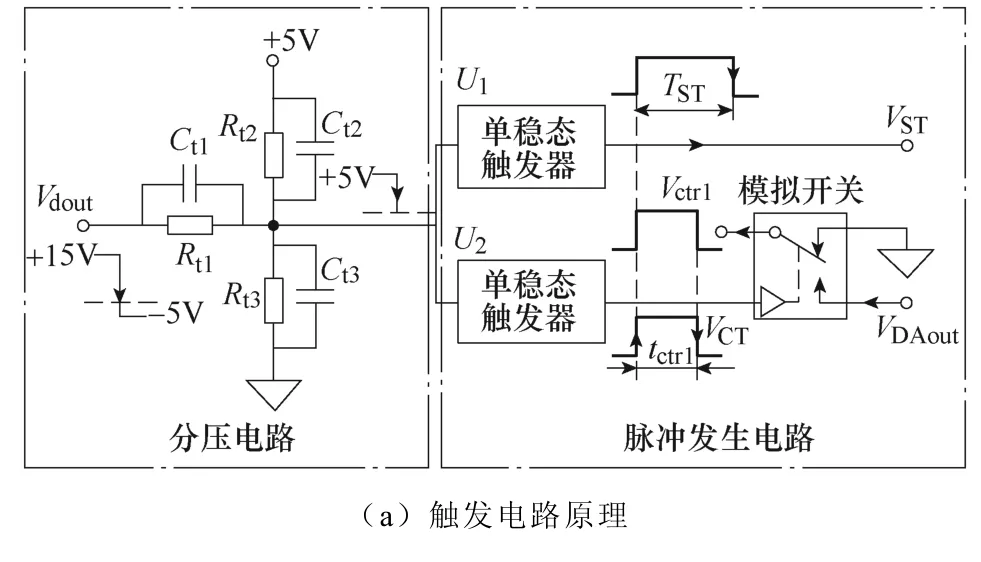

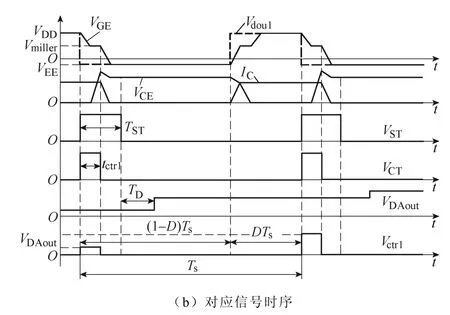

觸發電路及其工作原理如圖6所示。圖6a為本文所提出的觸發電路,其由阻容分壓電路及脈沖發生電路組成。其中分壓電路通過合適的阻容搭配將驅動IC輸出電壓Vdout轉化為TTL電平信號并傳輸給脈沖發生電路。脈沖發生電路由兩只下降沿觸發單穩態觸發器U1、U2及一只模擬開關組成,其中U1產生一時長為TST脈沖信號VST用以觸發采樣。而U2產生一時長為tctrl脈沖信號VCT用以控制模擬開關,在脈沖時間tctrl內,將控制采樣電路輸出信號VDAout與電流吸收電路輸入級Vctrl相連,實時改變Vctrl的值。各信號時序如圖6b所示,其中,Ts為開關周期,D為占空比,TD為控制采樣電路輸出延遲。

觸發電路的響應時間影響整個輔助電路的控制精確性與有效性,因此,觸發電路各元件應具有高帶寬頻率及響應速度。本文采用TI公司單穩態觸發器SN74LVC1G123及模擬開關TS5A63157,其在5V電源電壓下最大響應時間分別為7.6ns及5ns。合適的阻容搭配下分壓電路延遲時間基本可以忽略,因此整個觸發電路最大響應時間為12.6ns。

圖6 觸發電路及其工作原理 Fig.6 The schematic and sequence diagrams of the trigger circuit

1.3 控制采樣電路

由圖1與圖6b可知,控制采樣電路的功能是在觸發信號VST的作用下依據每個關斷周期IGBT靜態承壓來產生下一周期Vctrl對應的幅值VDAout。進而實現整個驅動電路的閉環均壓控制。

圖7 控制采樣電路原理框圖 Fig.7 Schematic diagram of control and sampling circuit

為實現上述功能,本文提出如圖7所示的控制采樣電路。為降低驅動電路成本,主控芯片采用1T 內核8051單片機STC8A8K64S4A12(宏晶),其自身集成采樣率800Ksps模數轉換器(ADC)。主控芯片輸出信號通過TLC7528實現數模(DA)轉換,并由OPA2830緩沖輸出。

本文均壓調節控制算法采用逐級調節與PI調節相結合的形式。IGBT靜態承壓VCE經阻容分壓后作為ADC的輸入。MCU檢測到觸發電路輸出信號VST下降沿后開啟AD轉換,采樣值與理論平均承壓 值相比較,若其值小于,則二者差值記為e。e依次與預設閾值eth1、eth2及eth3相比較,若e大于預設閾值ethx(x=1, 2, 3),則相應的增量Vthx(x=1, 2, 3)將被疊加于這一周期輸出nthVo,并將其和作為下一周期的輸出(n+1)thVo,直至數個周期后e小于最小閾值eth3時,PI調節替代逐級調節將輸出穩定于較小范圍內。采用逐級調節的目的在于迅速界定輔助電路輸出電壓范圍,確保控制的快速性,采用PI調節的目的在于輸出范圍界定后利用較大的積分系數避免輸出的波動,確保控制的穩定性。

2 設計方法

在分析了本文所提出的有源驅動電路工作原理后,本文給出實際應用過程中各子電路參數設計原則。其實驗給定條件為:直流母線電壓VDC=1kV,最大負載電流10A,兩只串聯IGBT型號為IHW20N120R3(1 200V/20A,英飛凌)。

2.1 電壓驅動電路設計

本文采用安華高ACPL-W341光耦作為基本驅動芯片,其驅動電壓設為+15V/?5V,輔助電路IC為+5V供電,電流吸收電路電源電壓VE設為?15V,輸入級放大器OP供電電壓為±15V。根據所需電壓等級,±15V電壓由DC-DC模塊電源WRE0515S- 3WR2(金升陽)提供,±5V電壓分別由位于模塊電源后級的線性穩壓芯片MC78L05與MC79L05(安森美)提供。

2.2 輔助電路設計

由1.1節的分析可知,輔助電路的目的在于補償關斷瞬態驅動延遲差異及門極對地寄生電容所引起的串聯IGBT輸入電容放電偏差。因此,最大理論放電偏差是確定電路元件參數的重要因素之一。對于Qdelay的理論最大值可由式(4)求得。其中,tdelay為ACPL-W341最大輸出延遲差異,tdelay= 100ns,Vmiller[19]可以估算為 式中,Vth為IGBT門極閾值電壓,Vth=5.8V;gfs= 16.3S。依據實驗條件可以求得Vmiller=6.4V。代入式(4)解得Qdelay最大值為86nC。

寄生電容Cp由隔離電源及驅動芯片隔離寄生電容組成,通過數據手冊可知,DC-DC電源隔離電容最大值為50pF,ACPL-W341輸入輸出間寄生電容為0.6pF,因此Cp的值約為50.6pF。當承壓均衡時,VCE2=500V,IGBT飽和壓降約為2V。代入式(8)可得,Qcp最大值為25.2nC。由式(12)可知,Qsink的最大值為111.2nC。

由IHW20N120R3數據手冊可知,其關斷所需時間由關斷延遲時間td(off)及電流下降時間tf組成,其值分別為387ns及25ns。根據1.1節所述電流吸收電路工作原理可知,tctrl的大小在滿足補償所需時間的同時應不大于td(off),以避免加快電流下降速率進而增大關斷電壓尖峰,本文取tctrl的值為210ns。

電流吸收電路中運放OP及三極管VQ1~VQ4的選型與表2一致,其中,R3影響電流吸收電路最大輸出,其選取原則如下:由于LM7171A最大負輸出擺幅為?10.5V,且ZXTP2012Z飽和壓降為?950mV,因此R3兩端最大壓差VR3(max)為?9.55V。考慮到tctrl時段內電流吸收電路需能提供Qsink的最大值,由式(2)可得,最大吸收電流Isink(max)=530mA,因此由

可知,R3=18.02Ω,此處取常用阻值18Ω。

觸發電路在提供時長為tctrl的控制信號VCT的同時還需提供時長為TST的采樣延遲信號VST。由圖6b可知,一方面,TST要足夠長以確保采樣時刻VCE關斷尖峰電壓已消失且達到穩態值;另一方面,TST不能大于單開關周期內IGBT關斷時長(1?D)Ts,以避免在其開通期間采樣。因此,TST的大小需滿足

式中,Dmax為最大開關占空比;fs(max)為IGBT最大開關頻率。令fs(max)=5kHz,Dmax=0.9,代入式(17)解得412ns≤TST≤20μs,此處取TST=1μs。

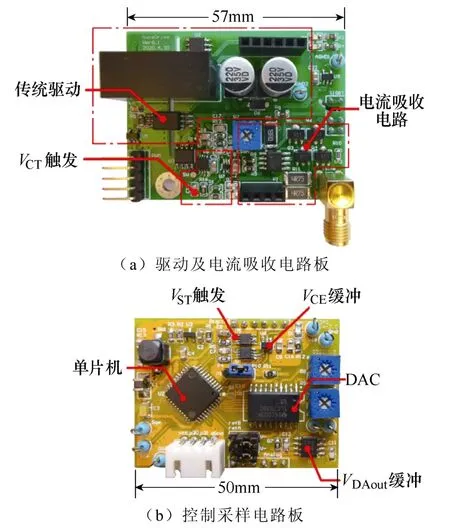

圖8所示為應用上述器件構成的有源驅動電路結構,其中,控制采樣電路為獨立可插拔結構,便于更換其他型號MCU及DAC以適應不同應用需求。從圖8可以看出,該驅動電路不需要額外電源或信號隔離單元,在降低成本的同時減小了寄生參數及電磁干擾對IGBT開關特性的影響。

圖8 有源驅動電路結構 Fig.8 Outlook of the active driving circuit board

式中,n為串聯單元數量;m為單只IGBT允許承壓 誤差,通常取5%[20]。根據實驗條件可得=550V。 閾值eth1~eth3的選取決定了控制的準確性與快速性,其關系應滿足

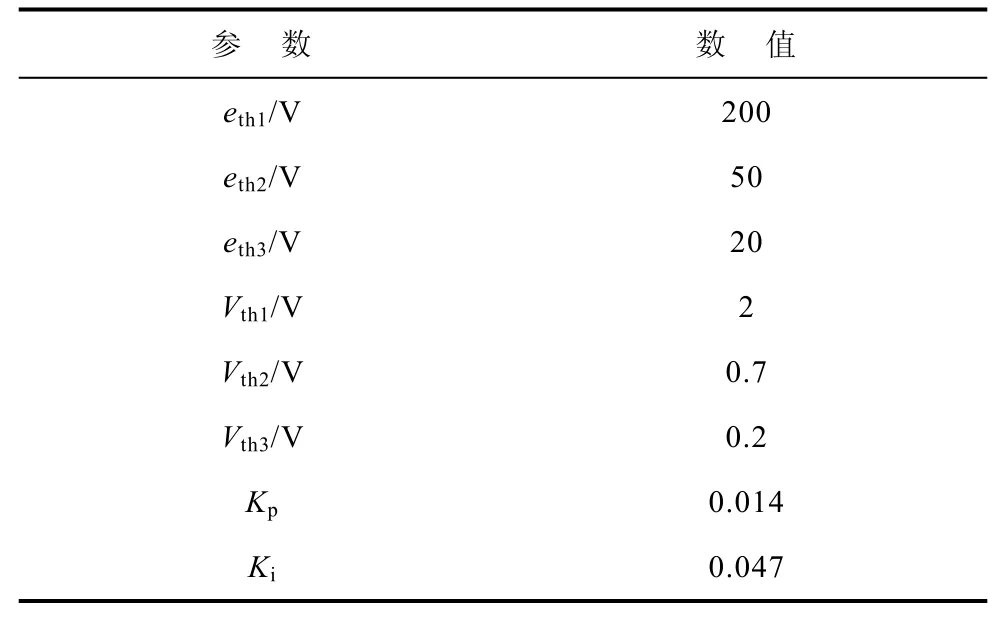

根據式(19)結合實驗條件及測試驗證,本文逐級控制算法相關參數及PI控制系數(Kp,Ki)見表3。

表3 控制算法相關參數 Tab.3 The parameters of the control algorithm

3 實驗驗證

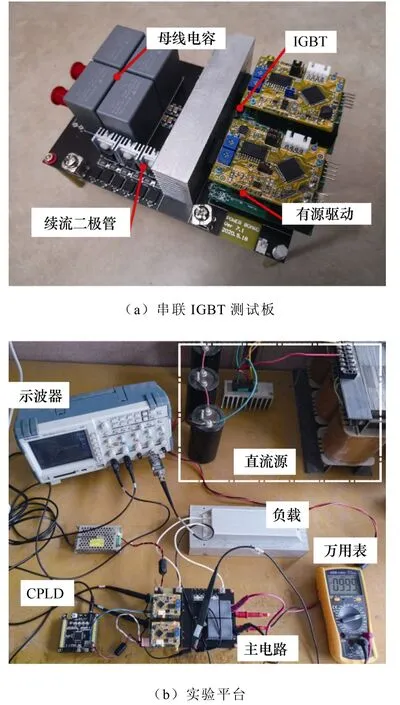

為驗證所提出的有源驅動電路均壓作用,本文依據圖3搭建了如圖9所示的兩只IGBT串聯實驗平臺。其中直流母線電壓為1kV,負載采用100Ω線繞電阻,其等效電感為25μH。串聯IGBT型號如第2節所述為IHW20N120R3(1 200V/20A),主回路續流二極管采用3只G3S06510A(650V/10A)串聯結構。電壓波形由泰克四通道隔離示波器TPS2024B配合無源探頭P2220(200MHz/300V)及UT?P20(250MHz/1.5kV)完成采集,驅動信號由CPLD(5M240ZT100C5N)產生。

圖9 主電路及測試平臺 Fig.9 The testing board and platform setup in this paper

3.1 僅使用傳統驅動時串聯實驗波形

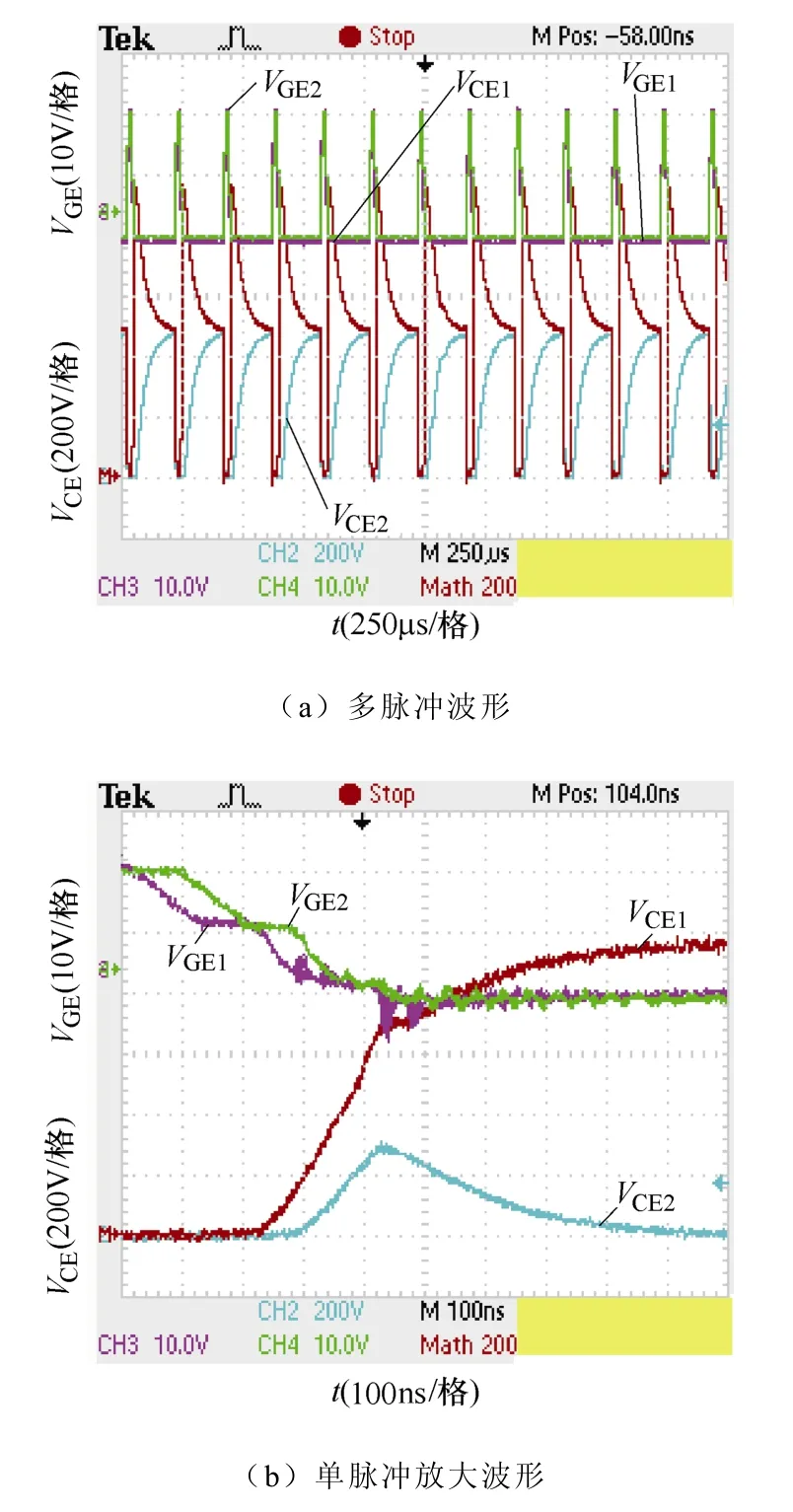

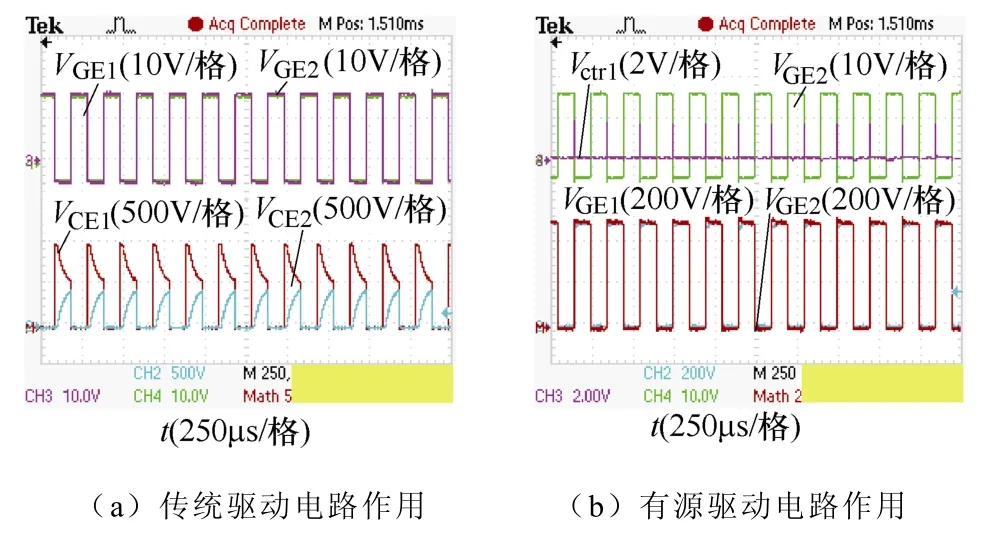

為對比有源驅動電路均壓效果,本文首先給出傳統驅動電路作用下串聯IGBT電壓波形。圖10給出了tdelay=100ns時串聯IGBT電壓波形。由于缺少高壓差分探頭,上管VT1承壓波形通過對兩只IGBT集電極電壓相減的方式顯示于MATH通道。可以看出,下管VT2的延遲關斷使上管VT1在關斷瞬態幾乎承受了整個母線電壓1kV,盡管在靜態均壓電阻作用下二者承壓趨于平衡,但隨著母線電壓的升高VT1將有過電壓損壞的風險。

圖10 傳統驅動電路作用下串聯IGBT電壓波形 Fig.10 Experimental waveforms of series-connected IGBTs with conventional gate drivers

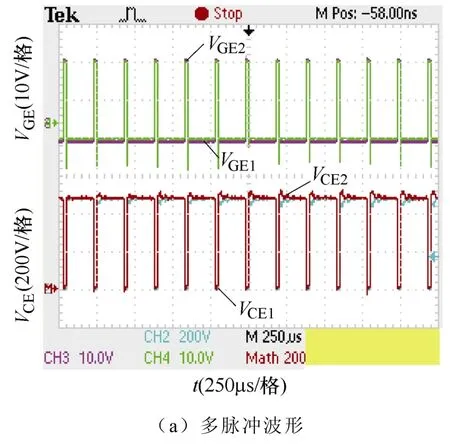

3.2 有源驅動作用下串聯實驗波形

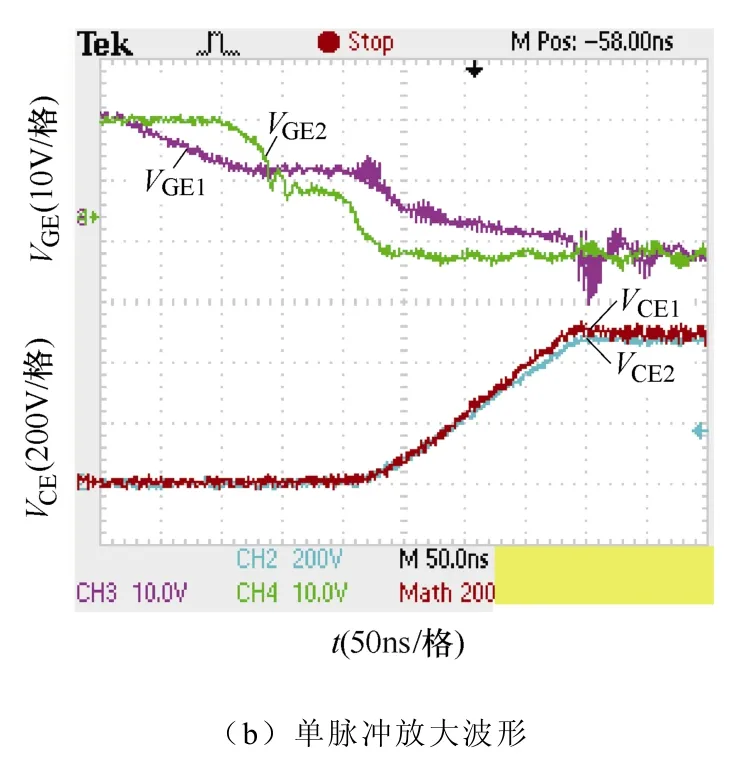

圖11所示為有源驅動電路作用下串聯IGBT電壓波形。與圖10相比可以看出,雖然VGE2晚于VGE1開始下降,但在電流吸收電路的作用下,更快的下降速率使其與VGE1幾乎同時進入米勒平臺。VCE1與VCE2上升時間基本一致,電壓平衡得以實現。

圖11 有源驅動電路作用下串聯IGBT電壓波形 Fig.11 Experimental waveforms of series-connected IGBTs with proposed active gate drivers

圖12給出了電流吸收電路作用時Vctrl與Isink的波形。可以看出,在檢測到VGE2的下降沿后,Vctrl由零變為控制采樣電路輸出VDAout。由于運放LM7171的輸出延遲及三極管開通延遲的存在,Isink滯后于Vctrl約30ns。然而,如2.2節所述,電流吸收電路作用時間tctrl(210ns)仍處于IGBT關斷延遲時間387ns內,故其在關斷瞬態提供的放電補償量不變,不影響電壓平衡控制效果。

3.3 控制算法的驗證

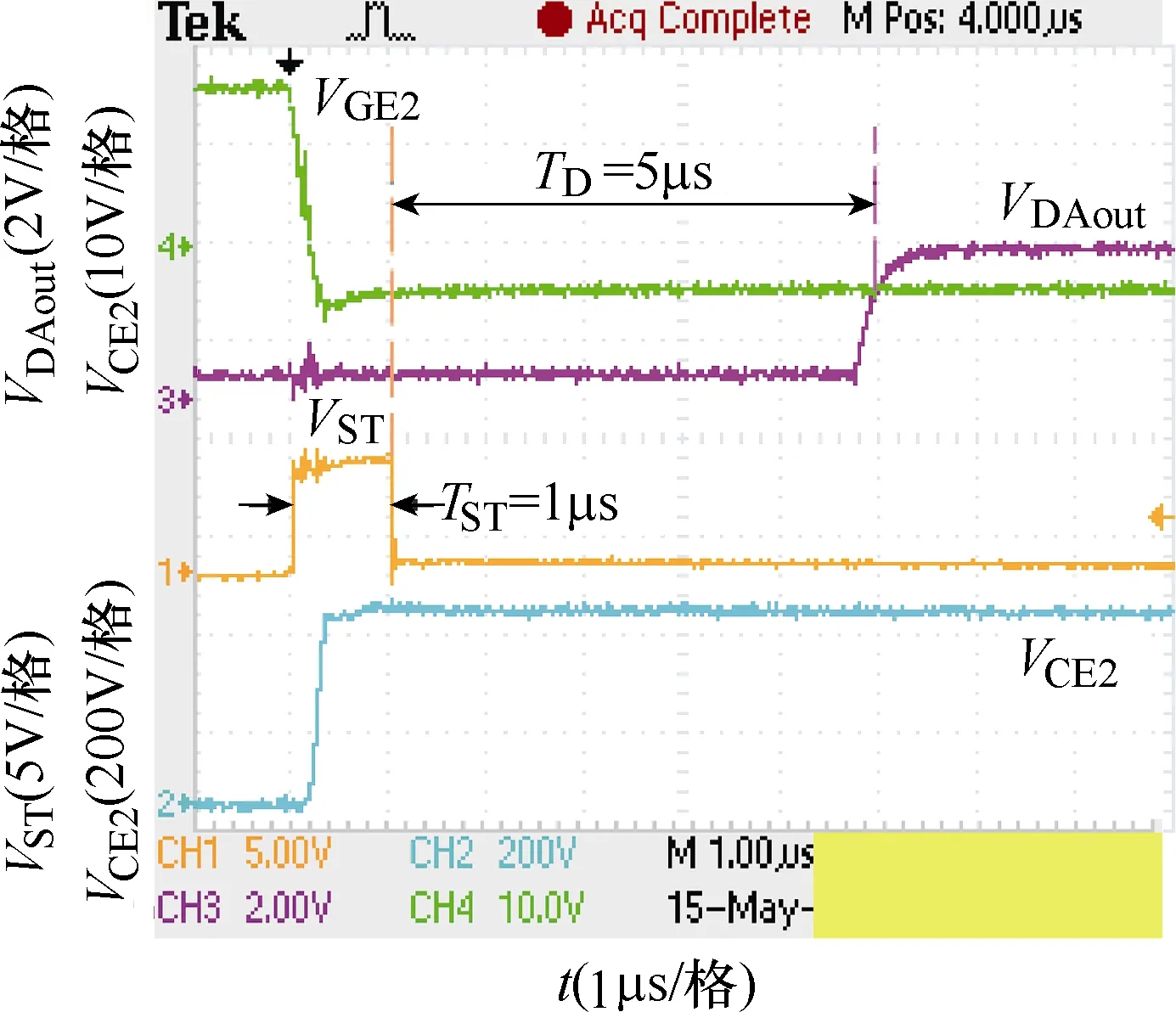

首先,為了驗證控制采樣電路的性能,圖13給出了調節過程中觸發信號VST與控制采樣電路輸出VDAout的波形。可以看出,在VST下降沿到來時,VCE2已達到穩態值。經過5μs的AD采樣、算法處理及DA輸出延遲TD后,VDAout的值得以更新并在下一個開關周期作為電流吸收電路的輸入。

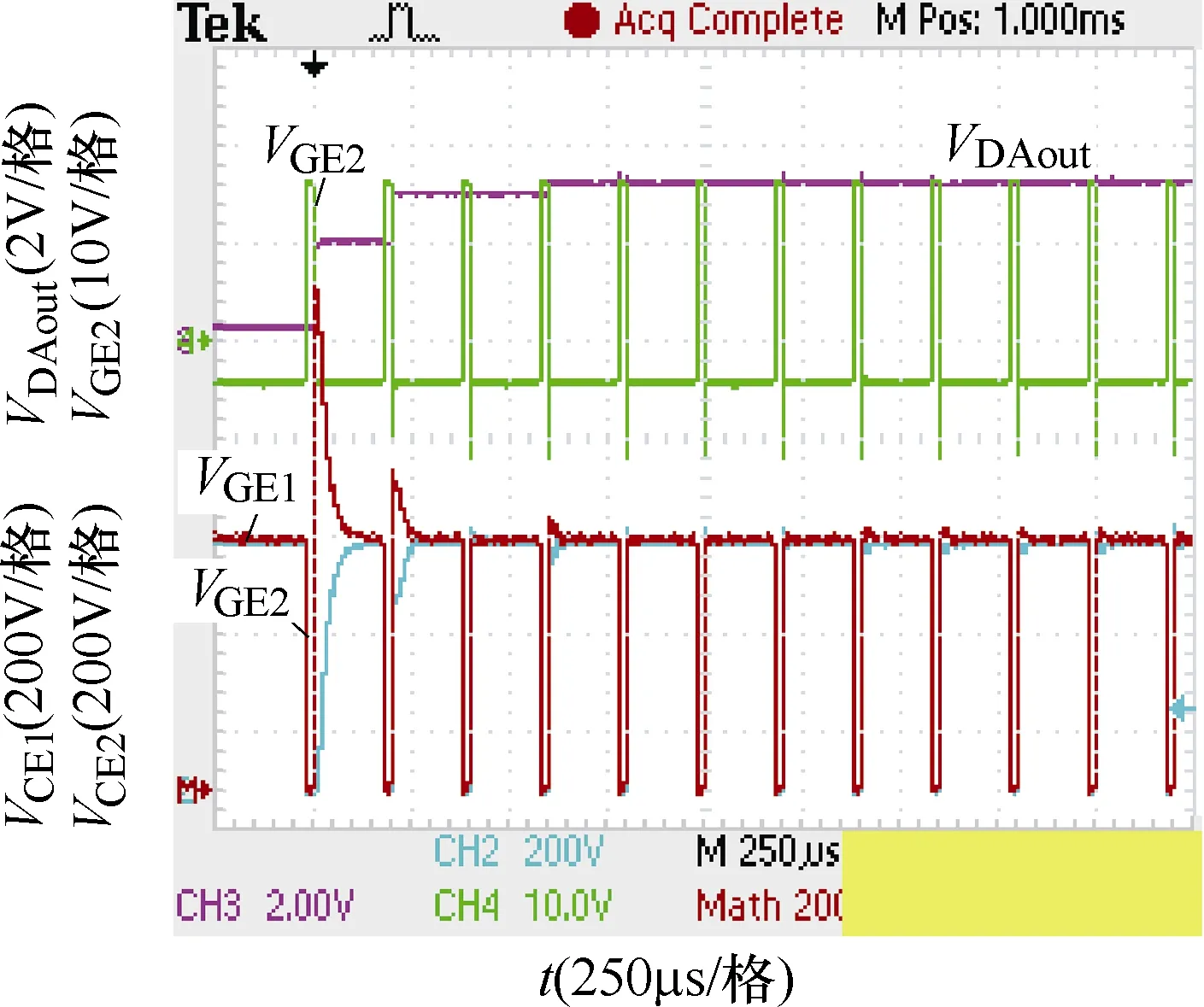

圖14給出了初始12個開關周期內串聯IGBT電壓及控制采樣電路輸出VDAout波形。據圖14可以 看出,在第一個開關周期內,由于輔助電路尚未作用,兩只IGBT承壓呈現出極大的不平衡,VDAout依據逐級控制算法閾值設置上升Vth1(2V)。在下一個開關周期,雖然電壓不平衡仍然存在,但2V的Vctrl已使其不平衡度大幅降低。因此,VDAout上升增量降低為Vth2(0.7V),在其作用下,電壓不平衡程度進一步降低。經過4個開關周期后,兩只IGBT承壓基本一致,PI控制取代逐級控制方式并將VDAout的值穩定在較小區間內,均壓調節完成。

圖13 控制采樣電路輸出電壓時序波形 Fig.13 Time sequence among the relevant voltage signals of the control and sampling circuit

圖14 有源驅動電路作用下電壓調節過程 Fig.14 The voltage regulating process with the proposed active gate drive

3.4 有源驅動電路適用性驗證

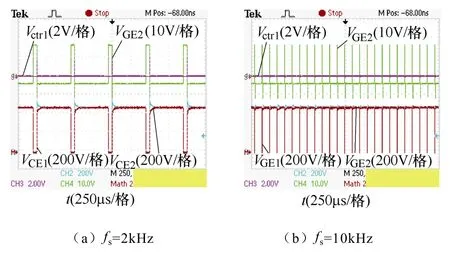

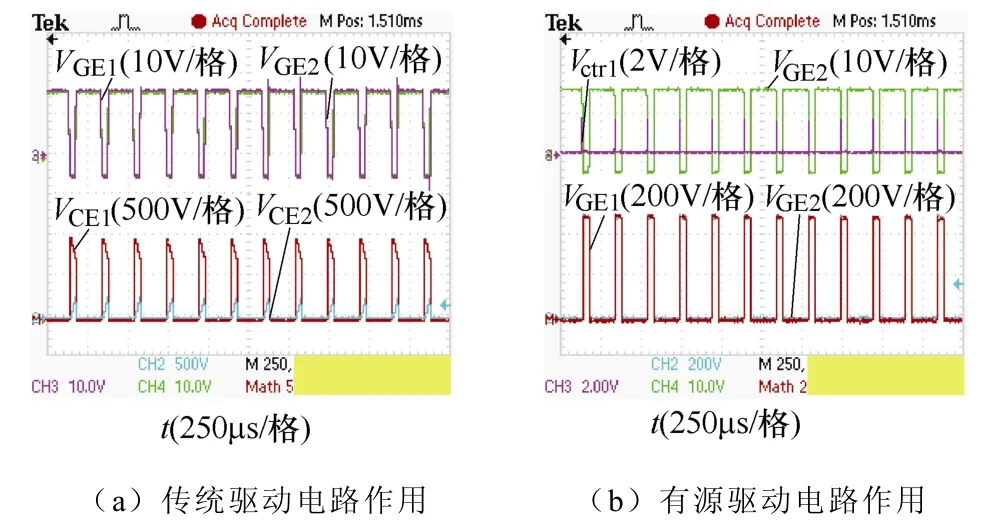

為進一步驗證該有源驅動電路在串聯IGBT電壓平衡調節中的作用,圖15給出了不同開關頻率時該有源驅動電路作用下串聯IGBT承壓波形。由于輔助電路僅于關斷瞬態激活,因此開關頻率不是影響其工作特性的因素。不同開關頻率下有源驅動電路均壓效果如圖15所示,當開關頻率fs分別為2kHz與10kHz,且tdelay=100ns時,該驅動電路作用下串聯IGBT仍可實現電壓平衡。

圖15 不同開關頻率下有源驅動電路均壓效果 Fig.15 Voltage waveforms of the series-connected IGBTs at different switching frequencies

圖16與圖17分別給出了開關占空比為50%與80%且驅動信號間延遲tdelay=100ns時,傳統驅動電路與有源驅動電路作用下各IGBT承壓波形。可以看出,不同開關占空比下,該有源驅動電路仍可實現同樣的均壓效果。

圖16 占空比為50%時有源驅動電路承壓波形 Fig.16 The voltage waveforms of the series-connected IGBTs when the duty cycle is 50%

圖17 占空比為80%時有源驅動電路承壓波形 Fig.17 The voltage waveforms of the series-connected IGBTs when the duty cycle is 80%

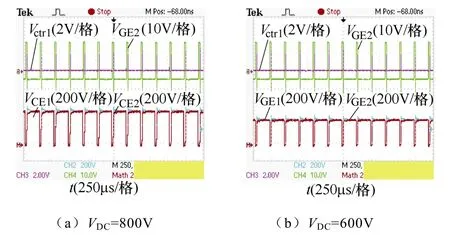

圖18給出了母線電壓降低至800V與600V時,tdelay=100ns條件下兩只IGBT承壓波形。從圖18可以看出,不同母線電壓下,應用該有源驅動電路的串聯IGBT仍可實現電壓平衡。

圖18 不同母線電壓時有源驅動電路承壓波形 Fig.18 The voltage waveforms of the series-connected IGBTs under different DC bus voltages

4 結論

本文提出了一種旨在補償串聯IGBT關斷瞬態門極放電偏差的有源驅動均壓電路,與目前應用的有源驅動均壓電路相比,該方法在實現電壓平衡控制的同時還具備以下優點:

1)輔助電路僅使用現有驅動IC輸出信號下降沿作為觸發信號,易于與傳統驅動相集成。

2)僅將IGBT靜態承壓作為采樣對象及閉環控制輸入,降低了采樣難度,提升了穩定性。

3)控制采樣頻率與變流器開關頻率一致。因此,低成本控制器(如51單片機)即可滿足要求,降低了電路成本。

4)無需引入額外的隔離控制與反饋信號,在減小了門極對地寄生電容Cp的同時減小了信號間的共模干擾[16]。

該有源驅動均壓電路在實際應用中仍存在改進的空間,未來的工作將在以下兩個方面予以優化:

1)雖然該驅動電路可應用于不同母線電壓,但 當其值變化時,參考值也需要重新設置。因此, 在母線電壓變化較大的場合,需要在驅動電路中集成VDC監測功能。

2)根據3.3節的實驗結果可以看出,由于閉環控制滯后一個開關周期,起動過程中至少有一個開關周期輔助電路是無法起到均壓作用的。文獻[13]所述的電壓斜率抑制電路可以應用于各串聯單元以避免控制初期的過電壓風險。