基于BCM5396級聯的千兆以太網交換設計及測試驗證

宛 然,張 陽,詹思維

(中國航空工業集團公司西安航空計算技術研究所,陜西 西安 710065)

0 引言

隨著核心處理平臺的綜合化程度越來越高,其內部各硬件單元的處理器節點數量逐漸增多,單片以太網交換芯片所提供的端口數量及交換容量已無法滿足系統內交換需求。本文提出了一種基于兩片BCM5396以太網交換芯片級聯的設計方案,可靈活擴展多路以太網接口,提高了系統內以太網的交換能力。同時,由于本設計體積小、集成度較高、布局布線復雜,當以太網數據傳輸流量達到設計上限時,以太網接口的物理特性將會對通信質量產生明顯的影響。因此,對該方案交換機的每一個以太網接口進行了信號一致性測試,驗證傳輸鏈路上的電氣性能指標是否滿足千兆以太網1000BASE-T標準要求。測試結果表明以太網交換機接口信號質量達到標準要求,通信穩定可靠,交換容量滿足設計指標需求。

1 硬件設計

1.1 總體架構

千兆以太網交換以2片BroadCom公司的BCM5396級聯作為交換核心,構建了30路以太網交換網絡;主要硬件電路包括以太網交換電路、物理層(PHY)電路、變壓器電路、微處理器交換配置電路、電源轉換電路和時鐘電路等。

1.2 以太網交換電路

以太網交換電路由2片BCM5396網絡交換芯片級聯構成。BCM5396是一款二層千兆以太網交換芯片,內置16個1.25 G的SerDes/SGMII接口(串行千兆介質獨立接口),最大交換容量為16 Gbps,可支持4 K MAC(介質訪問控制)地址搜索表及9 728字節巨幀,支持SPI(串行同步通信接口)和EEPROM(帶電可擦可編程只讀存儲器)兩種配置接口。每片BCM5396的15個SGMII外接PHY芯片,1個SGMII接口通過軟件配置為SerDes模式作為級聯端口。

在本設計中,BCM5396通過SGMII接口連接PHY芯片進行數據傳送。數據收發端各有一對差分信號線S_OUT+/-和S_IN+/-,發送和接收信號需要串聯0.1 uF或0.01 uF的AC耦合電容,在SGMII接口模式下發送端不需TXCLK時鐘輸入,MAC側BCM5396有參考時鐘,PHY無須提供接收端參考時鐘RXCLK,收發都可從數據中恢復參考時鐘。BCM5396通過管理配置接口MDC/MDIO對PHY芯片寄存器進行輪詢訪問,以控制PHY的行為或獲取 PHY 的狀態[1]。

BCM5396提供17個硬件配置管腳,可以通過外部上拉或下拉跳線設計完成交換芯片的初始化配置,省去軟件配置步驟。大部分硬件配置管腳可根據設計需要的功能、接口類型靈活選擇,在本設計中重點關注以下幾個配置管腳。

(1)AUTO_POLL_DIS管腳上拉關閉PHY輪詢功能。使用PHY輪詢功能時,交換芯片每個SGMII接口外接的PHY地址應與SGMII接口順序一一對應,否則交換芯片將無法讀寫PHY寄存器。由于本設計中交換芯片使用了級聯端口,無須外接PHY,因此應關閉輪詢功能。

(2)CPU_EEPROM_SEL管腳上拉選擇SPI接口配置交換芯片,若該管腳下拉則選擇EEPROM配置。

(3)HW_FWDG_EN管腳上拉使能數據轉發功能。

1.3 PHY電路

PHY電路用來連接MAC層到物理媒介,實現對被發送和接收信息的編解碼及并串/串并轉換功能。物理層PHY芯片選用MARVELL公司生產的88E1111,支持10 Mbps、100 Mbps、1 000 Mbps 3種速率自協商,支持全雙工工作模式,與MAC層接口有GMII(吉比特介質獨立接口)、RGMII(簡化吉比特介質獨立接口)、SGMII等類型,本設計中采用SGMII接口與MAC層連接。

88E1111有7個配置引腳CONFIG[6∶0],其中大部分常量可通過軟件進行配置,PHYADR[4∶0]、HWCFG_MODE[3∶0]、SEL_TWSI則需通過硬件配置完成。

PHYADR[4∶0]為PHY地址配置,每片BCM5396連接的15個PHY芯片按Port0至Port14的順序地址從“00000b”至“01110b”,每個PHY配置一個獨立地址。HWCFG_MODE[3∶0]為硬件配置模式,配置了88E1111的工作模式。本設計中88E1111工作在SGMII(不需參考時鐘)模式下,HWCFG_MODE[3∶0]=“0100b”。SEL_TWSI為接口選擇配置,為0時選擇MDC/MDIO接口,為1時選擇TWSI接口。本設計采用MDC/MDIO接口對PHY芯片寄存器進行讀寫,因此SEL_TWSI=“0b”。

1.4 變壓器電路

變壓器電路用于實現信號耦合、信號增強、高壓隔離、電磁干擾抑制等功能。本設計選用“迅達”電子的雙路千兆以太網變壓器LT2808,可滿足以太網信號鏈路傳輸低插入損耗、高返回損耗及電磁干擾(EMI)抑制要求,具有耐壓能力保護芯片避免雷擊感應的浪涌損傷,同時可節約布板面積,實現差分信號的高效傳輸。

在設計變壓器電路時需注意PHY芯片發送、接收端的驅動類型,通常分為電壓型PHY和電流型PHY。若使用電壓型PHY,則變壓器中心抽頭通過電容直接接地;若使用電流型PHY,則中心抽頭需上拉接偏置電壓,為PHY提供足夠的驅動能力,否則將出現網絡通信故障。本設計采用的88e1111為電流型PHY芯片,因此將中心抽頭上拉至2.5 V電平。

1.5 微處理器交換配置電路

配置電路用來實現以太網交換電路的配置,完成以太網交換主從模式配置、程序加載方式配置、時鐘頻率配置、接口工作模式配置等功能,通常采用EEPROM或外部主機方式配置。本設計中采用微處理器進行配置,具有低成本、低功耗、設計簡單、可靠性高、靈活性高等優點,除配置功能外,還可實現每路以太網端口的實時監控,讀取端口連接狀態、連接速率、半雙工/全雙工狀態等寄存器信息,并通過I2C總線將監控狀態上報給上位機,更有利于交換機板卡的調試維護及健康管理。

微處理器選用TI公司的CortexTM-M3系列芯片,最高工作頻率為80 MHz,內置128 KB FLASH、20 KB SRAM,具有2個SPI串行同步通信接口、2個I2C串行通信接口、3個串行異步通信接口。采用1路SPI接口復用片選信號對兩片BCM5396進行交換配置,微處理器為主設備,兩個交換芯片為從設備,微處理器可分時訪問2個交換芯片。

1.6 時鐘電路

以太網交換芯片各需提供2路2.5 V電平、25 MHz頻率的時鐘,PHY芯片時鐘采用8片2.5 V電平、25 MHz頻率的獨立時鐘源,頻率-溫度穩定度≤±50 ppm,通過時鐘驅動器為30片PHY提供時鐘。微處理器外部時鐘頻率為4~16 MHz,本設計中使用8 MHz時鐘輸入,經鎖相環PLL倍頻后,系統時鐘為48 MHz。

1.7 電源轉換電路

交換機板卡外部輸入電壓為28 V直流電源,通過DC/DC隔離電源實現28 V到5 V的電源轉換。板卡的工作電源有 3.3 V、2.5 V、1.2 V,3.3 V 為微處理器及串口供電,采用1片線性電源TPS74401實現;2.5 V和1.2 V為交換芯片和PHY芯片供電,所需的最大電流為8.5 A和11 A,選用2片LTC公司的電源轉換芯片LTM4644,可提供的最大電流為16 A,滿足設計要求。

2 軟件設計

BCM5396可通過SPI接口和EEPROM接口進行交換軟件配置,兩種接口復用同一管腳,通過寄存器CPU_EEPROM_SEL選擇接口模式。本設計中采用SPI接口配置方式,軟件開發環境為Keil5。

2.1 SPI接口

BCM5396的SPI接口分為快速和標準兩種模式,通過命令字區分,在實現中兩種模式不可同時使用,微處理器必須一直使用同一模式傳輸。

本設計中采用標準模式,MODE bit(bit4)=0,同時規定了bit[7∶5]=011 b。BCM5396作為一個單片系統,CHIP_ID=000 b。bit[0]為讀寫控制位,0表示讀,1表示寫。因此該模式中,讀操作命令字為60 h,寫操作命令字為61 h。

2.2 讀寫流程

標準SPI模式允許單字節讀和多字節寫操作,基于CPU輪詢方式監視進程。讀操作的格式為〈讀命令字〉 〈寄存器地址〉,寫操作的格式為〈寫命令字〉 〈寄存器地址〉 〈數據〉。BCM5396的寄存器采用分頁機制,每頁地址空間為256個字節,對某一寄存器進行讀寫操作時,需要先定位至該寄存器的頁,再進入寄存器位于頁的地址中。

當讀一個寄存器時,首先讀SPI狀態寄存器(地址FEh)查詢SPIF是否為0,若為0,則在頁寄存器(地址FFh)寫入要讀取的寄存器的頁,再讀取該寄存器位于頁的地址,然后再次讀SPI狀態寄存器查詢RACK,RACK為1,則可以讀取SPI數據I/O寄存器,完成讀流程。

當寫一個寄存器時,首先同樣是讀SPI狀態寄存器查詢SPIF是否為0,若為0,則在頁寄存器寫入要寫的寄存器的頁,再在該寄存器位于頁的地址中寫入要寫的數據,完成寫流程。

2.3 級聯初始化配置

BCM5396級聯端口初始化配置分為兩種方式。第一種是將級聯端口配置為SGMII模式,在該模式下兩片BCM5396的級聯端口有主從之分。具體配置操作為將主級聯端口對應的Serdes / SGMII Control 1寄存器配置為0x01F0h,SGMII主從位配置為主,并使能自動探測。從級聯端口無需進行任何配置。第二種是將級聯端口配置為FIBER模式,在該模式下兩個級聯端口直連,不區分主從。具體配置操作為分別將兩個級聯端口對應的Serdes /SGMII Control 1寄存器配置為0x01C0h,SGMII主從位配置為普通模式,關閉自動探測,FIBER Serdes模式開啟。

在軟件設計中對以上兩種方式均進行了驗證,結果顯示FIBER模式下的級聯端口通信更加穩定。

3 信號一致性測試驗證

千兆以太網1000BASE-T標準使用4對雙絞線同時進行雙向信號傳輸,測試時需對每個以太網接口的每對雙絞線都進行測試。每對傳輸線上的數據傳輸速率達到250 Mbps,由于采用5電平的PAM5信號編碼方式,實際上每對差分線上的波特率為125 MBaud,因此可選用1 GHz以上帶寬示波器[2]。為了更方便地將每路千兆以太網RJ45接口上的信號引出,加入傳輸線模型,提供信號端接收并進行以太網信號的分析,測試使用Agilent公司的N5395C以太網測試夾具并配合以太網一致性測試軟件。

千兆以太網1000BASE-T信號一致性測試項目主要有峰值電壓測試、模板測試、電平衰落測試、失真測試、共模電壓測試、主模式抖動測試等,測試時需針對不同測試項目將被測以太網接口對應的PHY芯片設置在不同測試模式下(Test Mode)。根據IEEE802.3以太網標準,Test Mode 1為發送波形測試,Test Mode 2為主模式發送抖動測試,Test Mode 3為從模式發送抖動測試,Test Mode 4為失真測試[3]。

3.1 峰值電壓、模板、電平衰落測試

峰值電壓、模板、電平衰落測試目的是為了驗證以太網端口的驅動能力,是否能夠將信號傳輸到較遠的距離,也是保證輸出端能夠發送標準的以太網電平,電平過低會導致驅動能力不足,電平過高會在鏈路中引入其他故障或干擾[3]。

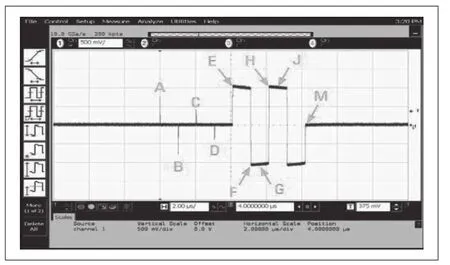

將被測以太網接口對應的PHY芯片1000BASE-T控制寄存器設置為Test Mode 1,使用以太網一致性測試軟件進行測試,波形如圖1所示。

圖1 峰值電壓、模板、電平衰落測試波形

按照IEEE802.3以太網標準要求,峰值電壓測試A、B點峰值電壓為670~820 mV,A、B點峰值電壓差值幅度小于1%,C、D點峰值電壓與A、B點峰值電壓平均值1/2的差值小于2%。模板測試要求以太網信號眼圖未壓模板。電平衰落測試要求G點、H點分別與F點、H點的電壓比值大于73.1%。實際測試結果均在電平要求范圍內,測試通過。

3.2 失真測試

將被測以太網接口對應的PHY芯片1000BASE-T控制寄存器設置為Test Mode 4,峰值失真電壓≤10 mV即測試合格。實測峰值失真電壓為2.9 mV。

3.3 共模電壓測試

共模電壓測試需在以太網的差分信號上增加外部擾動信號,將被測以太網接口對應的PHY芯片1000BASE-T控制寄存器設置為Test Mode 4,共模輸出電壓絕對值小于50 mV即測試合格。實測共模電壓為3.8 mV,測試通過。

3.4 主模式抖動測試

抖動過高會導致誤碼率增大,降低數據傳輸的精確性,影響以太網網絡傳輸性能。

將被測以太網接口對應的PHY芯片1000BASE-T控制寄存器設置為Test Mode 2,主從手動配置使能位設置為手動主從配置,主從配置位設置為主模式,使用以太網一致性測試軟件進行測試。在無濾波條件下抖動峰峰值小于1.4 ns,有濾波條件下抖動峰峰值小于0.3 ns即測試合格。實測無濾波抖動峰峰值為0.215 ns,有濾波抖動峰峰值為0.186 ns,測試通過。

4 結語

本文設計了一種基于兩片BCM5396級聯擴展30路端口的千兆以太網交換機,詳細闡述了交換機的硬件電路設計與軟件開發流程,介紹了千兆以太網1000BASE-T標準的信號一致性測試方法,并以此方法對交換機板卡的信號完整性進行了測試驗證。測試結果表明以太網交換機接口信號質量達到標準要求,通信穩定可靠,交換容量滿足設計指標需求。但是,受限于芯片選型,本設計未能實現交換機的高度集成,布板面積略大,整體功耗略高。下一步將繼續開展小型化、低功耗交換機的設計研究。