N2O 處理對背溝刻蝕金屬氧化物薄膜晶體管性能的影響*

徐華 劉京棟 蔡煒 李民 徐苗 陶洪? 鄒建華 彭俊彪

1) (廣州新視界光電科技有限公司,廣州 510530)

2) (華南理工大學,發光材料與器件國家重點實驗室,廣州 510641)

3) (季華實驗室,佛山 528000)

通過采用稀土元素鐠摻雜銦錫鋅氧化物半導體作為薄膜晶體管溝道層,成功實現了基于鋁酸的濕法背溝道刻蝕薄膜晶體管的制備.研究了N2O 等離子體處理對薄膜晶體管背溝道界面的影響,對其處理功率和時間對器件性能的影響做了具體研究.結果表明,在一定的功率和時間處理下能獲得良好的器件性能,所制備的器件具有良好的正向偏壓熱穩定性和光照條件下負向偏壓熱穩定性.高分辨透射電鏡結果顯示,該非晶結構的金屬氧化物半導體材料可以有效抵抗鋁酸的刻蝕,未發現明顯的成分偏析現象.進一步的X 射線光電能譜測試表明,N2O 等離子體處理能在界面處形成一個富氧、低載流子濃度的界面層.其一方面可以有效抵抗器件在沉積氧化硅鈍化層時等離子體對背溝道的損傷;另一方面作為氫的鈍化體,抑制了低能級施主態氫的產生,為低成本、高效的薄膜晶體管性能優化方式提供了重要參考.

1 引言

金屬氧化物半導體 (metal oxide semiconductors,MOS)薄膜晶體管 (thin film transistors,TFT) 因具有較高的遷移率、較好的均勻性、大的電流開關比、可見光透明等優點[1-3],在顯示領域具有廣泛的應用潛力,高性能、可靠的金屬氧化物薄膜晶體管已成為國內外科研院所和產業界的重點研究方向.

在MOS 材料的研究中[4-8],最具代表性的當屬氧化銦鎵鋅 (indium-gallium-zinc-oxide,IGZO),其在薄膜晶體管中的應用已有量產實績,可以滿足部分應用場景的需求.但是,隨著顯示技術的發展,IGZO 對作為驅動背板核心元件的薄膜晶體管提出了更高的標準.如高遷移率、高穩定性,特別是光照條件下的穩定性等有了更嚴苛的要求.其次,在金屬氧化物TFT 結構的探索中[9-11],比較具有應用前景的是背溝道刻蝕 (back channel etch,BCE)結構和頂柵自對準 (top-gate self-aligned,TGS)兩種結構.其中,TGS 結構最大的優點是在寄生電容方面比較突出,但是在導體化和短溝道器件的實現方面存在較大的挑戰,穩定性有待進一步提高;而BCE 結構因和當前大規模量產的硅基工藝兼容、可實現低成本制備而備受關注.但是,考慮到MOS對酸、堿、水、氧等特別敏感的問題和低電阻布線的要求[12,13],目前產業界主要基于銅酸工藝制備背溝道刻蝕的金屬氧化物薄膜晶體管.而銅酸主要的有效成分是雙氧水,存在有效期短、對金屬膜層結構敏感,甚至有爆炸的風險.基于鋁基的疊層結構金屬膜層在應用中非常成熟,需要強調的是,該結構的薄膜需要用磷酸基的強酸刻蝕液進行圖形化,在背溝道刻蝕的金屬氧化物薄膜晶體管應用中較難實現良好特性.通常,需要對制備工藝進行特殊處理.而N2O 等離子體處理是一種高效的氧源補充方式,和氧氣相比,N2O 具有更低的離化氧形成焓 (N2O:1.73 eV,O2:4.13 eV)[14],可以在相對較低的功率下離化,這樣可以避免高強度的等離子體轟擊對氧化物半導體的影響.N2O 等離子體處理在金屬氧化物薄膜晶體管的制備中已有嘗試[14-16],但在濕法背溝道刻蝕的金屬氧化物薄膜晶體管研究中還鮮有報道.

本文采用稀土鐠摻雜的氧化銦錫鋅半導體(praseodymium-indium-tin-zinc-oxide,PITZO)作為薄膜晶體管器件的溝道層,制備基于鋁酸的背溝道刻蝕金屬氧化物薄膜晶體管.通過引入N2O 等離子體處理薄膜晶體管的背溝道界面的方式,對其處理功率和時間對器件性能的影響做了具體研究.借助高分辨透射電鏡,研究該金屬氧化物半導體材料晶型結構和器件形貌.進一步通過X 射線光電能譜測試,研究了N2O 等離子體處理對薄膜影響的機理.

2 背溝道刻蝕金屬氧化物薄膜晶體管器件制備與性能

2.1 PITZO-TFT 器件制備

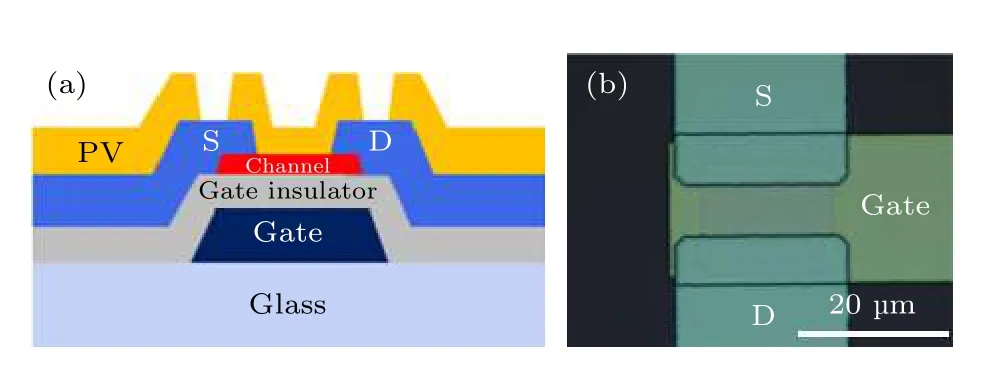

如圖1(a)所示,本文所用器件均采用BCE 型結構.首先,采用直流磁控濺射的方式在玻璃襯底上濺射一層200 nm 厚的金屬鉬 (Mo)柵極薄膜,利用濕法刻蝕對柵極薄膜進行圖形化.通過等離子體增強型化學沉積 (plasma enhanced chemical vapor deposition,PECVD) 技術制備雙層堆疊的柵絕緣層,和柵極金屬Mo 層接觸的下層為250 nm 厚的氮化硅薄膜,上層為50 nm 厚的二氧化硅薄膜,并利用干法刻蝕進行圖形化.然后,通過磁控濺射的方式分別制作一層30 nm 厚的PITZO (Pr/In/Sn/Zn=0.2/2/0.5/1 mol) 薄膜作為薄膜晶體管器件的有源層,并利用草酸進行圖形化.隨后,采用直流磁控濺射方式制備一層200 nm 厚的Mo 金屬作為源漏電極層;采用鋁酸刻蝕液,以濕法刻蝕方式進行源漏電極的圖形化.接著,利用PECVD腔室分別對器件進行不同條件的N2O 處理.具體地,保持處理時間為30 s 不變,設置N2O 的功率分別為0,50,150 W,對應的器件分別標記為Device A,Device B,Device C;以及保持N2O 的功率為150 W 不變,設置處理時間分別為10 和60 s,對應的器件分別標記為Device D,Device E.在N2O等離子體處理后不破真空,利用PECVD 制作一層300 nm 厚的二氧化硅薄膜作為鈍化層,并采用干法刻蝕進行薄膜圖形化.最后,所有器件在350 ℃的空氣氛圍中退火60 min.制備的器件顯微鏡圖如圖1(b)所示,各膜層輪廓清晰可見.

圖1 PITZO-TFT (a)結構示意圖;(b) 器件顯微鏡照片Fig.1.(a) Structure diagram and (b) microscope photo of the PITZO-TFT.

2.2 PITZO-TFT 器件性能

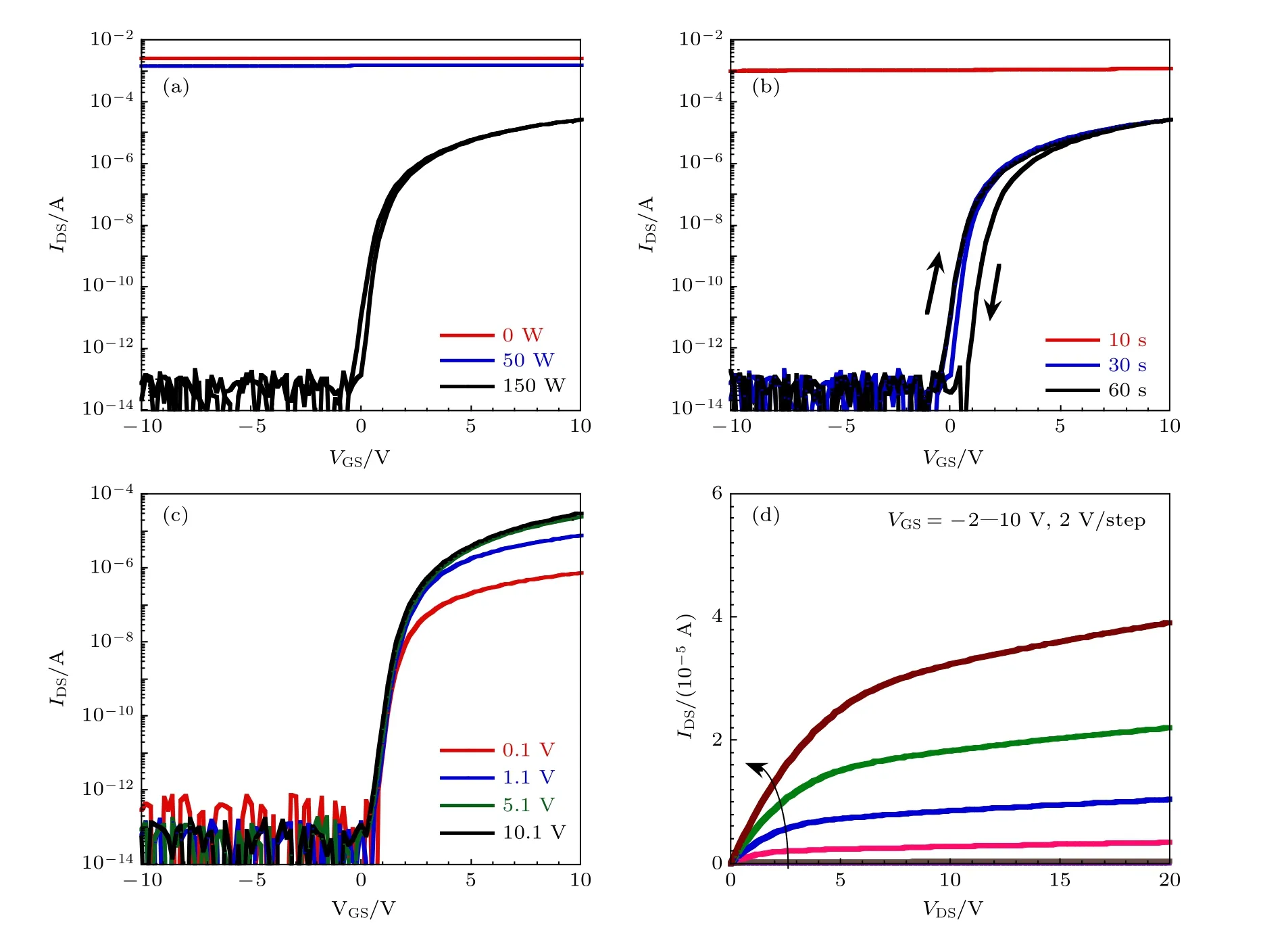

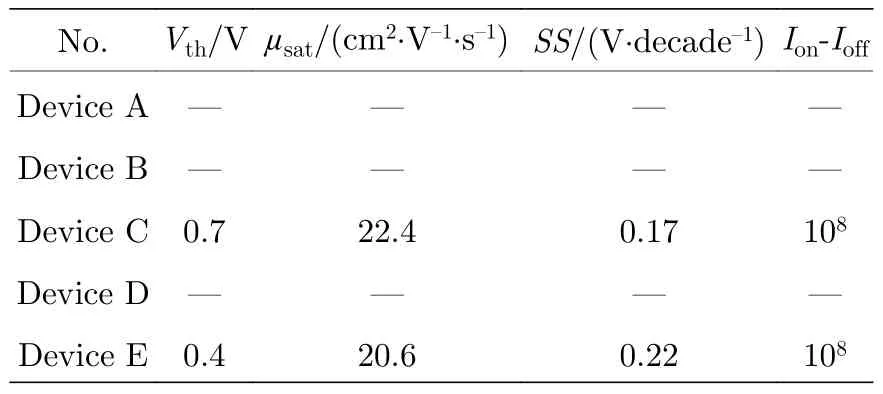

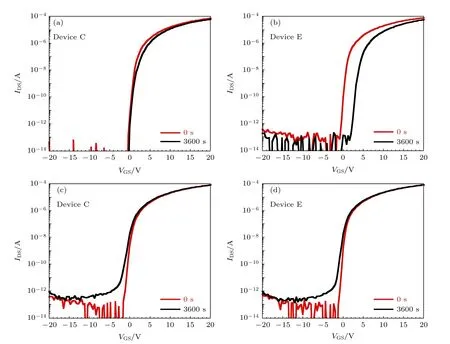

首先,固定N2O 等離子體處理時間為30 s,不同功率處理下的器件轉移曲線如圖2(a)所示.很顯然,無N2O 等離子體處理 (0 W)和低功率 (50 W)處理條件下的器件都處于“導通”狀態,二者均無開關特性;增加N2O 等離子處理功率至150 W 后,器件 (Device C)表現出了良好的開關特性.本文中器件溝道寬長比 (W/L)均為20/10 μm,轉移曲線中固定源漏電壓 (VDS)為10.1 V,器件閾值電壓 (Vth)定義為轉移曲線中源漏電流 (IDS)為1 nA時對應的柵極電壓 (VGS).通過相關參數提取可得(如表1 所列),器件Device C 對應的閾值電壓Vth為0.7 V,器件飽和遷移率 (μsat)為22.4 cm2·V—1·s—1,亞閾值擺幅 (SS) 為0.17 V/decade,電流開關比(Ion/Ioff) 約為108.進一步地,在保持N2O 等離子體處理功率為150 W 的基礎上,設置處理時間分別為10,30 和60 s.如圖2(b)所示,當處理時間為10 s 時,器件Device D 處理“導通”狀態;隨著處理時間增至30 s,也即Device C,器件表現出了良好的開關特性,無明顯的磁滯效應;當進一步增加時間至60 s 后,器件Device E 依然表現出了開關特性,但是“磁滯”效應明顯增強.和Device C 比較而言,Device E 的Vth稍有負向偏移(0.4 V),器件μsat稍有降低 (約20.6 cm2·V—1·s—1),亞閾值擺幅退化為0.22 V/decade,Ion/Ioff保持約為108.其次,為進一步評估優化器件Device C 的電學特性,圖1(c)給出不同源漏電壓 (VDS=0.1,1.1,5.1,10.1 V)下的轉移特性曲線,可以看出,器件未表現出“漏誘導勢壘變低”的現象.另外,器件Device C 的輸出特性曲線如圖1(d)所示,無電流擁擠現象,說明源漏電極和溝道層接觸良好,而且器件表現出了良好的飽和特性,這為器件的實際應用提供了堅實的基礎.

圖2 (a)不同功率和 (b) 不同時間的N2O 處理對器件轉移特性的影響;Device C (c) 不同源漏電壓下的轉移特性曲線和 (d) 輸出特性曲線Fig.2.Influence of different (a) power and (b) time treatment of N2O on the transfer characteristics of the device;(c) transfer characteristic curve under different source and drain voltages and (d) output characteristic curve of Device C.

表1 各器件性能參數表Table 1.Electronic parameters of each TFTs.

根據以上結果可知,在濕法背溝刻蝕金屬氧化物薄膜晶體管的制備中,器件背溝道受制備工藝影響較大.未經N2O 等離子體處理的薄膜晶體管直接表現出“導通”狀態,說明溝道層中載流子濃度過高,該區間柵壓無法起到調控效果.通過引入N2O 等離子體處理,可以有效改善器件的開關特性;而且,N2O 等離子體處理的功率和時間對器件性能的影響非常明顯,合適的功率和時間窗口是獲得器件優化性能的關鍵.因此,有必要對其改善機理做進一步的研究.

3 實驗結果與分析

3.1 器件偏壓穩定性評估

圖3(a)和圖3(b)分別為Device C 和Device E在正向偏壓下的熱穩定性 (positive bias temperature stress,PBTS)表征結果.其評估方式為:設置測試機臺的溫度為60 ℃,先測試初始狀態下的器件轉移特性曲線 (VGS=—20—20 V 掃描,VDS=10.1 V),緊接著加上一定的偏壓 (VGS=20 V,VDS=0 V,T=60 ℃),保持3600 s 后再次測試器件的轉移特性曲線,得到器件轉移特性的變化情況.圖3(a)和圖3(b) 的結果表明,N2O 等離子體處理時間從30 s 增加至60 s 后,器件PBTS 的閾值電壓漂移量從0.2 V 退化為3.1 V.對比Device C 和Device E 的結構和制備工藝,可推斷其和器件背溝道的狀態直接相關.根據Sheng 等[17]和Nahm 等[18]的研究結果,過多的氧誘導的缺陷態可能是其PBTS 穩定性退化的原因.簡單而言,長時間的N2O 等離子體處理產生的過量的氧間隙態作為電子俘獲中心,從而導致了器件PBTS 穩定性退化,后面將做進一步的驗證.

進一步地,為評估N2O 等離子體處理的實用性,有必要對器件在光照條件下的負偏壓熱穩定性(negative bias illumination temperature stability,NBITS) 進行表征.NBITS 的測試方式為:設置測試機臺的溫度為60 ℃,先測試初始狀態下的器件轉移特性曲線 (VGS=—20—20 V 掃描,VDS=10.1 V),接著加上一定的偏壓 (VGS=—20 V,VDS=0 V,T=60 ℃,白色LED 光源直接照射溝道區域,光強為5000 nits),保持3600 s 后再次測試器件的轉移特性曲線,得到器件轉移特性的變化情況.需要說明的是,該實驗中加偏壓后測試轉移曲線時光源未關閉.Device C 和Device E 的NBITS穩定性分別如圖3(c)和圖3(d) 所示,可以看出,二者均表現出了良好的NBITS 穩定性,Vth漂移僅為—0.5 V.根據我們前期的研究結果[8,19,20],稀土鐠元素的摻入,會在導帶底附近引入“缺陷”態,其可作為光生載流子的快速復合中心.需要指出的是,雖然Device E 的背溝道界面具有相對較多的缺陷態,但是其NBITS 穩定性依然能保持和Device C 相當.很顯然,稀土鐠元素的摻入可以有效地提高器件的NBITS 穩定性.

圖3 (a) Device C 和 (b) Device E 器件在PBTS 條件下的穩定性;(c) Device C 和 (d) Device E 器件在NBITS 條件下的穩定性Fig.3.Stability of (a) Device C and (b) Device E under PBTS conditions;stability of (c) Device C and (d) Device E under NBITS conditions.

3.2 薄膜晶體管的高分辨透射電鏡分析

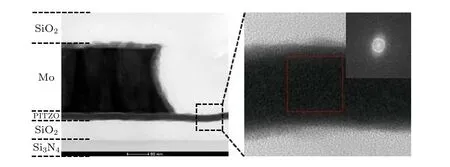

對于高可靠的薄膜晶體管而言,完整的器件結構是首先必須滿足的前提條件.因此,在前面光學顯微鏡的基礎上,有必要進一步評估該BCE 結構PITZO-TFT 的微觀形貌結構.圖4 所示為Device C 的高分辨透射電鏡 (transmission electron micrography,TEM)圖譜.很顯然,該截面TEM 圖中各膜層結構清晰可見,厚度和制備參數符合較好.需要特別指出的是,PITZO 薄膜雖然經歷強酸的源漏電極刻蝕過程,但是無明顯被刻蝕的跡象;而且,其上未發現有明顯的刻蝕殘留,表明PITZO 薄膜可以有效抵抗該強酸的刻蝕,具有較強的抗酸刻蝕特性.另外,在金屬Mo 電極上有一薄氧化層,應該和N2O 等離子體處理相關.進一步,對PITZO薄膜的晶型結構進行分析,從快速傅里葉變換圖可以清楚地判斷其為非晶結構,由于不存在晶界的問題,這保證了其在大尺寸面板中應用的可能.

圖4 TFT 器件的高分辨透射電鏡譜圖Fig.4.High-resolution transmission electron microscope spectra of TFT devices.

3.3 薄膜X 射線光電子能譜分析

在明確了器件性能和結構方面的信息后,有必要對N2O 等離子體處理的機理做深入的研究,因其對高性能器件的實現起到至關重要的作用.首先在玻璃基板上制備兩個和器件相同濺射條件下100 nm 厚的PITZO 薄膜,然后把其中一個薄膜在N2O 等離子體中進行和器件 (Device C,150 W,30 s)制備處理一致的工藝過程,再分別對這兩種薄膜進行X 射線光電子能譜 (XPS)深度剖析測試.

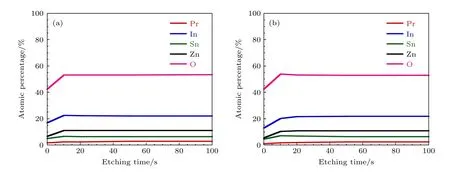

首先,兩種薄膜中各元素隨刻蝕 (Ar 離子槍)時間的分布結果如圖5(a)和圖5(b) 所示,其中圖5(a)為未經N2O 等離子體處理的薄膜樣品,圖5(b)為經N2O 等離子體處理的薄膜樣品.從圖5 可知,從元素原子含量的角度而言,二者均在表面存在一個界面區域,未經N2O 等離子體處理的樣品界面小于2 nm (Ar 離子槍刻蝕速率約為2 A/s),而經N2O 等離子體處理的樣品的界面區域擴展到小于4 nm.更深區域的元素分布無明顯區別,可以推斷該N2O 等離子體處理條件僅影響距離薄膜表面幾個納米深度區域.另外,對比兩種薄膜各元素含量的變化,未經處理的薄膜表面銦原子百分比約為16.9%,而經N2O 等離子體處理的薄膜表面銦原子百分比為12.9 %,其他主體元素含量未有明顯區別.但是,在距離薄膜表面4 nm深度后,二者各元素含量無明顯區別.考慮到銦在金屬氧化物半導體薄膜中是提供載流子遷移的通道[21],即N2O 等離子體處理會有降低遷移率的趨勢.因此,這也許是Device E 的遷移率和Device C 相比稍低的原因.

圖5 PITZO 薄膜的深度剖析X 射線光電子能譜圖 (a) 無N2O 處理;(b) N2O 處理后Fig.5.X-ray photoelectron spectroscopy depth-profile of PITZO films:(a) Without N2O treatment;(b) with N2O treatment.

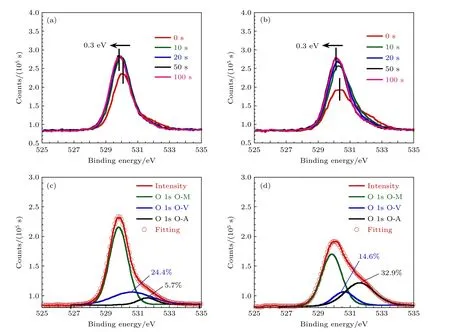

另外,上述兩種薄膜中氧元素 (O 1s)的X 射線光電子能譜和氬離子刻蝕時間的關系圖譜如圖6(a)和圖6(b) 所示.對于未經N2O 等離子體處理的薄膜,其O 1s 的峰位變化主要表現在0 和10 s 之間 (向低結合能方向偏移0.3 eV),10 s 之后無明顯位移.而經N2O 等離子體處理的薄膜,其O 1s 的峰位變化表現為0 和50 s 之間(向低結合能方向遞進偏移0.3 eV),50 s 之后無明顯位移.因此,從元素峰位的角度而言,該N2O 等離子體處理條件的影響深度約為距離薄膜表面10 nm.進一步地,對上述兩種薄膜表面 (對應0 s)的O 1s 進行高斯分峰擬合,圖6(c)和圖6(d) 分別對應未經N2O 等離子體處理和經N2O 等離子體處理的薄膜樣品.其中O 1s 圖譜可以擬合成3 個高斯峰,OM(529.8 eV),O-V(530.7 eV)和 O-A(531.7 eV),分別代表金屬結合氧、缺位氧和吸附氧,通過擬合峰面積可推知各峰位的占比情況.從圖6(c)和圖6(d) 可知,經N2O 等離子體處理后,薄膜中的O-V 占比由24.4 %降為14.6 %,表明薄膜中的氧空位濃度有一定程度的降低.大量的研究表明[22],金屬氧化物半導體中氧空位是其載流子的一個主要來源,也即薄膜中載流子濃度會有一定程度的降低.這和我們霍爾測試的結果相符合,其載流子濃度由未處理時的3.46 × 1018cm—3降低至處理后的4.49 × 1016cm—3.需要特別指出的是,未經N2O等離子體處理的薄膜中O-A 占比為5.7 %,而經N2O 等離子體處理的薄膜中O-A 占比高達32.9%.上述結果表明,N2O 等離子體處理能在薄膜表面形成一個富氧、低載流子濃度的界面層.

圖6 PITZO 薄膜在 (a) 無N2O 處理和 (b) N2O 處理后O 1s 的XPS 譜圖隨刻蝕時間的關系;Ar 離子槍刻蝕前 (c) 無N2O 處理和 (d) N2O 處理后薄膜O 1s 的擬合XPS 圖譜Fig.6.The O 1s XPS spectra of the PITZO films (a) without N2O and (b) with N2O treatment related with the Ar ion gun etching time.Fitted O 1s XPS of the PITZO thin films (c) without N2O and (d) with N2O treatment before Ar ion gun etching.

根據相關的研究報道[14,16,23],類似的背溝道刻蝕型結構的器件呈“導通”狀態(失去柵控的開關特性),其原因主要有兩種情況.其一是器件的背溝道區域存在成分的偏析,即存在低電阻率(如高銦含量)的界面層,使得器件處于“導通”狀態;另外一種是在PECVD 沉積二氧化硅鈍化層的時候引入過多貢獻電子的氫,以及由于等離子體轟擊的影響而產生額外的缺陷.因此,通常鈍化層沉積后,器件需要進行退火等相關工藝的處理.我們的器件亦存在該現象(見圖2),未經處理的器件處于“導通”狀態,只有當N2O 等離子體處理的功率增加至150 W,處理時間大于30 s 后,器件才表現出正常的開關特性.結合前面高分辨透射電鏡的表征結果,器件的溝道層和氧化硅層的界面清晰,未發現有成分偏析層;而且溝道層未有明顯被刻蝕的現象.我們推斷,器件處于“導通”狀態主要和鈍化層的制備過程有關.根據XPS 表征的結果,N2O 等離子體處理的溝道層薄膜在表面存在一個富氧、低載流子濃度的界面層.因此,我們推測N2O 等離子體處理一方面能對器件背溝道的一些原子或分子基團進行化學氧化和物理轟擊,在背溝道界面形成一個富氧、低載流子濃度的界面,可以有效抵抗PECVD 沉積氧化硅時氫的引入和等離子體轟擊的影響.原因可能是弱結合的吸附氧可以作為氫的鈍化體,抑制作為施主的低能級間隙氫的產生,這和Kang[24]等的研究有類似的效果.具體地,當N2O 等離子體處理功率較低或時間較短時,形成的界面層不足以抵抗PECVD 沉積氧化硅時的影響,器件表現為“導通”狀態.另一方面,當N2O 等離子體處理時間過長時,產生了過多的吸附氧態,從而引入了過量的電子缺陷[25],致使器件的“磁滯”現象明顯和PBTS穩定性的退化.因此,合適的N2O 等離子體處理條件是獲得優化器件性能的關鍵,需要根據具體材料具體設定.以上可知,N2O 等離子體處理是一種低成本、高效的薄膜晶體管性能優化方式,其在低溫工藝或溶液法工藝中可能會有一些特別的應用,相關研究還在進行中.

4 結論

本文通過采用稀土元素鐠摻雜銦錫鋅氧化物半導體作為薄膜晶體管溝道層(能有效抵抗鋁酸的刻蝕),成功實現了基于強酸的濕法背溝道刻蝕薄膜晶體管的制備.進一步引入N2O 等離子體處理薄膜晶體管的背溝道界面的方式,對處理功率和時間對器件性能的影響做了具體的研究.結果表明,在一定的功率和時間處理下能獲得良好的器件性能,所制備的器件具有良好的PBTS 和NBTIS 穩定性.高分辨透射電鏡結果顯示,該非晶結構的金屬氧化物半導體材料可以有效抵抗鋁酸的刻蝕,在器件的制備過程中未見其厚度有明顯的變化.進一步的X 射線光電能譜測試表明,N2O 等離子體處理能在界面處形成一個富氧、低載流子濃度的界面層,有效地修復器件背溝道的損傷以及抵抗鈍化層沉積的影響.本文提供了一種低成本、高效的薄膜晶體管性能優化方式,在實際產業化中具有廣闊的應用前景.