一種高性能八通道CAN 集線器方法

陽樂凱

(廣州致遠電子股份有限公司,廣東 廣州 510641)

我們知道,強大的網絡可以為系統的穩定運行提供可靠的保障,通信網絡可以認為是控制系統的中樞神經系統。CAN 總線控制系統的網絡搭建應在早期給予足夠的重視,做到網絡總體規劃,合理設計及安裝,總的來說,網絡搭建需要做好以下幾個步驟的工作才能保障總線長期穩定的運行。

本產品實現8 通道CAN 集線器功能,實現8 個通道CAN 幀接收、緩存、幀映射、幀轉發等功能。通過UART(USB 或RS232)使用類似ModBus 協議與上位機通信,實現CAN 集線器的功能配置。CAN 集線器能實現多個CAN 網絡的透明連接,可以在總線級別實現復雜結構的多點連接;CAN 集線器使得主干網絡沒有支線長度限制,網絡中任意兩個節點可以到達協議距離,該設備具有8 個通信端口,每個端口都有獨立的CAN 收發器,能倍增節點數目,因此,在提供自由的布線方式的同時,也解除了系統總線上CAN 收發器最大節點數驅動限制。每個端口還具備檢測總線活躍及總線故障指示燈,方便觀察CAN 總線網絡工作狀態。CAN 集線器可用于波特率高達1Mbps 的CAN 網絡,所有通道均可在不同的波特率下工作,其符合CAN 規范2.0A(11 位CAN 標識符)和2.0B(29 位CAN 標識符),支持透明的,協議獨立的CAN 消息傳輸,使其適用于多種應用。[1]

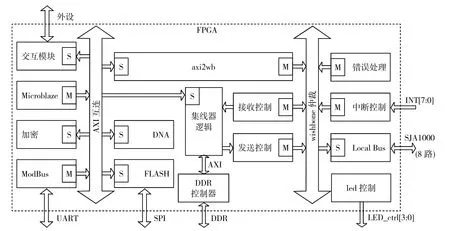

1 總體框圖

整個系統采用FPGA+SJF1000 方式,FPGA 負責將SJA1000 的CAN 數據波特率、路由表、濾波表、幀映射的規則進行各路之間的轉發,通過FPGA 的串口實現產品的配置和監控。本設計主要實現8 通道CAN 的集線器功能,實現8 通道之間的轉發和幀映射功能,實現框圖見圖1。主要由wishbone 仲裁部分和AXI 互連部分各模塊組成。

圖1 內部設計框圖

wishbone 部分各模塊實現8 通道sja1000 的管理。LocalBus 主要實現與8 通道sja1000 的通信;中斷控制實現對sja1000 中斷的接收和管理;錯誤處理模塊實現各通道的錯誤自動處理;接收控制和發送控制配合集線器邏輯實現本設計的核心功能——幀緩存、幀映射和路由等功能;axi2wb 模塊為通過AXI 配置各通道sja1000 提供接口,實現Microblaze 對各通道sja1000 的配置。[2]

AXI 互連部分主要實現上位機對集線器功能的控制。其中ModBus 模塊主要實現通過UART 與上位機通信,UART 可以通過USB 或RS232 兩種UART,兩種UART 會自動切換,當有USB 插入時則使用USB 轉UART 的ft232 的串口,沒有USB 插入時則自動切換到RS232 的串口來通信;加密和DNA 模塊主要實現對固件的加密;flash 模塊主要實現信息的存儲,包括固件、配置信息和加密信息等;交互模塊主要實現對外設的控制和與上位機的交互操作;axi2wb 模塊實現對各通道sja1000 的配置接口;Microblaze 用于實現以上功能的控制和與上位機的交互,上電后實現對固件的加密驗證,實現從flash 讀取上位機的配置并將其配置到指定的sja1000 中或集線器邏輯中,并通過交互模塊對其它各外設的控制和與上位機的交互。

集線器邏輯實現幀緩存、幀映射和轉發等功能。集線器邏輯從接收控制模塊接收幀后通過AXI 接口和DDR 控制器將幀緩存到外部DDR3 中;當能發送時從DDR 中讀取出來,并根據配置來映射幀并轉發到設置的通道中,通過發送控制模塊發送到sja1000。

2 設計實現

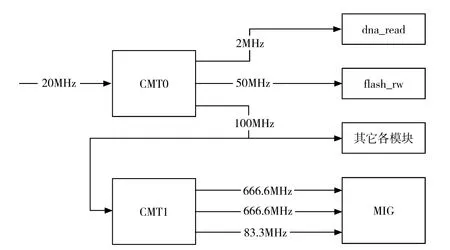

2.1 各模塊時鐘關系

本設計中各模塊時鐘關系如圖2,外部輸入時鐘20MHz,通過CMT0 生成100MHz 主時鐘到各模塊;同時也輸入到CMT1 中用于生成MIG(DDR 控制)的各時鐘(6666.6MHz 差分時鐘和83.3MHz 時鐘);另外,由于flash 最大支持80MHz,這里使用CMT0 生成的50MHz 時鐘;DNA 讀取模塊中DNA 原語(Spartan-6)中最大只支持2MHz,所以DNA 模塊使用CMT0 生成的2MHz 時鐘讀取器件DNA。

圖2 各模塊時鐘關系

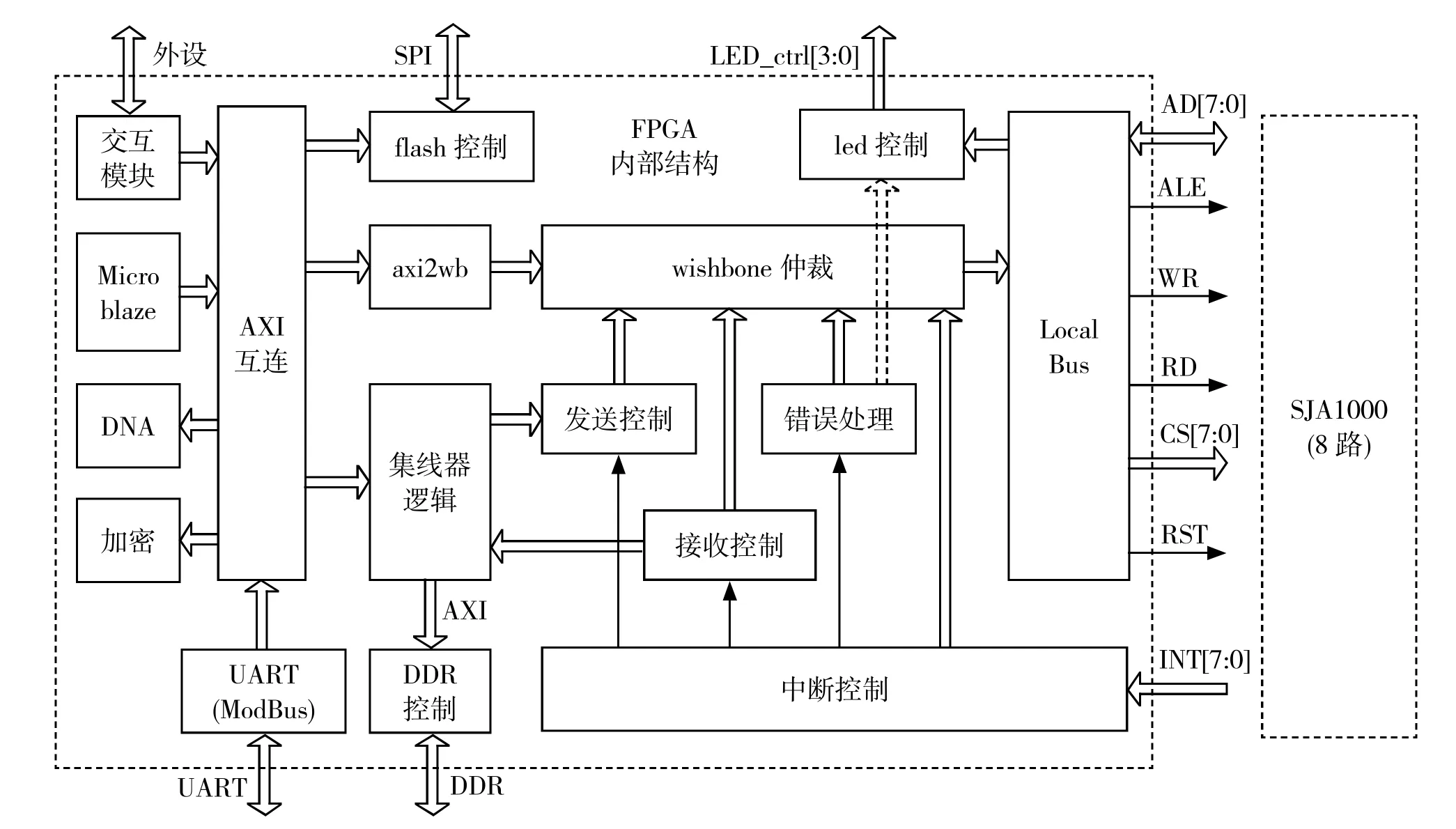

2.2 內部詳細結構

CANHub-AS8 內部詳細結構如圖3,sja1000 控制模塊主要有localbus 模塊、中斷控制模塊、錯誤處理模塊、接收控制模塊和發送控制模塊;與上位機通信主要有ModBus 模塊、交互模塊、flash 控制模塊和Microblaze;加密部分主要有加密模塊和DNA 模塊,加密信息存入flash 中;axi2wb 模塊主要實現sja1000 的配置;集線器邏輯主要實現幀映射、路由轉發和幀緩存等。

圖3 集線器內部詳細結構

sja1000 配置和與上位機通信的各操作主要有Micro blaze 實現,Microblaze 軟件控制流程如圖3,主要實現上電復位后對加密的驗證;從flash 讀取設備序列號存入寄存器操作;初始化各通道sja1000;外部按鈕的處理和USB 插入和拔出的處理等;對上位機發送命令的處理等。[3-7]

3 結語

對于現有技術的控制方式,由于ARM 處理速度受限制,當需要8 路CAN 通信同時使用的時候,經常出現丟幀、幀重復等錯誤,本設計采用FPGA 作為主控,由于FPGA 接收到中斷只要幾個時鐘周期(幾十ns)就可以開始處理,而ARM 收到中斷需要指令跳轉,而且還不止一次跳轉,各種計算也是串行的,而FPGA 中各種計算都是并行的,比如ARM 接收到一幀的1Byte就要存儲到內存,這個過程要先接收1Byte 再寫入內存,不能同時開始,而且寫內存的時間也不短;而FPGA中在收到1Byte 后存入寄存器(很快,一個時鐘周期=10ns),在寫入緩存(其實寫入緩存也很快)的同時就可以繼續接收下1Byte 了,大大提升了處理速度。