基于RISC-V 和密碼協處理器的SOC 設計

明洋,曲英杰

(青島科技大學信息科學技術學院,山東青島 266061)

隨著工業互聯網和物聯網關鍵技術的發展,越來越多的嵌入式設備應用于工業生產和社會應用中,隨之而來的網絡安全和隱私問題也愈發嚴重[1-2],IoT(Internet of Things,物聯網)設備機器及其傳感器所產生的大量的敏感數據需要通過加密的方式進行保存和傳輸,但是拘泥于其超低的功耗和有限的計算資源無法進行全面有效地部署[3]。

加解密算法可以用軟件和硬件兩種方式實現,使用軟件實現,利用CPU 中原有的計算資源去做數據加解密的效率是非常低的。對延遲敏感的物聯網設備,為其擴展加解密專用的協處理器是提高加解密效率的有效解決方式[4-7]。文獻[8]基于ARM 平臺設計實現了SM2 算法擴展的SOC,但是在實際應用中,為了提高加密效率,經常會使用多種算法復合加密的方式進行[9-10],AES 和RSA 算法分屬對稱和不對稱密碼算法,在國際上使用廣泛。基于這兩種密碼算法設計開發密碼協處理器,搭配蜂鳥E203 MCU 組成適用于嵌入式應用場景的信息安全SOC。

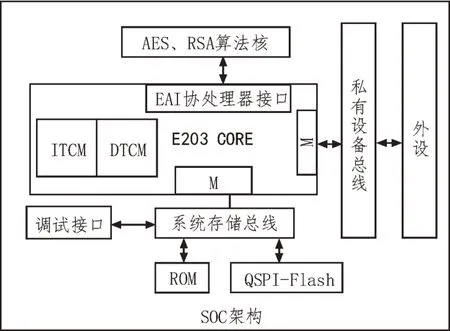

1 SOC體系結構設計

在開源蜂鳥E203 MCU基礎上,通過EAI(Extension Accelerator Interface)接口設計擴展AES、RSA 算法核,整個SOC 的體系結構如圖1 所示,EAI 接口是通過RISC-V 指令集中預留的Custom 指令擴展協處理器的接口。協處理器可通過EAI 接口中的存儲器訪存通道調用E203 核內的存儲器資源,配合E203 內核完成加解密的任務。

圖1 SOC系統架構

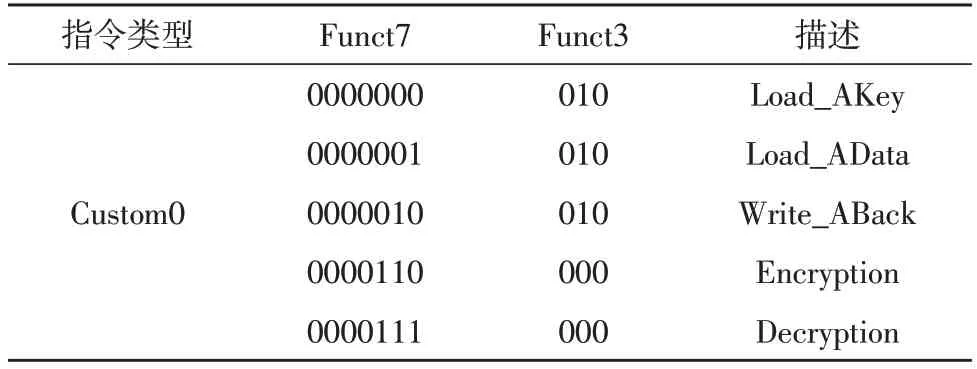

RISC-V 32 位指令集中預留了4 條Custom 指令,指令12-14 位為控制讀源寄存器和寫目標寄存器的Funct3 區間,25-31 位為作為額外編碼空間的Funct7區間。在本設計中,AES 使用Custom0,RSA 使用Custom1,并通過對Funct3 和Funct7 區間進行編碼;如表1 與表2 所示,擴展出加載數據,開始加解密以及寫回數據的對應指令。

表1 Custum0擴展指令定義

表2 Custom1擴展指令定義

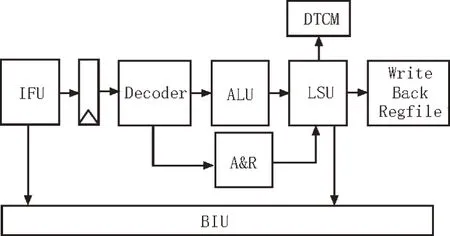

如圖2 所示,密碼協處理器核A&R(AES 和RSA)在蜂鳥E203 MCU 兩級流水線的位置與核內的ALU(Arithmetic and Logic Unit,算術邏輯單元)平行。當譯碼器譯到Custom 指令時,就會將指令以及所用的操作數通過EAI 接口轉發到協處理器中進行二次譯碼,完成對協處理的控制;通過EAI 接口的存儲器訪問通道占用LSU(Load Storage Unit,讀寫存儲器單元),訪存MCU 內部的存儲器資源,完成數據在MCU 與協處理之間的傳輸。

圖2 協處理器在MCU流水線的位置

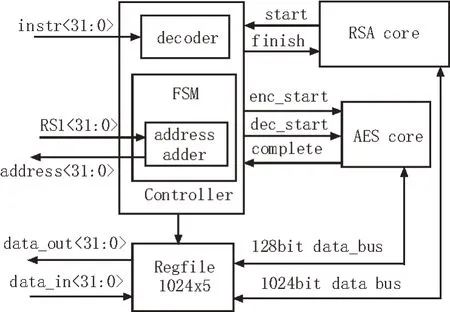

2 密碼協處理器設計

如圖3 所示,協處理器核主要由控制單元、寄存器堆和AES、RSA 算法核組成。譯碼器在指令請求通道中譯到協處理器對應的Custom 指令,會立刻通過指令反饋通道給MCU 反饋,進入工作態或者進入數據傳輸狀態。協處理器內部設置了5×1 024 bit的寄存器堆,在訪問DTCM(Data Tightly Coupled Memory,數據緊耦合存儲器)存儲的數據時,將數據暫存在寄存器堆中,等待分組數據完整加載后,再傳至AES、RSA 算法核進行運算。數據傳輸完畢后,就會關閉存儲器訪問通道,使協處理器單獨工作。

圖3 協處理器系統架構圖

為了更高效地利用EAI 接口的存儲器訪存通道,在協處理內部設計了地址自增的邏輯,使用EAI接口中的32 位數據總線,協處理器可以在32 個周期內完成1 024 位數據的傳輸。當協處理器完成加解密運算后,會將結果保存到協處理器的Regfile中,AES、RSA 算法核可以繼續進行下一組任務,控制器單獨響應程序中的寫回指令,將計算結果寫回到MCU,整個過程在MCU 內軟件程序的控制下完成。

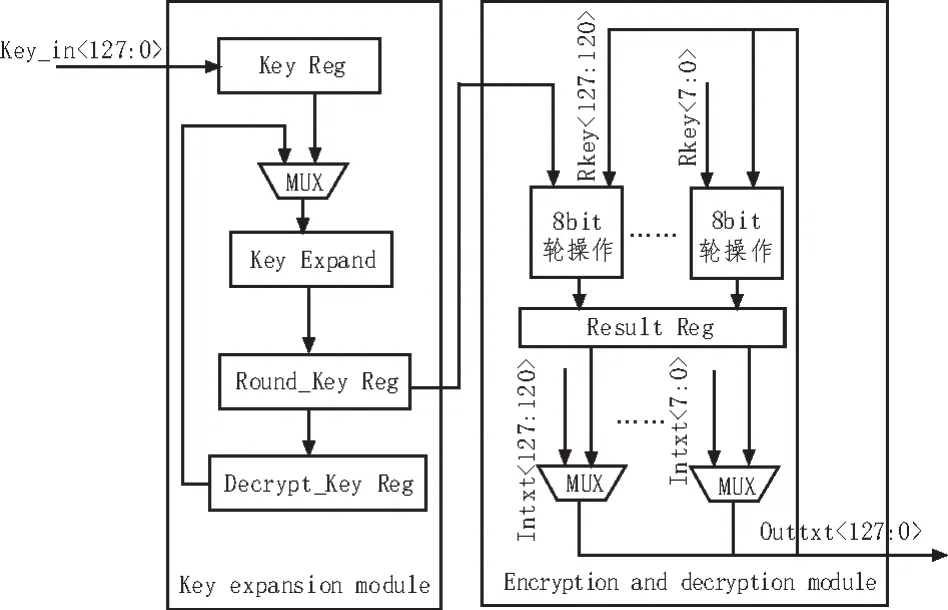

2.1 AES算法核設計

AES 算法主要分兩部分——加解密算法和密鑰擴展算法,是迭代型分組密碼算法。加解密運算主要由四種變換組成,分別是SubBytes(S 盒變換)、ShiftRow(行移位變換)、MixColumn(列混合變換)、AddRoundKey(輪密鑰加變換)[11]。該文實現的是128 bit 密鑰長度的AES 算法,前Nr輪操作相同,Nr+1 輪所做操作缺少MixCloumn,但仍可通過復用前Nr輪的邏輯電路進行運算。

為了降低ASIC(Application Specific Integrated Circuit,專用集成電路)實現的資源開銷,摒棄了使用寄存器堆或者RAM(Random Access Memory,隨機存取存儲器)單元實現S 盒變換的方式,而采用組合邏輯實現。除此之外,為了盡量減少核內寄存器的使用,如圖4 所示,采用在線實時產生輪密鑰的方法,大量減少保存輪密鑰所需的寄存器,且明文密文共享一個寄存器。整個AES 核僅使用4 組128 位的寄存器,較傳統實現方法,節省了9 組128 位的寄存器。對于AES 算法中多輪迭代的結構,僅需實現一輪電路通過FSM(Finite State Machine,有限狀態機)控制分時復用,大大減少了電路規模。同時,為了保證AES 的加解密速度,并沒有采用S 盒復用的架構,AES 核內同時實例化了16 個S盒,保留了AES 算法內部固有的并行性,使得輪邏輯可以高速運行。

圖4 AES 的數據路徑

2.2 RSA算法核設計

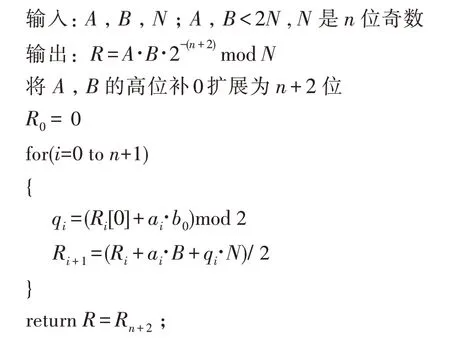

RSA 作為一種經典的非對稱密碼算法,其可靠性在于大數的因式分解,其系統核心是模冪運算P=ME(modn)。設計采用基于改進的蒙哥馬利算法的R-L 掃描法實現模冪運算,算法需要兩個操作數進行模乘循環n次實現。如算法1 所示,模乘主要是通過基2 的蒙哥馬利算法,轉化成模加運算和移位操作實現。

算法1:(改進的蒙哥馬利算法)

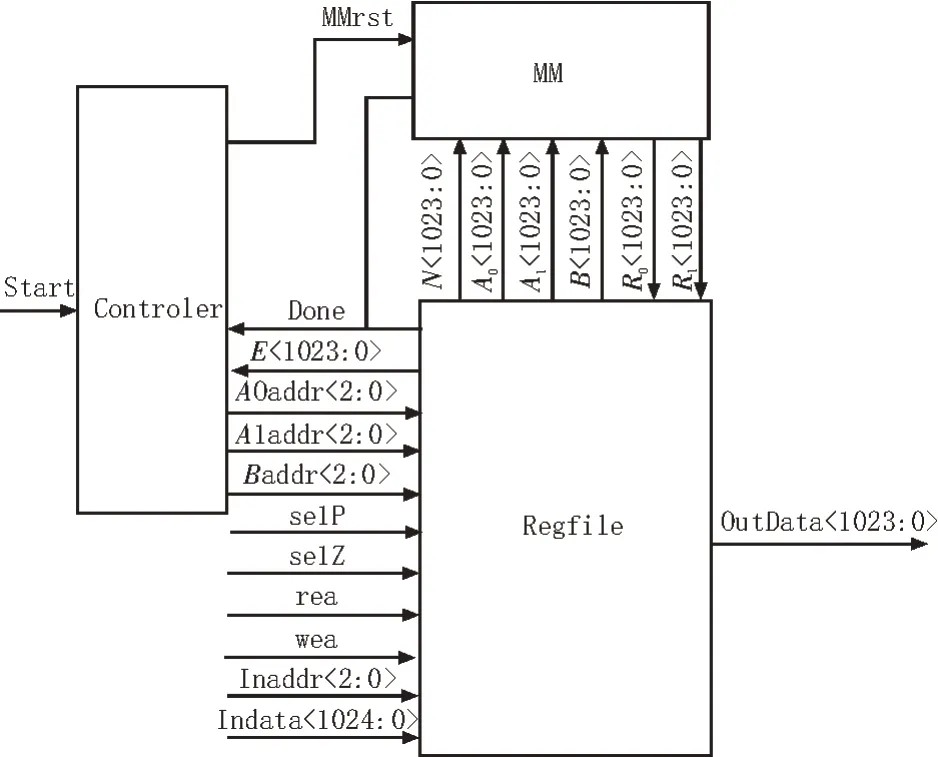

如圖5 所示,RSA 算法核由控制模塊(Control),蒙哥馬利模乘模塊(MM)和寄存器堆(Regfile)組成,參數N,C需要在軟件部分提前計算,通過Indata 端口直接輸入至RSA 核中,由RSA 核完成模冪運算最終完成加解密流程。為了保證RSA 核的運算速度,MM 模塊內部采用脈動陣列結構來解決長進位鏈的問題。為了減小MM 的面積資源開銷,僅實現一行脈動陣列結構,將1 024 位加法分成32 個32 位加法器模塊,并進行復用。

圖5 RSA的系統架構

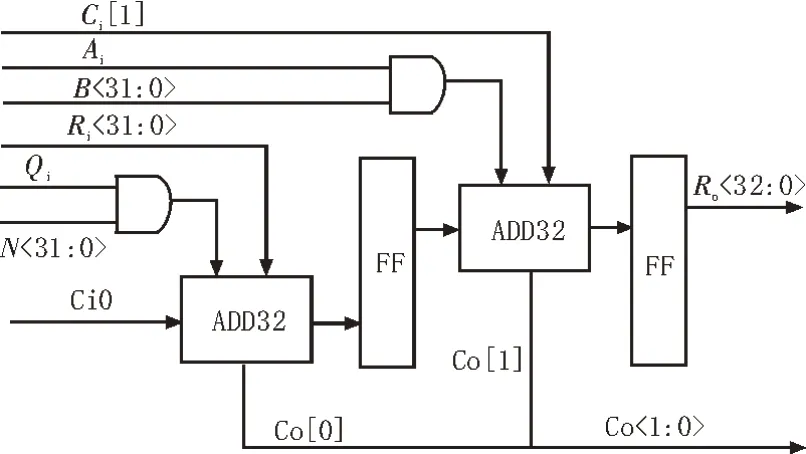

考慮到加法器模塊的復用,對蒙哥馬利模乘模塊中的加法器進行了重新設計,如圖6 所示,將qi的計算放到模塊外,模塊由兩個32 bit 的加法器組成,中間插入兩級寄存器,形成流水線,分別計算Ri中的兩次加法。

圖6 加法器的結構設計

3 實驗結果與分析

在華虹40 nm 工藝下單獨對AES 進行綜合,并對其進行靜態時序分析,其主頻可達400 MHz,面積為30 805 μm2,經過詳細的物理設計后,版圖的面積為44 944 μm2(212 μm×212 μm),版圖后的靜態時序分析結果與綜合后的一致。根據設計中的電路結構,13 個時鐘周期即可完成一次128 bit 的加/解密,估算數據吞吐率為3.9 Gbps,對比同為邏輯復用結構的低開銷ASIC 實現AES 算法的方案,如表3 所示,雖然面積要比同為低開銷設計的相關研究要大,但數據吞吐率與面積之比,該設計仍有較大優勢。造成這一現象的原因主要是設計的側重點不同,如文獻[12]瞄準的是超小面積,而該文的目的是在速度與面積之間達到平衡。

表3 AES ASIC實現與其他文獻的對比

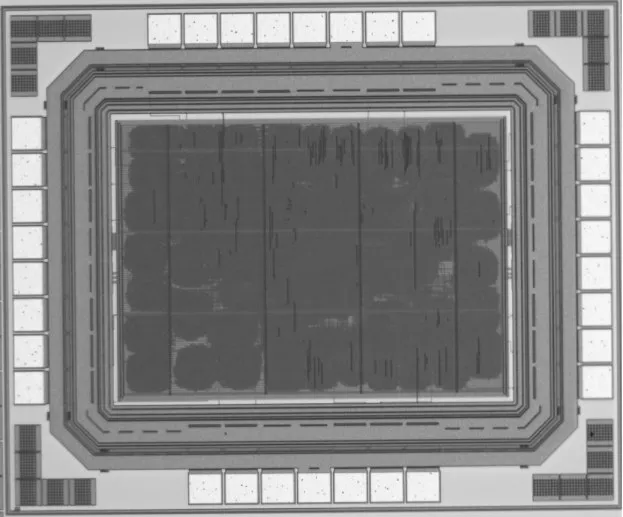

設計中AES 算法核已在SMIC180 nm 工藝下順利流片,圖7為流片后的顯微照片。由于IO pad(Input&Output pad,輸入輸出端口)數量和性能的限制,設計改為8 bit輸入輸出,芯片尺寸為1 256 μm×1 028 μm,主頻可達100 MHz,數據吞吐率達980 Mbps。

圖7 AES芯片顯微照片

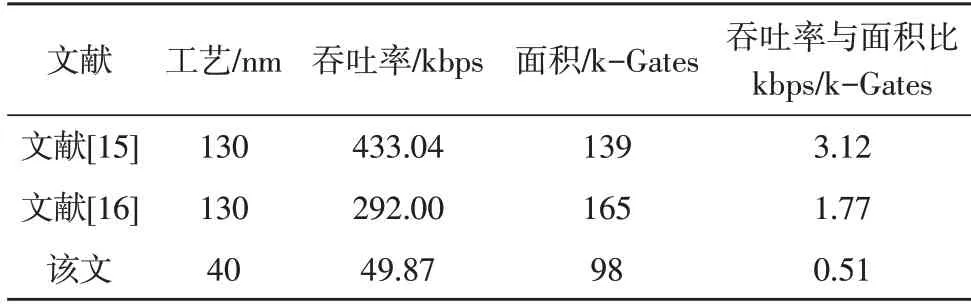

單獨對RSA 算法核在華虹40 nm 工藝下綜合,所用標準單元面積為94 552 μm2,主頻可達到100 MHz,對其進行詳細的物理設計后,面積為129 600 μm2(360 μm×360 μm),版圖后的靜態時序分析結果與綜合后一致,根據蒙哥馬利模乘模塊的運算流程分析,1 024 bit RSA 共需執行1 026 次模乘,單次模乘所需要的時鐘周期數為[2×(1 024+2)+1],可以估算一次RSA 加密所需要的時間為20.53 ms,吞吐率估算為49.87 kbps,對比同為低開銷ASIC 實現RSA 算法的方案,如表4 所示,所用等效門數與文獻[15]相比減少了29.5%。

表4 RSA ASIC實現與文獻的對比

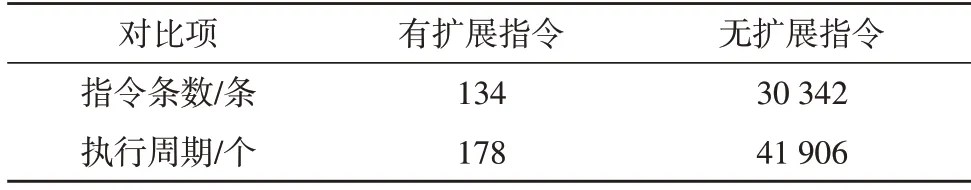

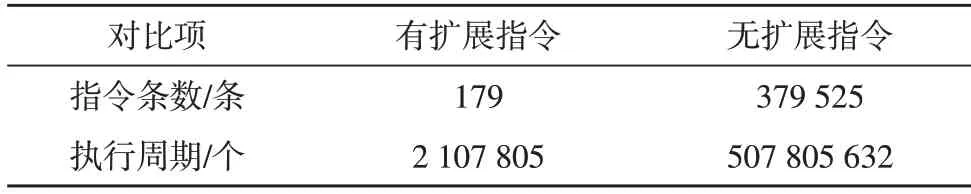

在Xlinx-Artix 7 系列開發板上做SOC 的軟硬件聯合測試,測試之前分別編寫使用協處理器和不使用協處理器的C 程序,使用RISC-V 的編譯工具編譯后,通過JTAG(Joint Test Action Group,聯合測試工作組)接口將其上載到FPGA(Field Programmable Gate Array,可編程門陣列)開發板上。通過測試可見,AES、RSA協處理核可以正常進行加解密,如表5、6所示,與沒有使用協處理器的AES 和RSA 算法程序相比,128 bit AES 加解密所用的處理器周期數減少為235.42,1 024 bit RSA 所用的處理器周期數減少了240.92。

表5 AES 有/無擴展指令所用時鐘周期和指令條數對比

表6 RSA有/無擴展指令所用指令條數核時鐘周期對比

4 結束語

面向工業互聯網和物聯網的加密應用場景,使用EAI 接口將AES、RSA 算法核擴展至蜂鳥E203 MCU上,完成了復合加密場景的RISC-V SOC 的設計,針對協處理器核的ASIC 實現面積資源與運算速度之間的平衡設計。在SOC 的軟硬件測試中可以看出,相對于無協處理器,AES 和RSA 的處理速度都得到了很大的提升。