低功耗可配置CIC 濾波器設計

高敏 ,于宗光 ,萬書芹,邵杰

(1.江南大學 物聯網工程學院,江蘇 無錫 214122;2.中國電子科技集團公司第五十八研究所,江蘇 無錫 214035)

級聯積分梳狀(Cascade Integral Comb,CIC)濾波器只包含加法器和寄存器,因具有設計實現簡單、運行速度快并且所需資源少等特點[1],作為常用模塊應用于數字下變頻(DDC)和數字上變頻(DUC)系統中[2-3]。伴隨集成電路的高速發展,傳統型CIC 濾波器結構已經不能滿足工程需求,設計低功耗可配置的CIC 濾波器結構成為當前產業的發展趨勢。

梅海軍等[4]提出采用非遞歸濾波結構以降低CIC濾波器的整體功耗,但額外引入濾波系數且采樣因子固定(2 的整數倍),難以適應多樣需求。高維等[5~6]引入非遞歸多相分解結構,雖有效降低功耗,但難以復用同一電路以實現不同的抽取倍數。為克服非遞歸形式的缺陷,王堯等[7]采用遞歸濾波結構,實現多抽取率的CIC 濾波器,但功耗和面積過高。為改善性能,王璞等[8]采用Hogenauer 剪除算法,減小內部寄存器位寬,能在一定程度上降低功耗并減小面積,但是數據轉換精度不夠高。

為降低功耗和設計面積,并滿足多種輸入信號帶寬下對轉換精度的要求,本文提出一種基于半字節串行算法的可配置CIC 濾波器,通過優化內部位寬,并在不同采樣因子下復用邏輯電路,可降低系統功耗和提高資源使用率。信道帶寬配置模塊提供2~16 倍范圍內的可編程采樣因子,以實現帶寬可變功能。增益校正模塊優化末級輸出有效精度并減小信號失真。為減少硬件資源開銷,采用正則有符號數(Canonic Signed Digit,CSD)編碼表示法對系數進行編碼,并利用移位替代乘法運算,最終基于65 nm COMS 標準單元工藝庫完成DC 綜合,結果表明所設計的數字濾波器在低功耗方面具有較大優勢。

1 基本原理

1.1 CIC 濾波器

1.1.1 單級CIC 濾波器

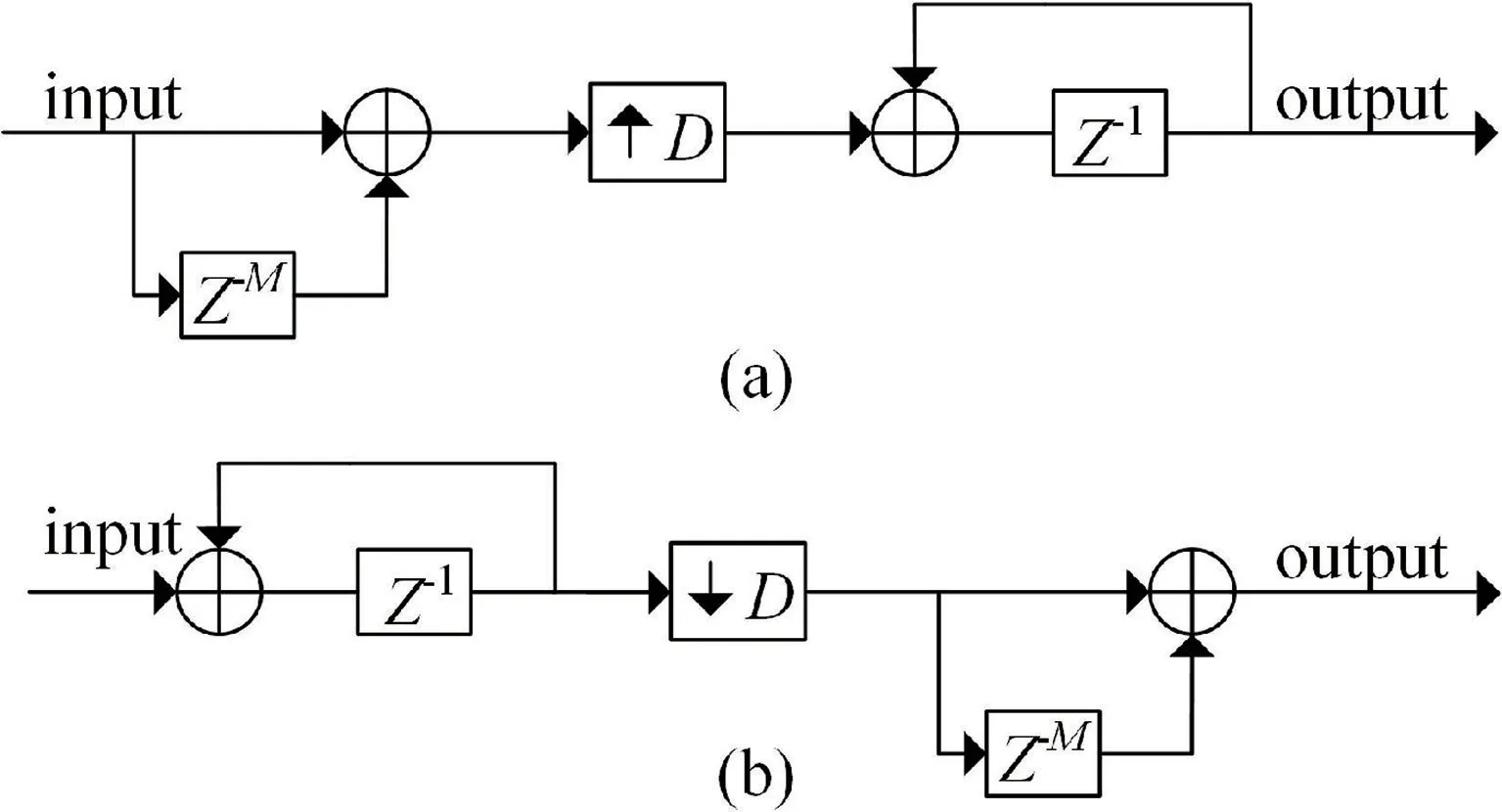

單級CIC 濾波器是一種FIR 濾波器,具有線性相位特性[9],主要由積分器和梳狀濾波器級聯構成。根據級聯順序的不同,可構成CIC 插值和抽取濾波器[10],分別如圖1(a)和(b)所示。其中,D為抽取/插值因子,M為延遲因子。

圖1 單級CIC 濾波器結構。(a) CIC 插值濾波器結構;(b) CIC 抽取濾波器結構Fig.1 The structure of single-stage CIC filter.(a) The structure of CIC interpolation filter;(b) The structure of CIC decimation filter

CIC 濾波器的傳遞函數為:

將z=ejω代入式(1),可得單級CIC 濾波器的幅頻響應為:

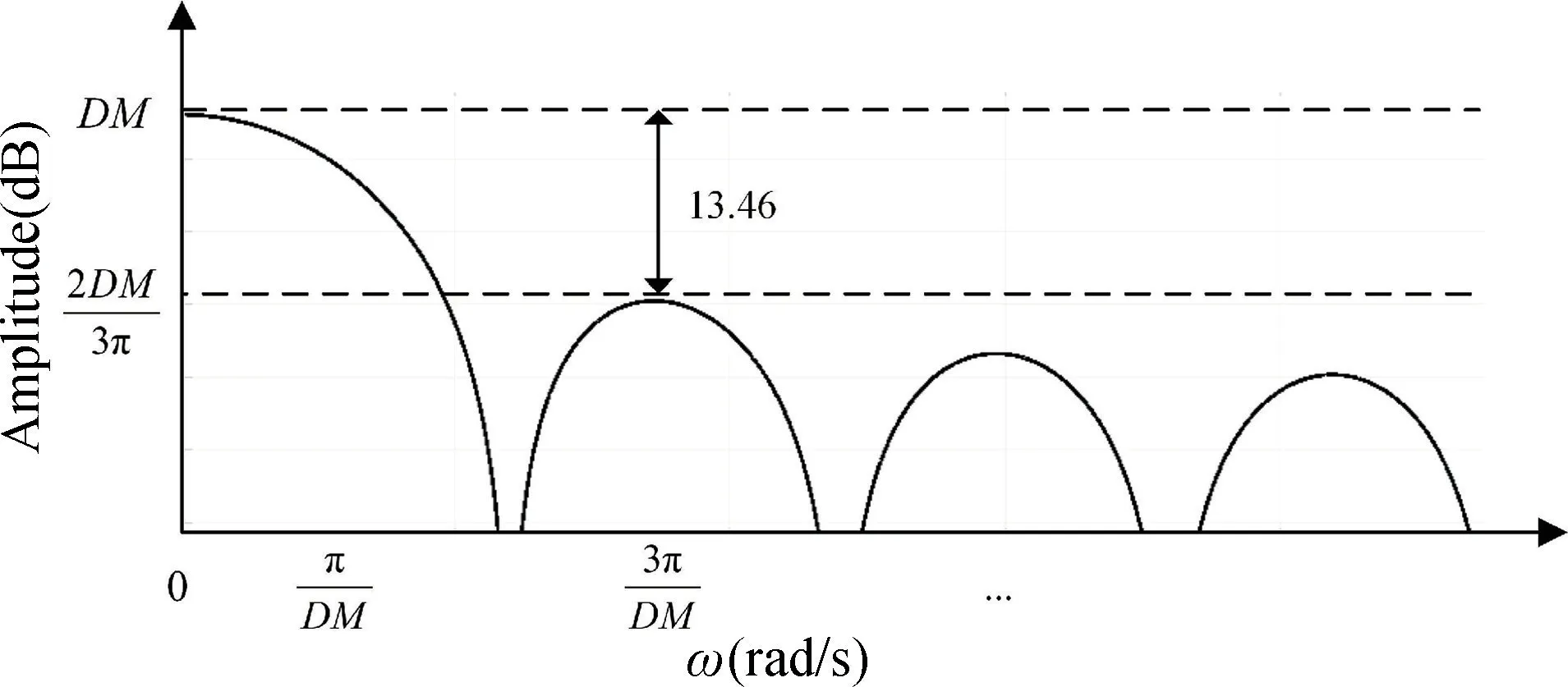

式中:Sa(x)=為抽樣函數,Sa(0)=1,則CIC 濾波器在ω等于0 時幅度值為DM。圖2 展示了單級CIC濾波器的頻率特性。阻帶衰減較嚴重,約為13.46 dB,旁瓣電平較高,容易出現混疊現象。

圖2 幅頻響應特性曲線Fig.2 Amplitude frequency response characteristic curve

1.1.2 多級CIC 濾波器

多級級聯CIC 濾波器可改善單級CIC 濾波器的缺陷,其通過降低旁瓣電平提高阻帶衰減。多級CIC 濾波器的阻帶衰減為[11]:

式中:N為級聯數,伴隨N值增大,阻帶和通帶衰減增加,導致通帶平坦度降低,因此N不宜過大[12]。

1.2 優化設計原理

以降低系統功耗和減小設計面積為目標,本設計提出的濾波器結構可有效改善功耗和面積問題。采用半字節串行算法技術,可有效減小寄存器內部位寬。為適應不同帶寬需求,提供可編程的采樣因子,同時對輸入信號字長進行有效擴展,使采樣因子大小不同時仍可復用同一電路。配置增益校正模塊以減小信號失真,并采用CSD 編碼方式對增益校正模塊中的乘法系數進行編碼,以有效減小乘法器面積。

1.2.1 位寬擴展

當采樣因子D和濾波器階數N過大時,由于積分器模塊不斷進行累加操作,運算數據則需要更大字長的寄存器進行存儲,但內部寄存器位寬是有限的,因此遞歸型級聯CIC 濾波器的輸出數據產生溢出,導致輸出信號嚴重失真。若數據流采用二進制補碼形式,并且累加器和寄存器的位寬足夠大時,則濾波器能正確輸出信號。

寄存器最大位寬由直流增益決定[13],當頻率趨近于0 時,增益G如式(4)所示:

為了避免溢出,寄存器的實際位寬應依據式(5)計算得出[14]:

式中:Bmax為CIC 濾波器各級存儲器最大有效字長;Bin為輸入位寬;Nlog2(DM)取值遵循向上取整規則。為了便于采用多路復用技術以減少資源開銷,D的取值設置為采樣因子可調范圍內的最大值。

1.2.2 半字節串行算法

采用半字節串行算法[15]可將輸入信號從最低有效位MSB 至最高有效位LSB 依次拆分為多位字長相同的信號輸出,輸出數據串行交叉或者多路復用在高速通道中。為有效優化內部寄存器位寬并節省邏輯單元數,利用該算法將輸入的每個數字中頻信號從LSB 至MSB 拆分為4 個位寬一致的信號,依次從低位到高位串行輸出。

1.2.3 可編程因子

在數字上/下變頻系統中,為實現帶寬可變功能,CIC 濾波器的采樣因子應可編程或可配置。數據的下采樣過程即通過跨時鐘域將高頻信號分量輸出為低頻信號分量,上采樣過程則相反。

對于采樣因子固定的CIC 濾波器,為實現抽取運算需要根據相應的采樣因子在連續信號間隔D個周期輸出數據,而實現插值運算則需在每個時鐘周期內插入D-1 個零值。因此,為實現可配置的CIC 濾波器,主時鐘根據可調的采樣因子生成相應的分頻時鐘,對數據進行采樣處理,即可完成相應的抽取和插值功能。

1.2.4 增益校正

積分器中連續的累加運算不可避免產生溢出,導致輸出比特增長,引起濾波器輸入輸出之間的濾波增益升高。為了減小信號失真,同時節約后級大量硬件資源[16],在設計中配置增益校正模塊使末級輸出數據的精度有限。

增益校正模塊分為截位模塊和常系數乘法器。若增益G的表達式(4)中DM的乘積為2 的冪指數的形式,即G=(DM)N=2KN,則直接裁剪輸出數據的低KN位,保留與輸出位寬長度相同的高位部分。當DM的乘積不為2 的冪指數的形式時,若直接將輸出結果乘上增益因子G的倒數,則會造成乘法器位寬和設計面積過大。

為進一步優化設計面積,提高資源利用率,本設計針對傳統增益校正模塊的不足之處進行優化。即當增益值G不為2 的整數次冪時,將增益表達式轉換為如下形式:

式中:X為2 的整數次冪所表示的數,且這個數最接近于DM,則直接對輸出進行右移以實現這部分乘積的增益校正;剩下的乘積部分(DM/X)N,首先對該乘積倒數進行量化,其中量化位寬為A,后采用CSD 編碼方式對量化后的數進行編碼,最終通過移位、加減法運算和截位實現增益校正。綜上,通過將截位后的信號與乘法系數相乘,并舍棄掉低A位乘法運算結果,保留所需高位數據,以此實現增益校正。

1.2.5 CSD 編碼

增益校正模塊中的常系數乘法器需要存儲一定量的配置系數,為減小乘法器面積,使用CSD 編碼方式對乘法器系數進行優化,可降低系數中非0 元素數量。

CSD 編碼方式如下[17]:

從上述CSD 碼的編碼方式總結得出: 任何相鄰的兩位中,必包含1 個0,故CSD 表示法中非0 元素的數量不會超過系數位寬總數的一半。所以利用CSD 編碼表示法對乘法器系數進行編碼,可獲得更多0 位,進而優化乘法器的面積。

2 MATLAB 建模

2.1 總體模型

采用MATLAB Simulink 搭建CIC 濾波器模型,以驗證半字節串行算法的可行性。由于CIC 抽取濾波器和內插濾波器的實現上,只是數據流的方向不同,而方法一致,見本文第1 部分基本原理說明,在此僅對抽取類型的濾波器進行詳細設計。

經對音頻領域應用需求進行分析,需要設計一個能夠實現2~16 倍抽取頻變因子、通帶帶寬為15 kHz~4 MHz、阻帶衰減大于50 dB 且輸入/輸出位寬為22 比特的抽取濾波器,綜合考慮確定該CIC 濾波器的級聯參數N和延遲因子M分別取值為4 和1。基于本文提出的CIC 實現結構,設計了一款通用的CIC 抽取濾波器。

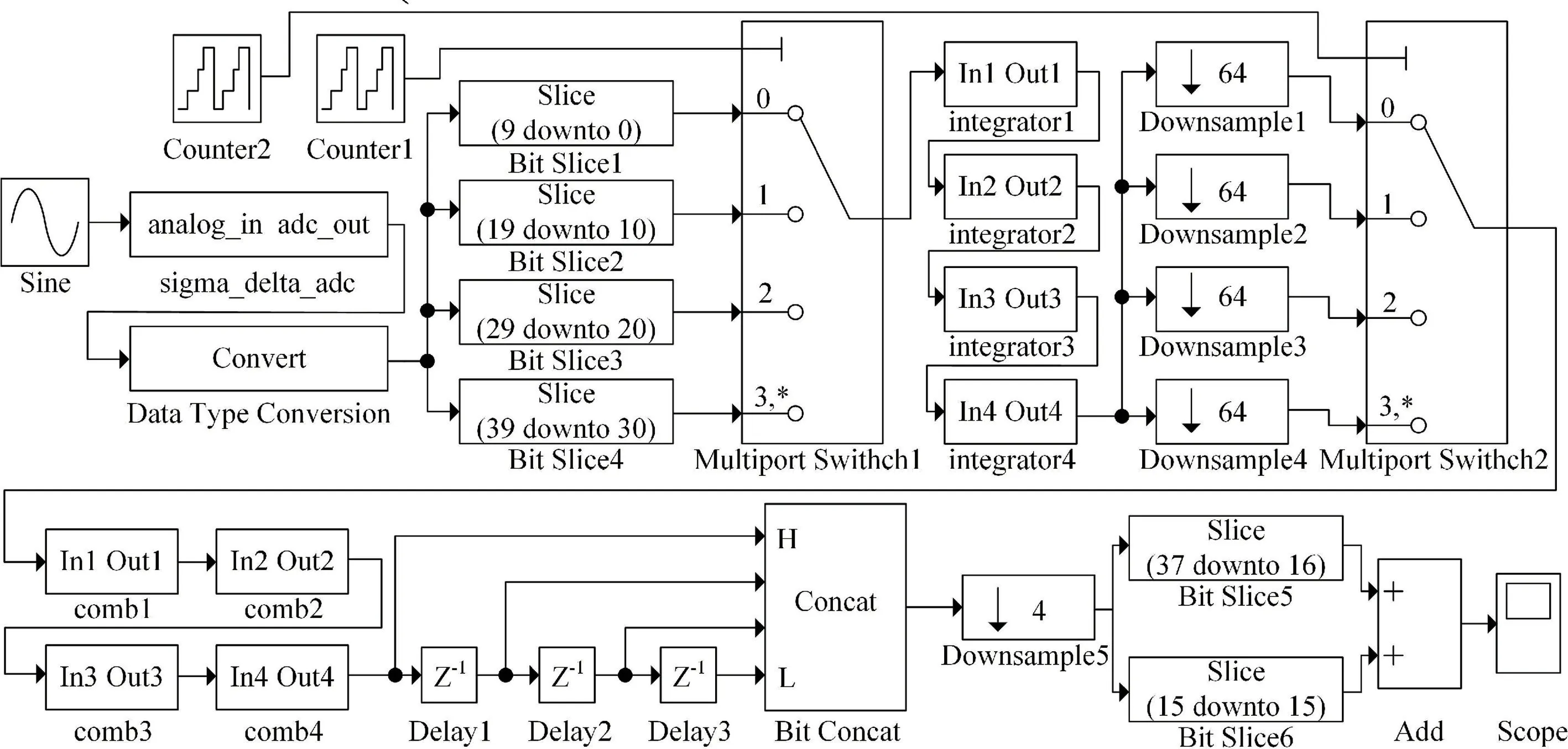

CIC 抽取濾波器整體模型如圖3 所示。采用轉換器Conversion 將輸入信號有效位寬拓展至40 比特,后利用片選器Bit Slice 將輸入數據依次從MSB 至LSB切分為4 組10 比特數據串行輸出。四級級聯積分器做累加運算,抽取器對末級積分器輸出數據進行降采樣處理,每間隔64 個時鐘周期,利用(4 個步長分別相差1)Downsample 模塊進行一次下采樣,多路選擇器Multiport Switch 將4 路并行采樣結果轉化為1 路串行數據輸出。梳狀濾波器comb 模塊對數據進行濾波處理,并將濾波后的數據分為4 路并行數據(分別相差一個時鐘周期)同時傳輸給Bit Concat 模塊,該模塊將數據從MSB 至LSB 拼接為位寬40 比特的數據傳輸給片選器,對數據做截位處理,最終實現CIC 抽取濾波器降采樣和濾波功能。

圖3 CIC 抽取濾波器模型Fig.3 The model of CIC decimation filter

2.2 功能驗證

基于半字節串行算法的CIC 抽取濾波器仿真波形如圖4 所示,正確實現16 倍下采樣功能,輸出所需低頻分量。

圖4 D=16 時的仿真波形。(a) 輸入波形;(b) 輸出波形Fig.4 Simulation waveform when D=16.(a) The waveform of input;(b)The waveform of output

輸出信號頻譜如圖5 所示,CIC 抽取濾波器濾除高頻信號,留下低頻信號。結果表明搭建的模型功能正確,完成了降采樣和濾除高頻噪聲的功能。

圖5 輸出信號頻譜Fig.5 The spectrogram of output signal

3 ASIC 電路設計

3.1 系統設計

根據MATLAB 建模設計原理進行ASIC 電路設計,本設計的整體架構包括信道帶寬配置模塊、時鐘控制模塊和CIC 抽取濾波器實現模塊,如圖6 所示。時鐘控制模塊通過信道帶寬配置模塊提供的下采樣因子D產生各模塊所需的低頻時鐘或使能信號。CIC 抽取濾波器編碼模塊將輸入數據一分為四串行輸出給積分器做累加處理,抽取器對累加處理后的數據進行D倍下采樣后傳輸給梳狀濾波器完成濾波處理,由位拼接模塊將拆分后的數據重新組合為完整數據,最后經由增益校正模塊調整輸出精度。

圖6 總體結構框圖Fig.6 The block diagram of overall structure

3.2 編碼模塊設計

首先,為保證精度以及避免數據溢出,根據位寬擴展公式(5)確定最大擴展位寬為40 比特,拓寬的有效位由輸入數據的最高有效位填補。隨后基于半字節算法原理,將拓展位寬后的信號依次從MSB 至LSB 切分為4個位寬10 比特的數據從低位至高位串行輸出。

3.3 積分器和梳狀濾波器設計

積分器主要由加法器和寄存器構成,在不影響輸入流的情況下,每4 個串行數據累加完成后開始新一輪累加。其狀態方程為:

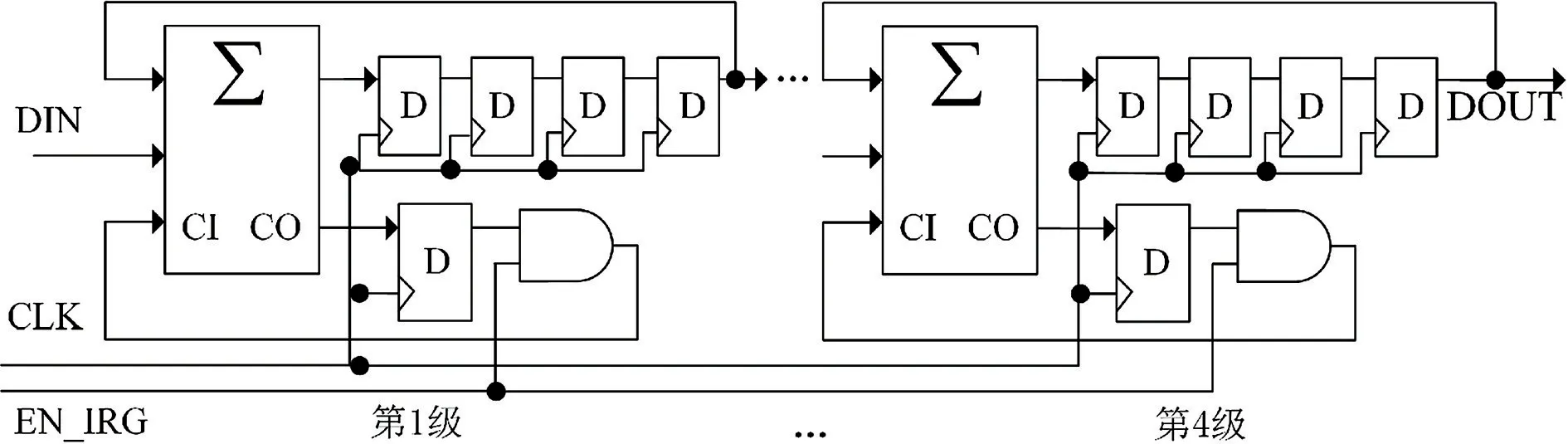

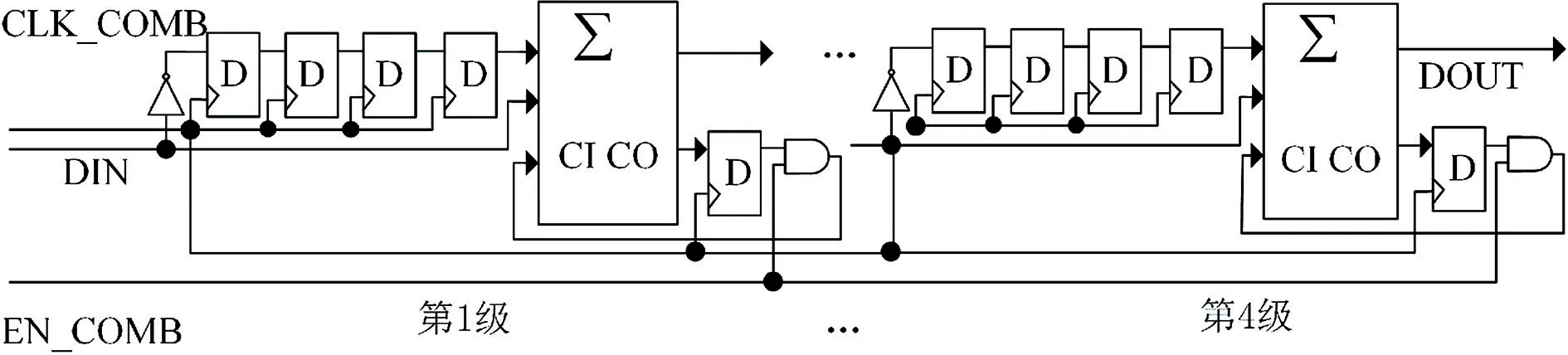

積分器結構如圖7 所示,積分器輸入數據為編碼數據,有效位相加產生進位,產生的進位信號存儲在寄存器中,并延時一個時鐘周期后向高位進位。4 個串行數據完成累加后,相當于40 比特數據運算完成,故最后一次累加產生的進位信號不參與下一次累加運算。

圖7 積分器結構Fig.7 The structure of integrator

梳狀濾波器同樣主要由加法器和寄存器構成,每4 個串行數據加法運算完成之后加法器清零。其狀態方程為:

梳狀濾波器結構如圖8 所示,采用數據直接取反的方式將減法運算轉化為加法運算,簡化了運算器的電路結構。

圖8 梳狀濾波器結構Fig.8 The structure of comb filter

3.4 抽取器和增益校正模塊設計

3.4.1 抽取器設計

抽取器將級聯積分器末級輸出的4 路數據x(n)、x(n-1)、x(n-2)和x(n-3)分別進行D倍下采樣,并對4 路采樣數據進行串并轉換以獲得1 路輸出數據。

3.4.2 增益校正模塊設計

當增益值G為2 的整數次冪時,采用右移運算完成增益校正。反之則根據式(6)先對輸出信號完成相應的截位運算,后對上述運算的結果進行右移運算和加/減法運算,以便實現乘以相應系數的功能。此外,利用CSD 編碼乘法系數替代全位寬二進制補碼編碼乘法系數。其中乘法系數被量化為16 位有符號數。最終,依據0 舍1 入的進位法則,舍棄乘法運算結果的低16 位,同時為滿足輸出信號位寬要求,保留所需高位數據。

4 驗證與綜合

4.1 仿真驗證

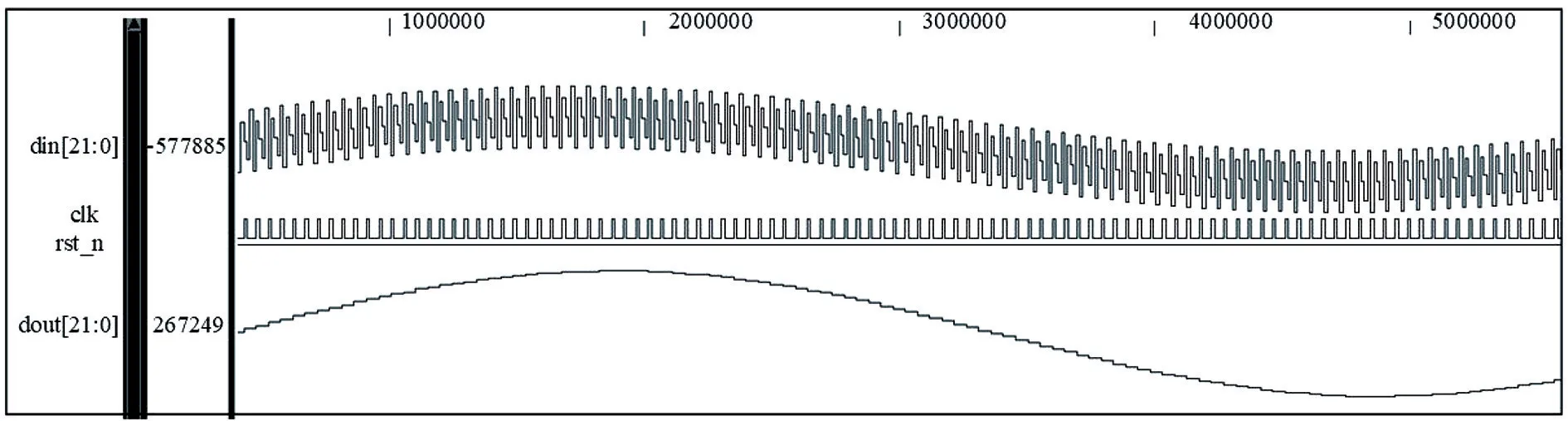

基于Verilog HDL 語言,采用自頂向下的層次化設計思路,完成采樣因子為2~16 倍的CIC 濾波器的RTL 級描述,并搭建VCS 仿真器環境進行功能驗證。

其中,輸入信號為50 MHz 和1 MHz 的正弦波混合信號數據,以抽取率D=2 為例,輸出仿真波形如圖9 所示,結果表明所設計的CIC 抽取濾波器功能正確,不僅濾除了50 MHz 高頻噪聲分量,還實現了2 倍抽取功能。

圖9 輸出仿真波形Fig.9 The simulation waveform of output

4.2 DC 綜合

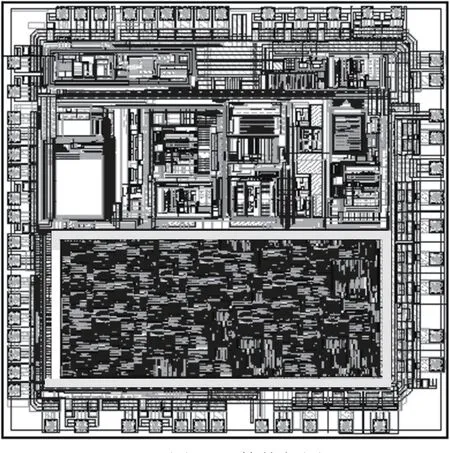

采用Synopsys 公司的Design Compile 綜合工具,基于65 nm COMS 標準單元工藝庫對ASIC 電路進行綜合,得到相應的門級網表,如圖10 所示。

圖10 CIC 濾波器DC 綜合網表Fig.10 The DC synthesis netlist of CIC filter

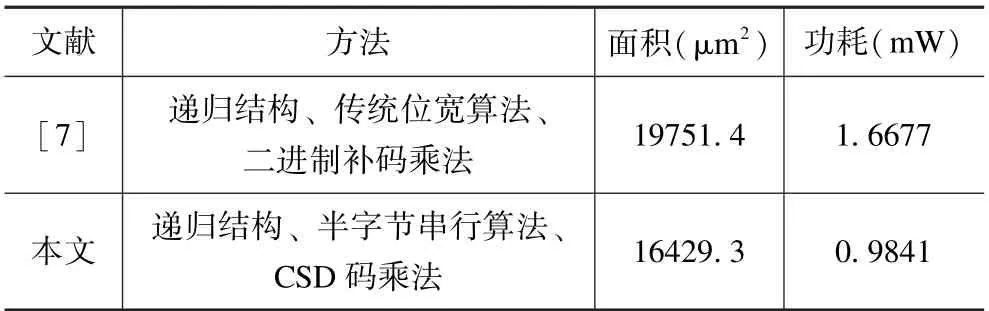

抽取倍數靈活的CIC 濾波器大多采用遞歸型結構。王堯等[7]實現具有16,32,64 和128 倍抽取功能的CIC 濾波器,由于內部寄存器位寬過大,使得功耗和面積過高。為對比上述設計思路,采用結合傳統算法和二進制補碼乘法[7]以及結合半字節串行算法和CSD 碼乘法(本文)兩種方法分別設計能夠實現2~16倍抽取功能的CIC 抽取濾波器,并進行DC 綜合。本文提出的結構和傳統結構所設計的濾波器性能參數對比如表1 所示。結果表明,本文設計的濾波器在功耗和面積方面具有優勢,特別是在抽取倍數和數據位寬過大時,這種優勢將會表現得更加明顯。

表1 性能參數對比Tab.1 Comparison of performance parameters

5 濾波器實現與仿真分析

5.1 布局布線

布局布線(Placement and Routing)就是將前端邏輯綜合產生的門級網表、約束文件和庫文件等通過電子設計自動化(Innovus)軟件轉換為版圖,圖11 為CIC濾波器設計版圖。

圖11 CIC 抽取濾波器的設計版圖Fig.11 The layout of CIC decimation filter

5.2 門級仿真

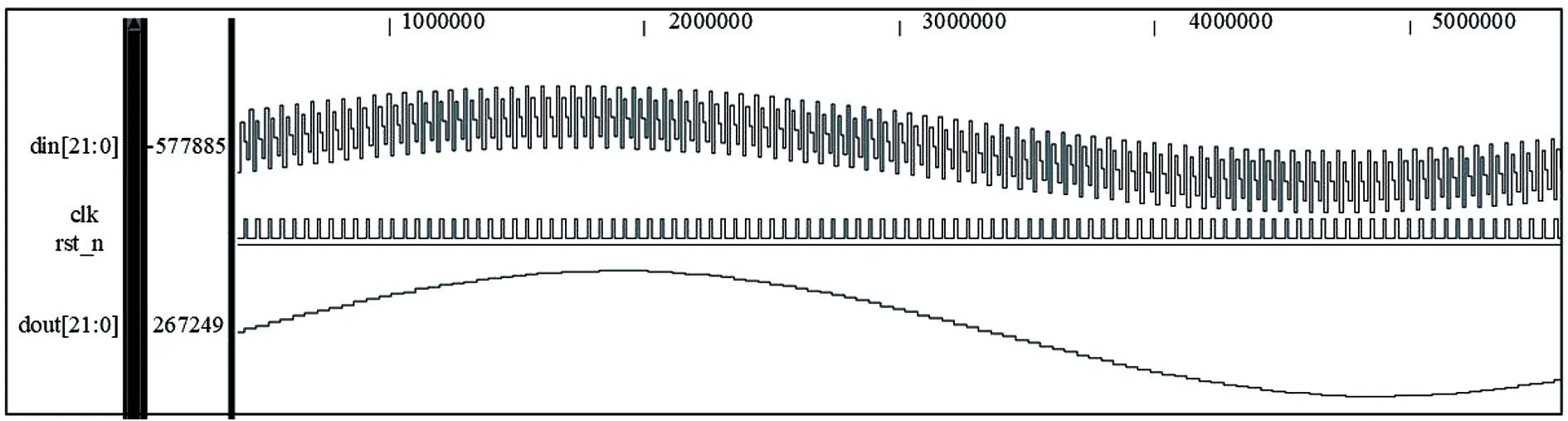

為模擬實際電路的運行效果,需要將版圖設計產生的延時信息、寄生電容和電阻添加到后仿真中,即門級仿真。

如圖12 所示,展示了抽取倍數為4 的門級仿真波形。結果表明,本設計正確地實現4 倍下采樣和濾波功能,同時滿足時序和信號完整性要求。

圖12 CIC 抽取濾波器門級仿真波形Fig.12 The gate-level simulation waveform of CIC decimation filter

5.3 工程應用

基于本設計方案,設計級聯數N=4,延遲因子M=1,抽取因子D為2~16 倍的CIC 濾波器。此外,CIC 濾波器級聯3 級半帶濾波器,綜上可實現抽取因子為16~128 范圍內的數字濾波器,其ASIC 電路已應用于某數字接收機工程設計中。基于65 nm CMOS 工藝對本文的CIC 抽取濾波器進行版圖設計,如圖13 所示,白色框內的即為數字電路版圖。

圖13 數字電路整體版圖Fig.13 The overall layout of digital circuit

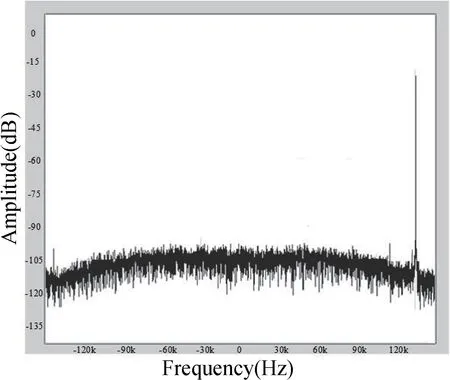

經測試,輸入信號頻率為2.385 MHz,經過混頻模塊及數字濾波器下采樣得到頻率為135 kHz 的基帶信號,信號頻譜幅度為85 dB,如圖14 所示。

圖14 數字電路測試結果圖Fig.14 The test result graph of digital circuit

6 結論

本文設計了一種基于半字節串行算法的低功耗可配置級聯CIC 抽取濾波器。為減小功耗,對傳統CIC濾波器結構進行改進和優化。采用半字節串行算法及多路復用技術,減少內部運算和存儲單元使用。提供可編程采樣因子,能夠靈活處理多速率信號,適用于多種信道帶寬并存的通信系統。為進一步降低功耗,采用CSD 編碼替代傳統二進制補碼編碼方式,大幅減少邏輯資源的消耗,最終實現了低功耗可編程的CIC濾波器。