多路精確穩壓輸出的數字DC-DC變換器設計

侯 偉,鄢婉娟,彭 健

(航天東方紅衛星有限公司,北京 100094)

目前航天器上使用的DC-DC 變換器均為傳統模擬電路設計,且很大一部分依賴進口。與模擬技術實現閉環反饋控制的DC-DC 變換器相比,數字電路具有以下優點:1)可實現多路獨立閉環控制、精確穩壓輸出,具有快速響應能力及調節能力;2)可實現硬件拓撲的通用化設計,通過參數設置實現針對不同對象的應用;3)抗干擾能力強,避免了模擬信號的畸變失真;4)控制參數設計精確,一致性好,性能穩定;5)具備高度的柔性、智能化和可操控性,可通過遠程診斷實現故障管理。本文以常用的XX28512 (28 V 輸入,+5 V、±12 V 三路輸出)型DC-DC 為例,設計一款三路(+5 V/3.6 A、+12 V/0.5 A、-12 V/0.5 A)獨立閉環控制、精確穩壓輸出且電壓可通過軟件設置的數字DC-DC 變換器。

1 方案設計

數字化DC-DC 變換器的設計分硬件電路設計和軟件程序設計兩個部分。

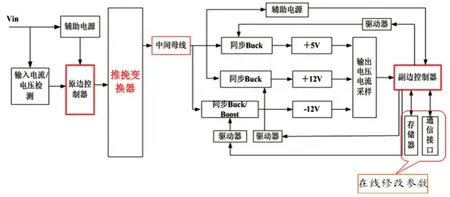

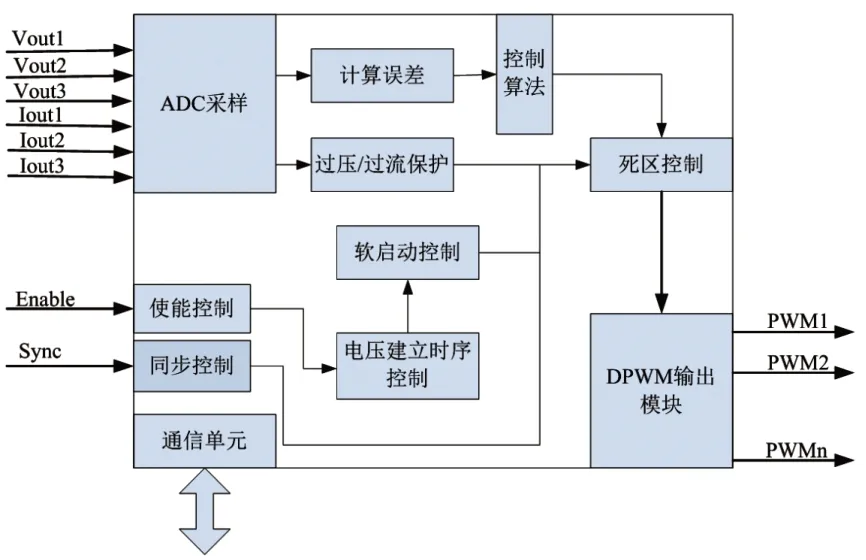

依據多路輸出、每路精確穩壓的要求,數字化DC-DC 變換器的設計必須建立三個獨立的閉環進行穩壓。為了提高輸出電壓的調節速度和避免原、副邊通信帶來的軟、硬件設計的復雜性,數字化DC-DC 變換器的總體框架采用主控制器在變壓器副邊、輔助控制器在原邊的設計方案,三路輸出電壓全部在副邊構成閉環,由主控制器直接進行調節,而不用將電壓信息隔離反饋到原邊。DC-DC 變換器的主拓撲原理框圖如圖1 所示。

圖1 主拓撲原理框圖

數字化DC-DC 變換器的主拓撲采用推挽變換器結構,提高了輸入電壓和變壓器的利用率,而且副邊繞組的整流電路無需濾波電感,電路結構簡單。副邊三路共用一路母線,+5和+12 V 輸出采用同步Buck 變換器實現穩壓,-12 V 采用同步Buck/Boost 變換器實現穩壓。采用同步整流的設計方式不僅可以減小續流二極管的導通損耗,提高轉換效率,而且實現了負載和母線的能量雙向流動,負載變化時每路后級調節的占空比變化較小,減小了對副邊母線電壓的影響和負載不平衡時各路之間的交叉調節[1]。

數字化DC-DC 變換器的原、副邊各有一個控制器,兩個控制器互相隔離。主控制器在副邊,完成副邊三路的穩壓調節、輸出電壓過壓保護、輸出電流過流保護、各路輸出軟啟動、電壓時序控制、使能、同步和通信功能。輔助控制器在原邊,完成原邊互補推挽開關管的控制、輸入電壓欠壓保護、輸入電流過流保護和原邊軟啟動功能。

2 硬件設計

2.1 主拓撲設計

數字化DC-DC 變換器的主拓撲采用推挽變換器結構,如圖2 所示。輸入電壓的設計范圍是23~33 V,經一級LC 濾波后輸入到主變壓器。原邊控制器在軟啟動之后,使兩個開關管分別以0.45 的固定占空比互補導通(死區時間為100 ns),將能量傳遞到副邊繞組中,并經過全波整流、濾波后得到比較穩定的副邊母線電壓。為了避免與副邊三路Buck 的開關頻率(312 kHz)之間產生拍頻干擾,原邊的開關頻率稍高于副邊的開關頻率,定為320 kHz。

圖2 主拓撲原理圖

為了減小開關動作時的導通損耗和關斷損耗,主開關管和副邊母線的整流二極管都加有相應的吸收電路,防止開關溫升過高損耗器件。原、副邊的“地”之間接有一高壓吸收電容,減小地之間的高頻干擾。根據工作頻率以及輸出功率,主變壓器的磁芯選用TDK 公司PC40 材質的磁罐,尺寸選擇P18/11,原、副邊每個繞組的匝數分別為8 匝和6 匝。

2.2 同步Buck(Buck/Boost)變換器設計

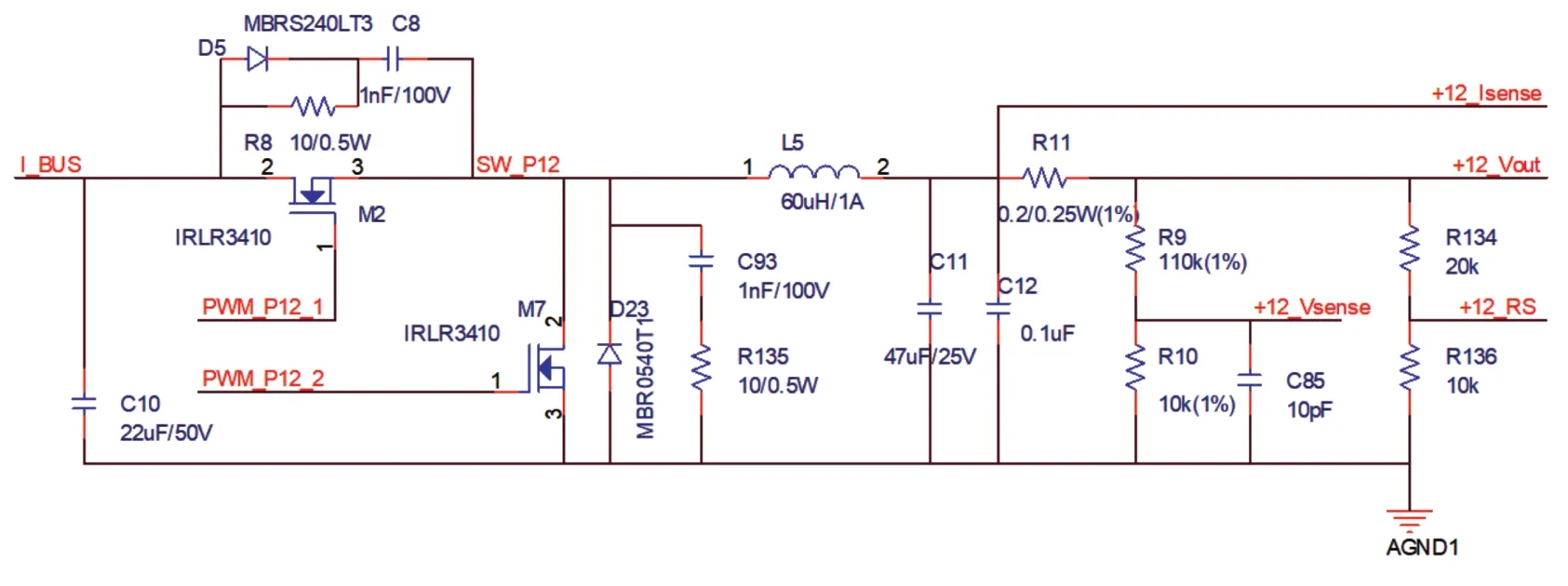

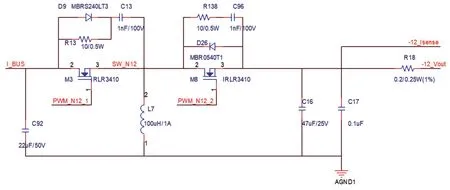

副邊+5 和+12 V 輸出采用同步Buck 的變換器結構,而-12 V 由于輸入、輸出電壓極性相反,采用同步Buck/Boost變換器結構,每路獨立穩壓調節。+5、+12 和-12 V 的電路原理分別如圖3、圖4 和圖5 所示。每路輸出都采用電壓閉環穩壓調節,每路輸出電流采用電阻取樣,因為三路輸出共地,所以取樣電阻放在輸出高端,防止地線中產生干擾,避免各路之間相互影響。正電壓輸出+5 和+12 V 的有遙測端子,遙測電壓為+4 V,遙測分壓電阻的值要盡量大,以減小對輸出電壓和效率的影響,但是必須滿足遙測阻抗的要求。

圖3 +5 V輸出同步Buck原理圖

圖4 +12 V輸出同步Buck原理圖

圖5 -12 V輸出同步Buck/Boost原理圖

同步Buck/Boost 變換器就是將傳統Buck/Boost 變換器中的續流二極管換成MOSFET,因此,與其他兩路不同的是,-12 V 的兩個MOSFET 都需要高邊驅動[2]。由于進行電壓取樣信號放大的運放為正電壓單電源供電,-12 V 的電壓檢測與其他兩路不同,不是分壓后進行取樣,而是采用倍數為1/12的反相放大器實現負電壓取樣。

3 軟件設計

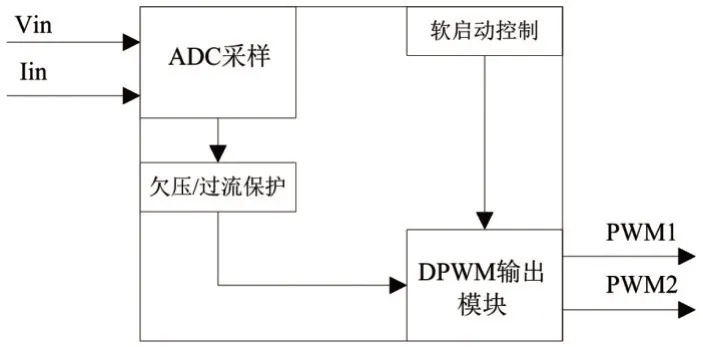

原邊控制器和副邊控制器的總體功能設計框圖如圖6 和圖7 所示[3]。

圖6 原邊控制器功能設計框圖

圖7 副邊控制器功能設計框圖

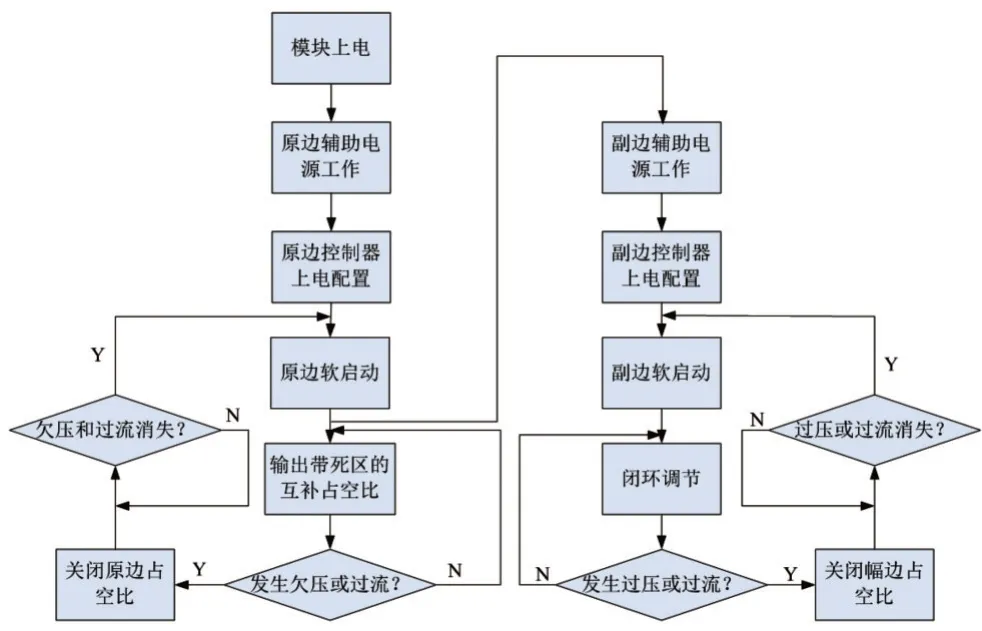

數字DC-DC 變換器工作流程如圖8 所示。在發生過壓、過流等異常情況時,控制器首先關閉控制信號,并且在檢測異常消失延時一段時間后重新軟啟動,且恢復時間可程序設定。數字化控制器的通信協議中采用16 位的CRC 校驗,保證上位機的數據可靠寫入數字化電源模塊中。考慮到特定的應用環境,設計中采用了三模塊冗余(TMR)技術,每個參數在E2PROM 存儲器中有三個備份,以抵抗單粒子翻轉對E2PROM 造成的影響[4-5]。

圖8 數字DC-DC變換器工作流程

4 測試結果

數字DC-DC 變換器實現了三路獨立精確穩壓且輸出電壓在額定值±20%范圍內可設置,同時上電時序、輸出過壓、過流保護值、PID 參數等可設置。頻率同步可通過外接時鐘實現。圖9 給出了參數配置軟件的界面,可以對+5、+12、-12 V 三路的輸出電壓基準、過壓保護值、過流保護值、上電延遲時間、PID 參數等進行獨立設置。

圖9 數字DC-DC變換器參數配置軟件

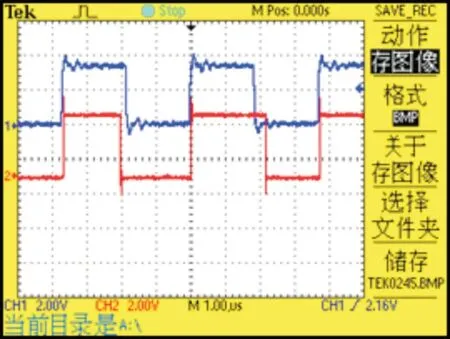

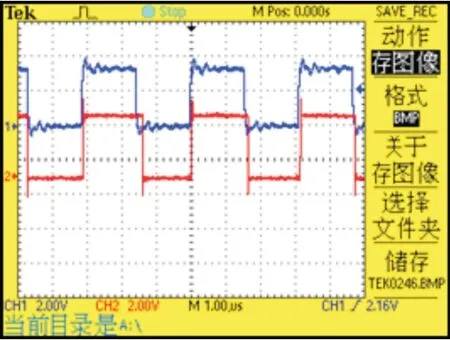

圖10 和圖11 給出了上電延遲時間設置后的啟動時序,圖10 中+5、+12、-12 V 啟動時序分別為0、5、10 ms,圖11 中+5、+12、-12 V 啟動時序分別為0、5、15 ms,三路上電延遲時間在0~100 ms 范圍內可設置,驗證了數字DC-DC 變換器上電時序設置功能。外接時鐘270 kHz 時,數字DC-DC 變換器的開關頻率如圖12 所示,外接時鐘320 kHz 時,數字DC-DC變換器的開關頻率如圖13 所示,驗證了外部時鐘頻率同步功能。

圖12 初始的外部時鐘與PWM波形(藍線:外部時鐘信號;紅線:控制器的PWM信號,同步頻率270 kHz)

圖13 調整參數后的外部時鐘與PWM波形(藍線:外部時鐘信號;紅線:控制器的PWM信號,同步頻率320 kHz)

5 結論

本文完成了一款三路輸出,各路獨立穩壓、輸出精確可調的數字化DC-DC 變換器的設計與驗證,取得了以下主要成果:通過對多路穩壓輸出拓撲結構比較與分析,設計了以推挽變換器為主體、副邊三路后級閉環穩壓控制的拓撲結構,在FPGA 平臺上采用狀態機結構完成控制算法的運算時序與控制邏輯,實現高精度DPWM 模塊,完成了多路信號高速采樣,實現了數字化DC-DC 控制器的核心功能;通過狀態機控制總線的時序邏輯,實現I2C 總線和UART 接口通信的設計,提供了數字化電源參數的存儲方式,并且可遠程修改電源的運行狀態,數據存儲中,采用三個備份的方式對每個數據進行讀寫操作,保證參數的準確性和電源的安全性,實現了數字化控制器的智能化與容錯機制設計。