一種基于GaAs和FO-WLP工藝的異質異構集成PDK

董澤瑞,陳展飛,劉 軍

(杭州電子科技大學浙江省大規模集成電路設計重點實驗室,浙江 杭州 310018)

0 引 言

近年來,隨著對電子系統微型化高密度、多樣化功能、高性能和低成本日益增長的需求,為實現不同工藝、不同材料和不同工廠的協同設計,異質異構集成技術已然成為電子技術重要研究方向之一[1]。

隨著信息技術的高速發展,半導體行業誕生了很多高性能的半導體材料,以GaAs和GaN為代表Ⅲ-Ⅴ族化合物半導體材料具有禁帶寬度較寬、電子遷移率高、高熱導率、低噪聲等顯著特點,表現出更優異的高頻器件性能,滿足集成電路日益增長的性能要求[2]。然而,由于單一半導體材料具有一定的局限性,難以滿足高信息化裝備的需求。異質異構集成技術可將基于GaAs、GaN等化合物材料的高性能有源器件、高性能無源器件、硅基電路模塊與樹脂基電路模塊等,集成為一個完整的異質異構集成電路,充分發揮各種材料、結構以及器件的優勢。本文采用一種異質異構集成技術,扇出型晶圓級封裝(Fan-out Wafer Level Packaging,FO-WLP),其在封裝體積、產品性能、封裝成本和封裝效率上都具有明顯優勢,并且可以將不同功能的芯片集成在一起,顯著提高產品性能[3]。

為了支持不同工藝的電路協同設計,提高異質異構集成電路設計效率,避免不必要的重復流片,設計人員非常需要通用并且準確的異質異構集成工藝設計套件(Process Design Kit,PDK)[4]。PDK是聯系集成電路(Integrated Circuit,IC)設計與晶圓代工廠(Foundry)的重要橋梁[5],其中包含了一系列完整的工藝信息文件、基礎器件庫和器件模型文件,并且可以確保其滿足Foundry的設計規則檢查(Design Rule Check,DRC)、版圖與原理圖的匹配檢查(Layout Versus Schematic,LVS)[6]。

異質異構集成PDK相較于之前傳統工藝PDK更困難復雜,主要表現在異質異構集成的工藝多樣,可開放度不一致,標準工藝定義困難,精確電/磁/熱仿真困難。2016年,為了實現將多種化合物半導體的優勢與CMOS集成電路的優勢結合,實現全新架構的高性能集成芯片,在美國國防部高級研究計劃局(Defense Advanced Research Projects Agency,DARPA)主導的多樣化可用異構集成(Diverse Accessible Heterogeneous Integration,DAHI)項目中,諾斯羅普·格魯曼航天系統公司(Northrop Grumman Aerospace Systems,NGAS)基于統一的設計平臺和分散的工藝平臺,將化合物半導體器件、以及其它新材料和器件與高密度硅基CMOS基板集成,顯著減小了尺寸、重量和功耗,實現顛覆性的高速電子器件[7]。

然而,由于異質異構集成技術的多樣性,目前還沒有提出標準的異質異構集成PDK設計方案,為進一步推進異質異構集成電路設計研究,本文提出一種基于GaAs和FO-WLP工藝的異質異構集成PDK。在本文中,研究了該PDK的開發難點和開發方法,同時該PDK對異質異構集成技術文件、器件模型、Pcell和物理驗證文件進行創新并提供了支持。最后,使用該異質異構集成PDK設計單刀雙擲開關及其封裝電路并進行仿真驗證。

1 異質異構集成PDK開發難點和開發方法

在Advanced Design System(ADS)平臺下開發基于GaAs和FO-WLP工藝的異質異構集成PDK,提供處理多種工藝集成的電路封裝設計流程的完整解決方案,實現工藝數據與設計環境的無縫集成,提高電路封裝設計效率,縮短生產周期[6]。該異質異構集成PDK基本結構框架包含:

Symbols:用于電路原理圖設計的圖形符號,是電路原理圖仿真時器件的載體,用戶通過調用Symbols,對器件進行各項參數的配置。

CDF(Component Description Format)參數:器件的屬性描述文件,用于定義器件名稱、器件參數等各種與器件屬性相關的內容[8]。

Callback函數:器件參數調用關系函數。器件所有參數的設置,包括相關工藝參數限制范圍和器件參數相關聯的計算等都由Callback函數來完成計算并回調。

器件模型(Device Model):器件的仿真模型文件。

Artwork:參數化單元Pcell對應的版圖文件,用于版圖設計。

參數化單元(Pcell,Parameterized Cell):由ADS的AEL語言編寫實現,是EDA仿真工具中的設計單元器件,由上述Symbol、CDF參數、Callbak函數和Artwork組成。

技術文件(Technology File):用于版圖設計和物理驗證的工藝文件,包括圖層的屬性定義、圖層顯示顏色定義、襯底信息等。

物理驗證文件(PV Rule):包含設計規則檢查文件(Design Rule Check,DRC)、版圖與原理圖比較文件(Layout Versus Schematic,LVS)等。

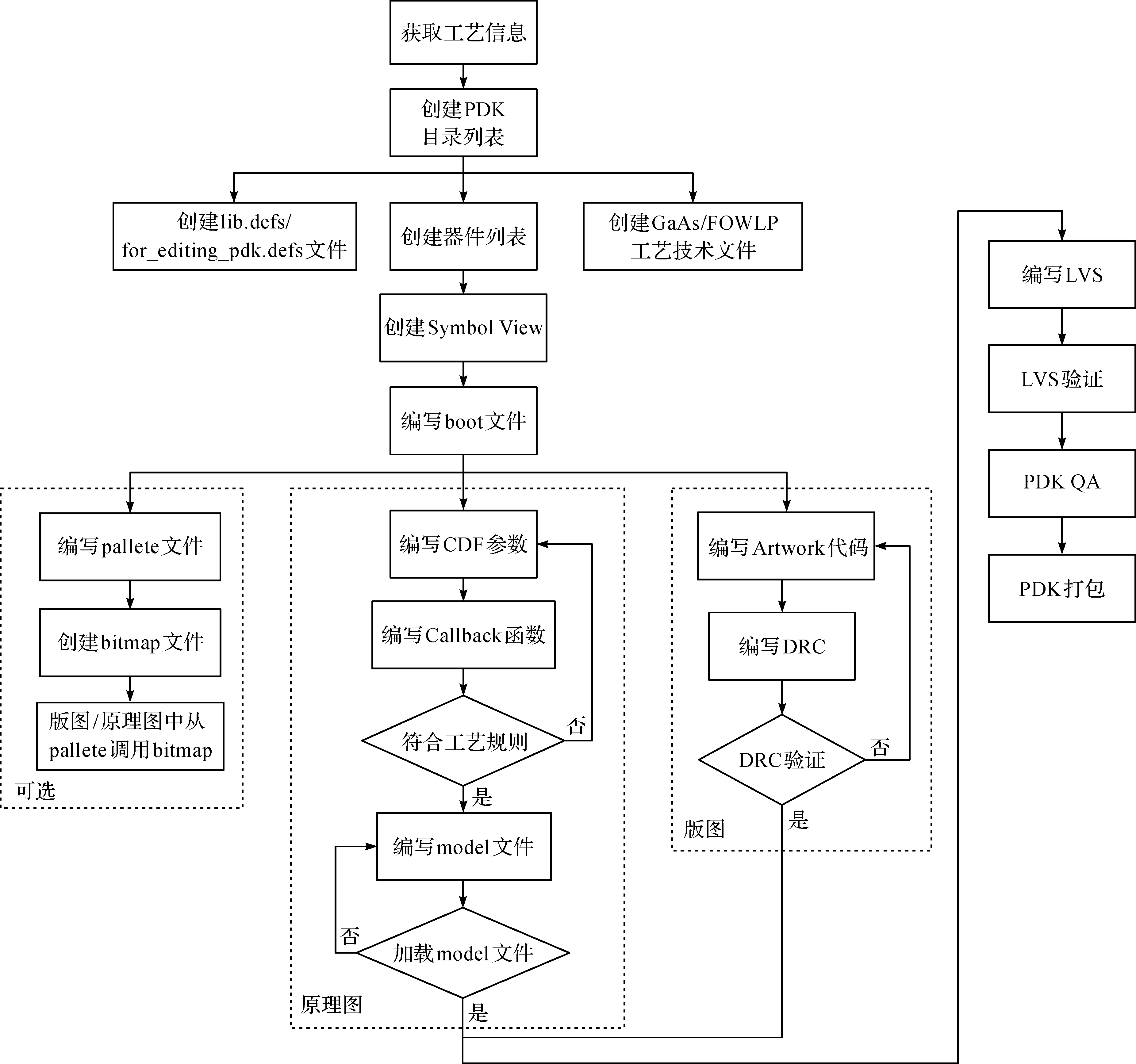

PDK結構框架如圖1所示:

由于預算管理的根本目的是使企業能夠適應市場發展的需要和市場的變化,加強企業對長期發展戰略的確定和實施。通過科學有效的企業預算管理,企業可以在激烈的市場競爭環境下調整自己的行為,并隨著市場的變化不斷做出有效改變,充分適應市場環境。這要求企業在發展市場環境和企業長遠目標的基礎上進行預算管理。在具體工作中,首先要以企業自身的發展戰略為根本目標,預測不同形勢下的市場變化因素,制定相應的經營機制,使企業適應各種變化的市場條件。最后,根據市場變化下企業的實際情況,不斷調整,與市場經濟同步發展。

圖1 PDK結構框架圖

異質異構集成PDK的開發難點在于多工藝之間的行交互,例如不同工藝的堆疊、圖層、電氣和電磁模型交互[9]。不同工藝之間的交互,主要體現在技術文件、Pcell和物理驗證文件,需要在一個PDK中同時調用不同工藝的技術文件,并且確保PDK集成多個技術文件不報錯。在此基礎上設計同時集成兩種工藝的器件,主要包含CDF參數、Artwork和器件模型,并執行滿足多工藝的物理驗證文件無誤。

為實現異質異構集成PDK的多工藝集成交互,本文提出了一種結構化的開發方法開發異構集成PDK,這種方法思路清晰、PDK運行速度快、方便迭代維護。通過此方法,技術文件可以降低出錯率,Pcell和物理驗證文件代碼行數顯著減少,準確性明顯提升,并提供了更高的性能。異質異構集成PDK的整體開發流程如圖2所示。

圖2 異質異構集成PDK整體開發流程圖

2 異質異構集成PDK技術創新

異質異構集成PDK構建在GaAs工藝和FO-WLP工藝信息基礎之上[10],支持從電路設計到物理設計驗證的整個設計流程。此外,該PDK對異質異構集成技術文件、器件模型、Pcell和物理驗證文件進行了創新并提供支持。

2.1 異質異構集成PDK技術文件

異質異構集成PDK技術文件開發的主要難點,在于導入不同工藝時圖層編號產生重復沖突和復合工藝襯底文件的開發。

異質異構集成PDK技術文件開發分為兩個部分,分別為GaAs工藝技術文件和FO-WLP工藝技術文件,開發方法和傳統PDK技術文件類似。異質異構集成PDK技術文件開發特別要注意圖層信息不能重復,如有問題需要及時和Foundry進行溝通。然后,將開發完成的GaAs和FO-WLP技術文件有效地組合為異質異構集成PDK技術文件。

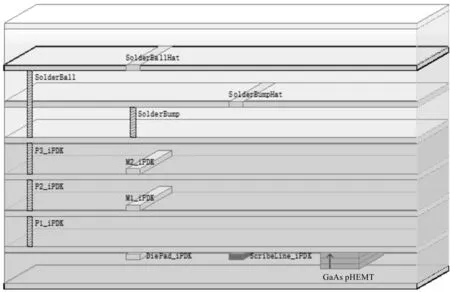

為支持多工藝復合襯底協同EM仿真,在異質異構集成PDK中搭建GaAs和FO-WLP工藝的襯底模型,襯底材料參數由工藝對應的Foundry提供。在FO-WLP工藝襯底上嵌入“Nested Substrate”,添加需要進行聯合仿真的GaAs工藝襯底信息,搭建多工藝復合襯底模型,如圖3所示。

圖3 基于FO-WLP和GaAs復合工藝襯底模型

2.2 異質異構集成pHEMT Pcell

異質異構集成PDK庫由許多器件的Pcell構成,每個Pcell由Symbol、CDF參數、Callback函數和Artwork等組成[11],Pcell實際上是一串使用AEL語言編寫的代碼。如果在ADS版圖編輯器中實例化了Pcell的Arwork,設計者就可以修改器件的參數進行電路性能的調整。然而,必須在器件特性允許的參數范圍內進行修改,任何小于或大于限制條件的值都將返回到最小或最大限值,并且CDF參數及其Callback函數應在器件的原理圖和版圖中保持一致。

為了便于后續系統級設計,在GaAs pHEMT Pcell基礎上開發一個CDF參數,HIExtType(Yes/No),控制pHEMT器件的Artwork是否啟用FO-WLP,其Artwork在GaAs pHEMT基礎上,由源漏柵端口引出PAD搭建GaAs芯片,對GaAs芯片進行模塑,通過3層RDL連接GaAs芯片PAD與樹脂基PAD,實現GaAs pHEMT器件的樹脂基FO-WLP。構建完成的異質異構集成pHEMT器件,允許設計人員從pallete直接拖放器件到原理圖和版圖上進行仿真設計。圖4(a)顯示了異質異構集成pHEMT器件的Symbol,源極、漏極和柵極端口及其FOWLP封裝在器件Symbol中有標記。圖4(b)顯示了相同異質異構集成pHEMT器件HIExtType參數為Yes的Artwork。

圖4 異質異構集成pHEMT Symbol和Artwork

2.3 異質異構集成pHEMT器件模型

在異質異構集成實際電路應用中,pHEMT器件同樣承擔著放大信號、信號混頻、開關電路等作用,因此要求pHEMT器件應當具備高輸出功率,低噪聲,高線性度,工作頻帶寬等電學特性。為提高異質異構集成PDK中pHEMT器件特性在多工藝襯底影響下的準確性,研究了一種基于GaAs和樹脂基FO-WLP異質異構集成的pHEMT器件模型。

該異質異構集成pHEMT器件結構上類似于樹脂基GaAs pHEMT器件。pHEMT器件的建模,是等效電路模型對器件電熱等物理行為的模擬,其在樹脂基上表現出不同的RF特性,與襯底的寄生效應有關。在對大信號模型準確建模之前,考慮樹脂基襯底寄生效應的影響,對小信號進行建模。異質異構集成pHEMT器件小信號模型的寄生元件分布與器件的物理結構模型緊密相關聯,物理結構模型如下圖5所示。

圖5 異質異構集成pHEMT器件的物理結構模型

異質異構集成pHEMT的大信號模型基于改良的ASM模型開發,ASM是由印度理工學院Khandelwal等人提出的一種物理基模型,用于GaAs,GaN pHEMT器件的精確建模。ASM的核心是量子阱表面勢計算,通過表面勢推導可以得到全部工作區域內連續、可導的I-V和C-V特性等。模型中所有的參數提取出來之后,將參數值輸入ASM模型對應值內得到異質異構集成Model文件。將其集成到異質異構集成PDK,即可進行直流特性與大信號的仿真模擬。

2.4 異質異構集成PDK DRC

設計規則為給定工藝技術的物理設計及其版圖連接設置了限制,在電路設計流程中,對于檢查錯誤、降低設計成本和減少設計失敗風險具有重要作用。異質異構集成PDK不僅需要同時引入GaA和FO-WLP兩種工藝設計規則,并且需要制定關聯兩種工藝的新規則,以確保兩種工藝異構集成的版圖設計符合工藝要求。該PDK制定了GaAs工藝頂部金屬層GaAs M2和FO-WLP工藝底部金屬連接層FOWLP P1的連接關系等設計規則,GaAs M2和FOWLP P1的三維結構連接圖如圖6所示。GaAs M2和FOWLP P1的連接規則是一種跨越不同工藝的enclosure設計規則,圖形示意圖如圖7所示。

圖6 GaAs M2和FOWLP P1的三維結構連接圖

圖7 GaAs M2和FOWLP P1的enclosure設計規則圖形示意圖

GaAs M2和FOWLP P1的enclosure DRC開發難點在于,需要同時調用兩種不同工藝的圖層進行DRC檢查。在開發Pcell的過程中GaAs pHEMT和FOWLP的工藝圖層信息已經重新在boot文件中完成定義,同時涉及兩種工藝DRC的工藝圖層運算需要在boot中進行,以確保3D HI PDK的DRC跨越不同工藝可以正常進行檢查。

2.5 異質異構集成PDK LVS

LVS確保了集成電路版圖設計和電路原理圖設計相匹配,盡管有效的DRC驗證檢查確保了版圖設計符合特定的工藝規則,但是不能保證版圖信息、器件連接與實際設計電路完全一致,這就需要LVS對版圖和原理圖的器件類型、器件參數、連接情況進行驗證,以確保制造出來預期的電路。異質異構集成PDK LVS開發與傳統PDK類似。

器件識別是LVS和寄生提取中的一個關鍵步驟,用于識別版圖中的器件及其連接端口。由于pHEMT的柵極使用肖特基接觸,源極和漏極使用歐姆接觸,并且端口不能互換,因此我們通過圖層定義和運算來識別器件并區分端口。pHEMT耗盡型器件ADS LVS的代碼片段如圖8所示,通過代碼識別版圖中的器件識別層及其三個端口,并可以在網表中導出。異質異構集成PDK LVS還有一個關鍵步驟為連接關系定義,需要對不同工藝芯片/結構界面進行定義,構建其連接關系,以檢查版圖中跨越不同工藝的連接是否存在問題。

圖8 pHEMT耗盡型器件ADS LVS代碼片段

3 異質異構集成PDK應用驗證

本章節介紹基于GaAs和FO-WLP工藝的異質異構集成PDK的應用驗證,以確保PDK的準確性和有效性。使用該異質異構集成PDK中GaAs工藝庫,電路設計人員可以使用傳統的MMIC設計工作流程來構建和仿真電路,并且可以構建與版圖相關聯的原理圖執行電氣仿真。在原理圖仿真之后,設計人員可以使用原理圖和EM聯合仿真來得到更準確的仿真結果。采用異質異構集成PDK設計微波段單刀雙擲開關及其FO-WLP電路[12],仿真結果與封裝前的設計結果對比,以驗證PDK的有效性和準確性。圖9顯示了微波頻段單刀雙擲開關的封裝電路。圖10顯示了微波頻段單刀雙擲開關的封裝電路3D結構圖。

圖9 開關扇出型封裝電路圖

在通過DRC和LVS驗證之后,得到電路封裝前后仿真的S參數結果如圖11所示。通過對比分析,開關電路封裝后的回波損耗S11、S22雖然都小于-13 dB,但由于封裝電路中存在電阻、電感引起諧振點偏移,回波損耗趨勢和封裝前有所差別。開關電路封裝后的插入損耗S21和隔離度S31、S32基本和封裝前設計結果相吻合。結果證明,本文所設計的異質異構集成PDK具有較高的準確性和可靠性,能滿足異質異構集成電路的設計要求。最后將封裝完成的單刀雙擲開關電路作為IP電路引入異質異構集成PDK,方便后續系統級設計調用。

圖11 封裝前后單刀雙擲開關S參數仿真結果

4 結束語

為進一步推進異質異構集成電路設計研究,本文提出一種基于GaAs和FO-WLP工藝的異質異構集成PDK,經過前期評估測試到后期開發驗證,較完整的解決了一些目前異質異構集成PDK開發的技術問題,并驗證了該PDK的準確性和可靠性。隨著異質異構集成PDK的成功設計和實現,電路研究人員能夠從復雜和困難的工作中解脫出來,設計將更加高效。我們相信這個異質異構集成PDK的設計將為電路研究人員提供條件開發創新電路,并為推進異質異構集成電路設計研究發揮重要作用。