一種基于MATLAB及FPGA的FIR低通濾波器的設計與實現

阿依夏木·力提甫,趙惠昌,王丹琦

(1.新疆師范大學 物理與電子工程學院,新疆 烏魯木齊 830054;2.南京理工大學 電光學院,江蘇 南京 210094)

隨著信息技術的發展,數字電路的設計逐步擺脫傳統的設計模式,越來越多的數字信號處理系統開始使用可編程門陣列和硬件描述語言實現。現場可編程門陣列(FPGA)是一種可以重復改變組態的電路,特別適合產品發展時需要不斷變更設計的應用,有效節省產品上市的時間。FPGA的修正不需要變更硬體,僅僅需要更改軟體即可。這大大節省研發的成本,而且僅需要下載新的程式碼便可以達到產品上市后的升級功能。 現在FPGA技術已經成為多種數字信號處理應用的強有力的工具。與通用DSP相比,FPGA器件能夠以高速,實時,低成本,高靈活性的優點應用于數字信號處理領域,利用FPGA實現數字信號處理成為數字信號處理領域的一種新的趨勢,它可以完全取代通用DSP芯片或作為通用DSP芯片的協處理器進行工作。低通濾波器的設計方面國內外提出了不少理論方案,但是具體實現過程很少有提及。本文靈活使用MATLAB語言和QuartusII軟件設計出了一種高效低通濾波器,填充了低通濾波器從理論到實際設計過程的一片空白。

1 濾波器的MATLAB設計

數字濾波技術作為數字信號處理的基本分支之一,就是提取信號的有用分量,削弱無用分量的技術,被廣泛應用于數據處理,圖像處理、雷達、聲納信號處理、地址石油勘探等很多領域,越來越受到人們的關注。由單位沖擊響應的不同數字濾波器有兩種類型:有限沖擊響應 (Finite Impulse Response,FIR)數字濾波器和無限沖擊響應(Infinite Impulse Response,IIR)數字濾波器。兩種類型濾波器相比而言,對于同樣的濾波器設計指標,雖然FIR濾波器成本較高,信號延遲較大并且FIR濾波器沒有現成的計算公式(必須要用計算機輔助設計軟件(如MATLAB)來計算),但是FIR濾波器可以采用FFT算法,運算速度較快;精度高,具有嚴格的線性相位等特點優于IIR數字濾波器已被廣泛應用。下面重點介紹FIR數字濾波器的基礎上,基于MATLAB及FPGA實現一種優化的FIR低通濾波器。

1.1 FIR數字濾波器的設計方案

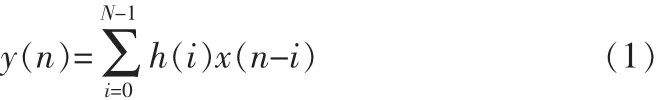

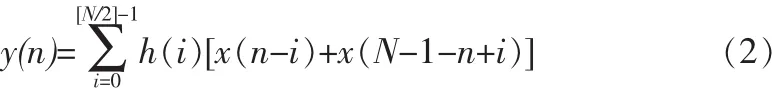

FIR數字濾波器是一個線性時不變系統(LTI),N階因果有限沖激響應濾波器可以用差分方程:

來描述,其中 y(n)是濾波器的輸出信號,x(n)是濾波器的輸入信號,h(n)是濾波器系數。從以上的表達式可以看出來,FIR濾波器是通過加法器,乘法器和移位器組合而實現的。加法器和乘法器的數量,速度和效率等特性對于濾波器的性能非常重要。

在很多應用場合,濾波器都是線性時不變濾波器,也就是帶有常系數的濾波器。具有線性相位的FIR濾波器的系數具有中心對稱特性,即 h(i)=±h(N-1-i)。 則其輸出表達式(1)可以編寫成如下形式:

由此可見,利用它的對稱形式比直接實現少用了一倍的乘法器,大大節省了硬件資源,而且可以提高速度[1]。

1.2 參數提取

設計指標如下:

類型:低通濾波器;Beta 值=0.5;采樣頻率:FS=80 kHz;窗函數:Kaiser窗;截止頻率:FC=10 kHz;階數:15 階;數據寬度:輸入10位,輸出10位。

本次設計選擇了Matlab2009的Toolboxes(數字信號處理工具箱)中的 FDATool(Filter Design & Analysis Tool)工具來設計濾波器,使設計過程更加簡潔,精確[2]。FDATool是一個功能強大的數字濾波分析設計工具,它涵蓋了信號處理工具箱中所有的濾波器設計方法。利用它可以設計出滿足各種性能指標的濾波器,并可查看該濾波器的各種分析圖形。待濾波器設計滿意后,還可以把其系數直接導出為MATLAB變量,文本文件或C語言頭文件等[3]。

打開Matlab軟件主窗口,在Workspace上輸入語句:FDATool,將出現數字信號處理工具窗口,窗口輸入相應的參數以后可以形成符合要求的低通濾波器系數。低通濾波器系數通過在Matlab主窗口上輸入

round(Coefficient*(2^11))命令被放大 2 048 倍后得到如下系數:

Coefficient=[-31 -88 -106 -54 70 239 401 499 499 401 239 70-54-106-88-31]

根據以上濾波器系數設計,可以得到該濾波器模型的差分方程如下:

y(n)=h(0)x(n)+h(1)x(n-1)+h(2)x(n-2)+…,…h(n-1)x(1)+h(n)x(0)=-{-31[x(n)+x(n-15)]+88[x(n-1)+x(n-14)]+106[x(n-2)+x(n-13)]+54[x(n-3)+x(n-12)]}+70[x(n-4)+x(n-11)]+239[x(n-5)+x(n-10)]+401[x(n-6)+x(n-9)]+499[x(n-7)+x(n-8)]

1.3 FIR濾波器的實現原理

根據以上所說的濾波器設計思路,可以將FIR濾波器的原理圖畫出來,如圖1所示。

圖1 FIR濾波器原理框圖Fig.1 Block diagram of the FIR filter

從以上濾波器原理框圖可以看出來,設計的FIR濾波器由16個小BDF文件和一個總體BDF文件組成,小BDF文件分為以下4種模塊:寄存器、加法器、減法器、乘法器。下面結合本設計分別介紹每一個模塊。

2 濾波器的FPGA實現

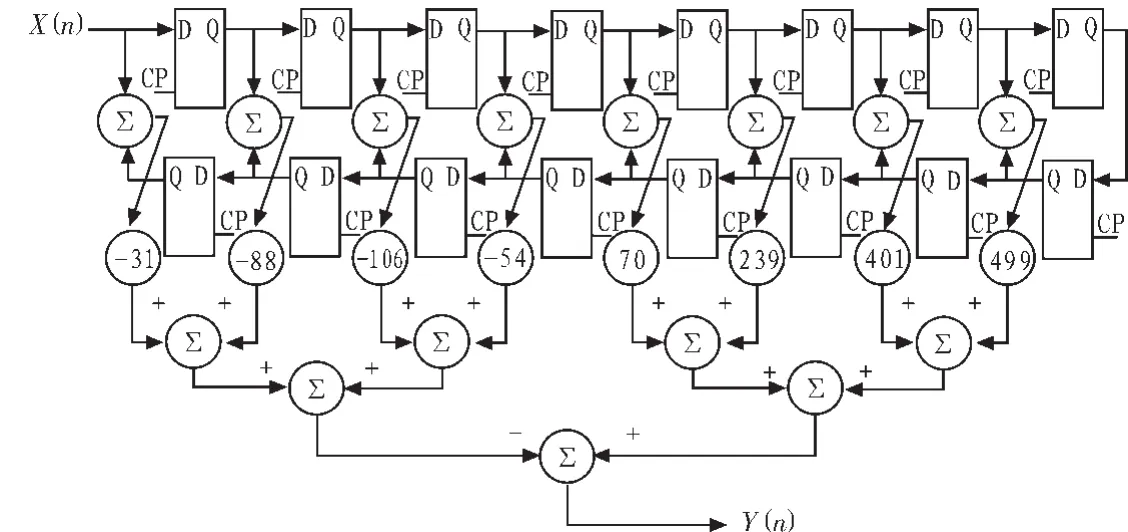

2.1 寄存器模塊的實現

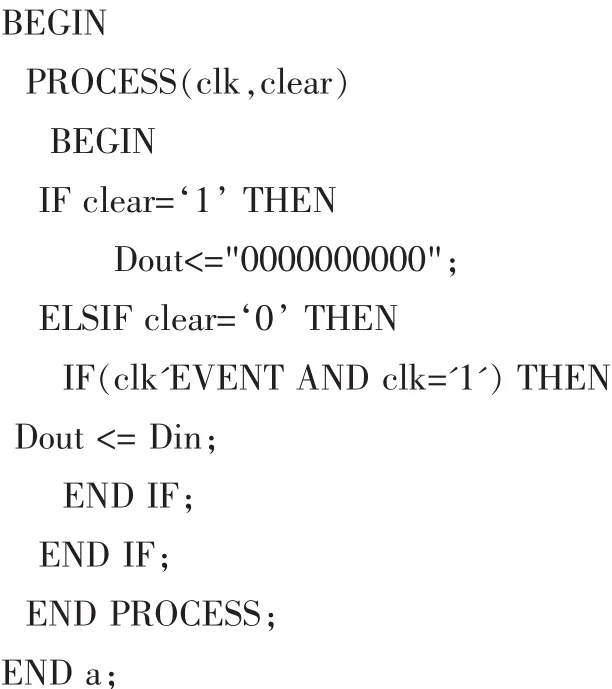

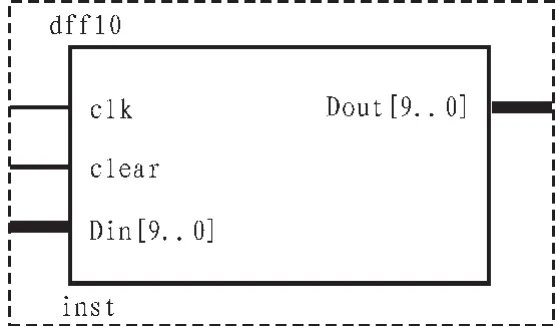

寄存器用于寄存一組二值代碼,對寄存器的觸發器只要求它們具有置1、置0的功能即可,因而本設計中用D觸發器組成寄存器,實現寄存功能。寄存器要求實現的功能為在CP正跳沿前接收輸入信號,正跳沿時觸發翻轉,正跳沿后輸入即被封鎖。本次設計要求輸入數據寬度為10位,總共需要16個十位寄存器。系統生成的寄存器模塊如圖2所示,十位寄存器用VHDL語言描述如下:

圖2 10位寄存器模塊Fig.2 Module of 10 bit register

2.2 乘法器模塊的實現

眾所周知,二進制數在實現乘法或加法時,數值為0的位是不參與運算的。因此,對輸入信號進行編碼時,如果能使0位的數量最多,則完成相應的運算所需要的硬件將會大大減少,運算的速度也會相應地提高很多。正則有符號數字量(Canonic signed digi,t簡稱CSD)正是基于此思想而提出來的一種新型編碼方法,它是具有最少非0元素的表示法[4]。

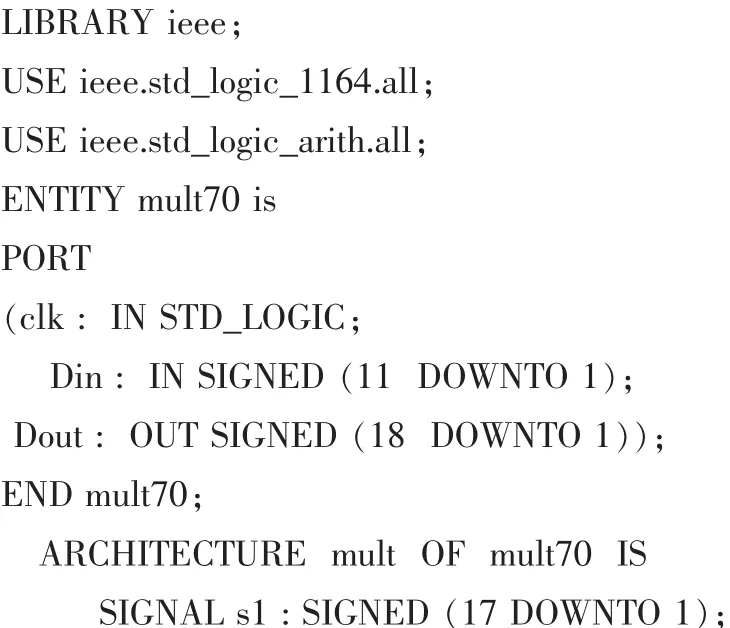

從資源和速度考慮,常系數乘法運算可用CSD算法,將常系數分解成幾個2的冪的和形式,通過每一個分解因數的移位相加來實現乘法運算。對于本次設計分析各個乘法器的系數,實現輸入帶符號數據與固定數據兩個二進制數的乘法運算 ,比如31=32-1=2^5-2^0,分別左移5位和 0位;88=64+16+8=2^6+2^4+2^3,分別左移6位,4位和3位等。以此類推,乘法器其他系數按同樣的方法分解成2的冪的和形式。下面以乘70乘法器的VHDL語言來描述以上算法,70=64+8-2=2^6+2^3-2^1,分別左移6位,3位和一位;

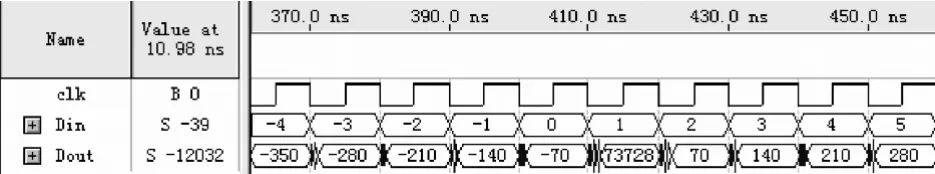

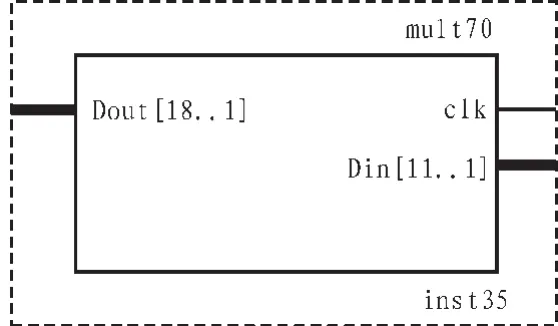

運行此程序可以得到驗證波形,如圖3所示。通過此仿真波形可以驗證程序的正確性。程序運行成功之后,打開File菜單欄的CreateUpdate選項,選擇Create Symbol File for Current File命令,系統自動生成當前程序的模塊,并以bsf文件的形式保存在制定文件夾,如圖4所示。

圖3 實現乘70的乘法器仿真波形Fig.3 Simulation waveform ofmultiplying unitby 70 times

圖4 乘70的乘法器模塊Fig.4 Module ofmultiplying unit by 70 times

其他乘法器模塊按同樣的方法生成,保存到同一個文件夾。

2.3 加法器模塊的實現

整個系統需要三級加法器:第一級加法器只需要輸入10位輸出11位的加法運算。第二級加法器包括4個加法器,需要考慮乘法器輸入輸出數據的位數。本次試驗用的乘法器都是專用乘法器,不同乘法器輸出的信號位數也不一樣。因此第二次使用加法器時需要設計4種專用加法器把從各個乘法器輸出的信號位數統一起來。

1)對于乘31和乘88乘法器需要設計17位數加18位數生成22位數的加法器;

2)對于乘106和乘54乘法器需要設計18位數加18位數生成22位數的加法器;

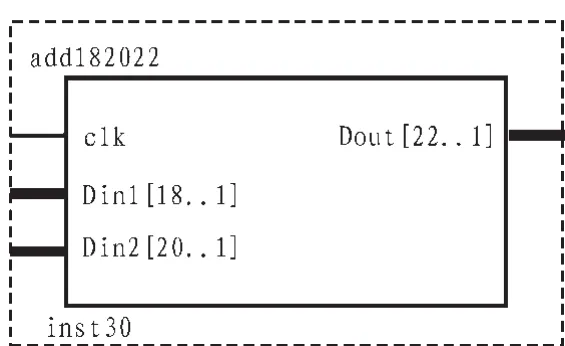

3)對于乘70和乘239乘法器需要設計18位數加20位數生成22位數的加法器;

4)對于乘401和乘499乘法器需要設計20位數加21位數生成22位數的加法器。

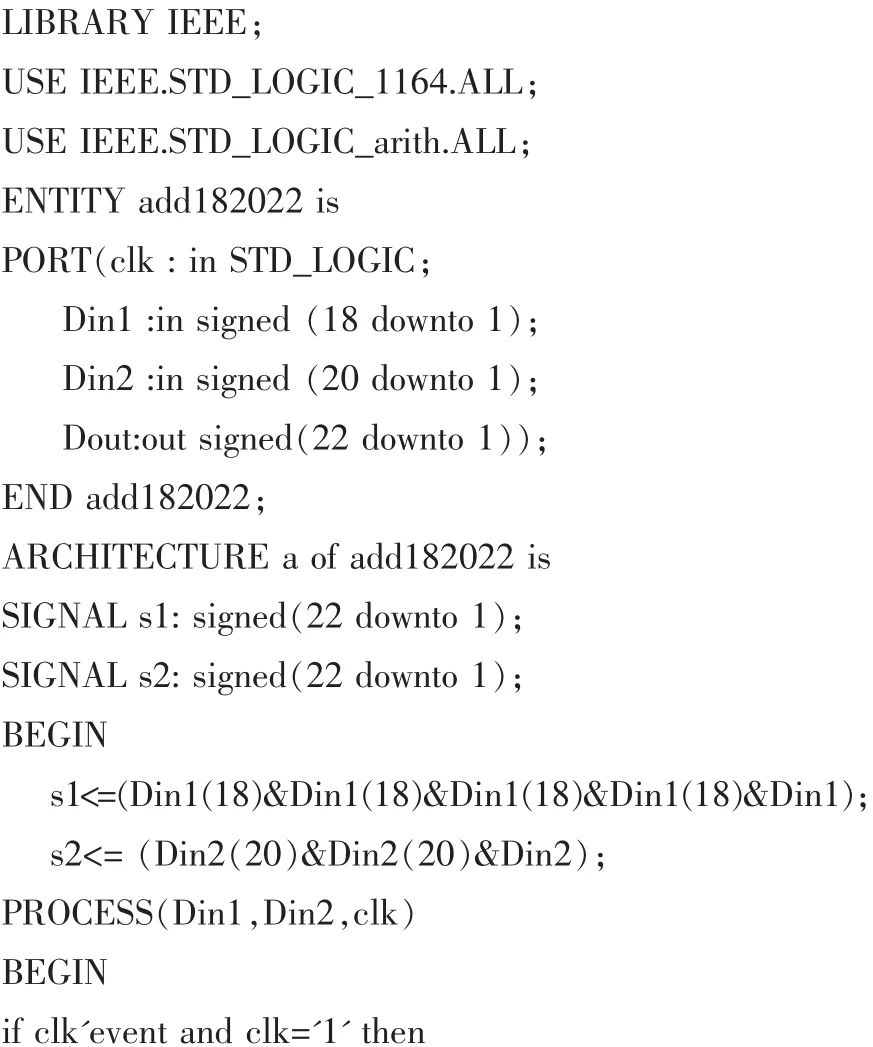

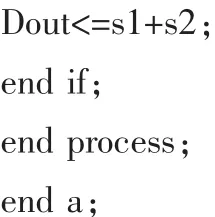

第三級加法器需要兩個能實現22位加22位生成23位數的加法器。以上幾種加法器用VHDL語言描述的思路是一樣的,現舉一個為例說明加法器的實現原理。

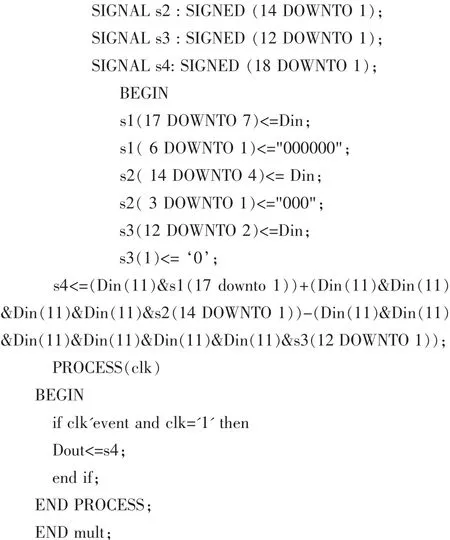

對于乘70和乘239乘法器需要設計18位數加20位數生成22位數的加法器,加法思路是位數少的被加數補最高位,生成位數高的加數。系統生成的18位數加20位數生成22位數的加法器的模塊如圖5所示。加法器部分程序如下:

圖5 加法器模塊Fig.5 Module of adder

減法器的原理與加法器類似,并行式減法器與加法器的區別僅僅在于最后的和數為兩數相減。

3 高效FIR濾波器的FPGA實現

根據以上思路,采用Altera公司的Quartuas II開發軟件對此FIR濾波器進行設計及仿真[5-6]。FIR濾波器的電路連接與其原理圖連接方式類似,首先打開Quartuas II軟件點擊Block Diagram/Schematic文件,新建一個bdf文件,然后調用生成的寄存器,各種加法器以及乘法器模塊,按照如圖1所示的原理圖前后連接可以形成FPGA濾波器整體電路,利用該軟件所提供的Waveform Editor進行時序仿真可以得到時序仿真波形。

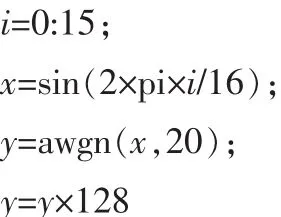

時序仿真需要一系列輸入信號,為了驗證方便利用matlab在正弦函數上取特定信噪比的幾個點作為輸入序列,本次設計選取的信噪比為20分貝,此函數為:

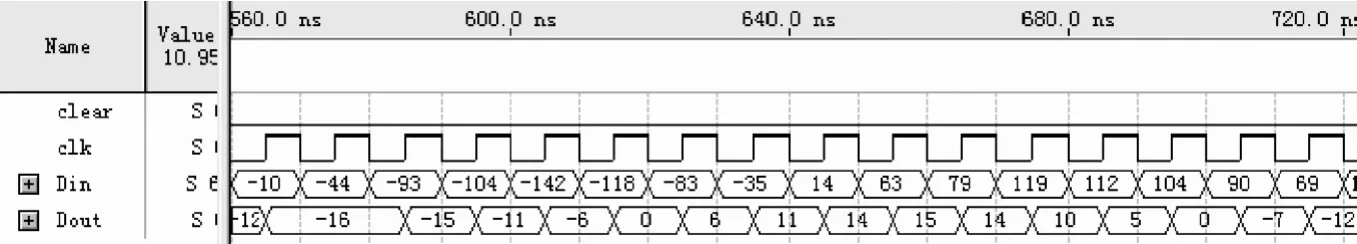

輸出結果:y=[14,63 ,79,119,112 ,104,90,69,-10 ,-44,-93 ,-104, -142,-118,-83 ,-35], 此序列代表信噪比為 20分貝的正弦信號序列,把這些序列作為以上系統的輸入信號運行,結果如圖6所示,圖上clk是控制輸入的時鐘信號,時鐘頻率為100 MHz,clear是加法器及鎖存器的清零信號,低電平0有效,Din是外部的輸入信號,Dout是最終的外部輸出信號。

理論上,以上序列y的值與濾波器系數求卷積,可得濾波器理想輸出值 conv(x,y):

conv (x,y) ={1.97, 5.22, 12.67, 15.12, 15.61, 13.75,9.56,3.59,-3.17,-9.50,-14.16,-16.28,-15.64,-12.7,-8.48,-4.23}

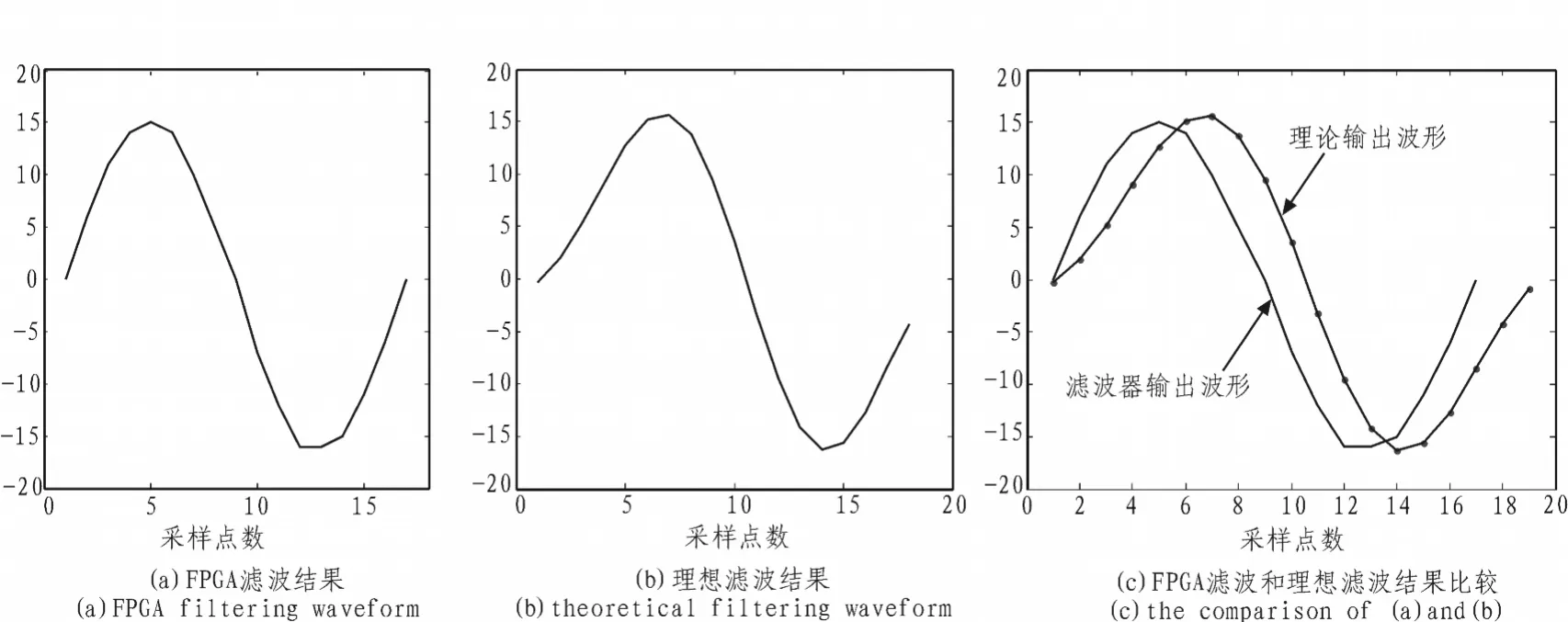

通過matlab軟件可以畫出以上兩種數據Dout和conv(x,y)對應的圖形,分別如圖 7(a)和(b)所示。

圖6 FIR濾波器仿真波形Fig.6 Simulation waveform of Finite Impulse Response digital filter

圖7 FPGA仿真濾波結果與理想FIR濾波結果對比圖Fig.7 The comparison of FPGA filtering and theoretical filtering

從以上數據和波形可以看出理論值除個別點數外,波形基本沒有毛刺。圖中橫坐標是采樣點數,縱坐標代表的是采用10位二進制數量化后的幅值,圖中的實線是FPGA濾波結果,帶固定點的實線是濾波器理論值。從圖7可以看出,用本文提出的設計方案實現的基于FPGA芯片和MATLAB軟件的FIR濾波器的濾波結果與理想濾波結果是非常接近的,對比圖中FPGA濾波結果比理想值稍低,原因是由于在FPGA濾波器實現的過程中,為了節省硬件資源,將數據做了截掉低6位的處理,從而產生了一點誤差。但是,從仿真結果來看,該截掉低位的處理并不影響濾波器的性能。這次設計采用的是輸入信號信噪比等于20 db時的情況,使用過程中根據實際設計要求可以更改信噪比,隨著信噪比的降低輸出信號的恢復程度有所降低,一般按這種方法設計出來的低通濾波器最高可以恢復信噪比為-20 db的輸入信號。

4 結 論

FIR濾波器在數字信號處理的各個領域中起著很重要的作用,其性能優劣對信號處理的結果有舉足輕重的影響。該文采用對稱結構、被加法和移位代替的乘法運算、優化的CSD編碼、流水線技術、級聯技術等幾個方面,對傳統的FIR濾波器的設計方法進行了改進,并借助Altera公司的FPGA芯片和QuartusII軟件以及Matlab軟件對設計方案進行了仿真驗證。仿真實驗結果表明,該FIR濾波器的實現方案,具有工作速度快、實時信號好、節省硬件資源等特點,能夠滿足實際的數字系統的要求。

[1]李亞奇,張雅綺.線牲相位FIR數字濾波器[J].電子測量技術, 2005(6):35-36.

LI Ya-qi ,ZHANG Ya-qi.The design of a linear phase FIR digital filter[J].Electronic Measurement Technology.2005(6):35-36.

[2]王宏.MATLAB6.5及其在信號處理中的應用[M].北京:清華大學出版社,2004,231-251.

[3]梁靜.數字FIR濾波器的MATLAB設計和仿真[J].現代機械,2003(6):88-91.

LIANG Jing.The design and imitate of digital FIR filter by MATLAB[J].Modern Machinery.2003(6):88-91.

[4]Uwe Meyer-Baese.數字信號處理的FPGA實現[M].劉凌,胡永生,譯.北京:清華大學出版社,2003.

[5]張馳,郭黎利,孫巖.基于MATLAB及FPGA的高速FIR濾波器的設計[J].信息技術, 2006(7):31.

ZHANG Chi, GUO Li-li, SUN Yan.A high speed FIR filter design based on MATLAB and FPGA device[J].Information Technology, 2006(7):31.

[6]蔣立平,譚雪琴,王建新.一種基于FPGA的高效FIR濾波器的設計與實現[J].南京理工大學學報,2007(2):125-128.

JIANG Li-ping, TAN Xue-qin, WANG Jian-xin.Design and implementation of efficient FIR filter based on FPGA[J].Journal of Nanjing University of Science and Technology.2007(2):125-128.