基于FPGA的衛星數字頻率信號處理關鍵技術研究與實現

羅來金,曾連蓀

(上海海事大學 信息工程學院,上海 200135)

近年來FPGA以其硬件并行處理的高速性和可重配置性,在電子設計中得到了大規模的應用。伴隨著制作工藝和不斷進步及IP內核概念的出現,FPGA正在從傳統的系統粘合邏輯應用轉移到系統核心處理應用上來。

文中分析了傳統頻率信號處理方法的優缺點,采用ALTERA的Cyclone II系列FPGA完成某型衛星陀螺組合X、Y、Z軸方向的角速和溫度傳感器發送來的頻率信號的測量與處理,并通過RS-422串口通信總線實現了與主控計算機的雙向通信。相比于以往采用單片機、DSP等器件實現數字脈沖頻率的測量及其數據處理,采用FPGA以及特定的算法來實現數字脈沖頻率的測量及其數據處理,后者具有高速、高穩定度、高精度和高集成度的特點,不會出現程序跑飛的情況,滿足航天系統對頻率信號測量的特定要求。

1 頻率測量方法分析[1]

1.1 測頻法

測頻法就是在確定的時間Tw內,記錄被測信號的變化周期數(或脈沖個數)Nx,則被測信號的頻率為:Fx=Nx/Tw。該種測量方法會產生±1的計數誤差,測試精度與計數器的記錄值Nx有關,頻率越高精度越大,因此該測量方法適用于高頻信號的測量。

1.2 測周法

測周法需要有標準的數字基準時鐘頻率Fs,在待測信號的一個周期Tx內,記錄標準信號的周期數Ns。則被測信號的頻率為:Fx=Fs/Ns。該種測量方法Ns同樣也會產生±1的計數誤差,測試精度與計數器的記錄值Ns及標準頻率穩定度有關,適用于低頻信號的測量。

1.3 相檢寬帶測頻

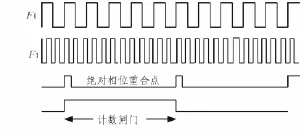

相位檢測法利用兩個頻率之間的周期性規律來產生計數閘門,這種周期性規律就是兩個頻率的最小公倍數周期,如圖1所示。

圖1 相位檢測法頻率測量原理圖Fig.1 Schematic diagram of phase detection frequency measurement

理論上在這樣一個計數閘門時間段內對標準頻率和被測頻率的計數都不會存在±1的誤差,沒有時間誤差,因此理論上精度無限高[2]。但實際上“絕對相位重合點”是不可能的,而且外加實際電路器件的延時,計數閘門也會存在相應的時間誤差,導致實際測量精度與理論有一定的差距。在此基礎上不少學者也提出并實現一些新的相位重合點檢測技術,精度在一定程度上得到提高,但算法復雜。

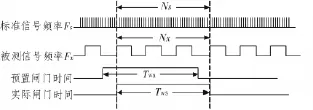

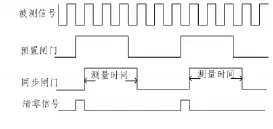

1.4 等精度測量法

等精度測量原理如下:在預置閘門信號的上升沿時不立即進行計數,而是等到被測信號脈沖的上升沿到來時開始計數,在閘門的下降沿到來時也不立即關閉計數,而是等到被測信號的上升沿到來時停止計數。等精度測頻的原理圖如圖2所示。

圖2 等精度測量原理Fig.2 Principle of equal precision measuring

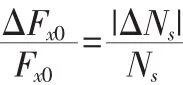

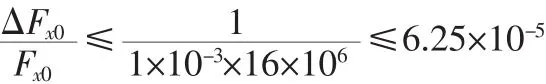

誤差分析如下:

假設待測信號頻率是Fx,標準信號頻率是Fs,在實際閘門時間TWS內的計數值分別為Nx和Ns,則可得到下式:

所以

由于待測信號Fx的計數時間是由它本身的上升沿控制的,所以在閘門時間內計數得到的Nx不存在誤差,而誤差產生只能是Ns帶來的,在TWS內對標準信號Fs計數得到的Ns可能相差 1,即|△Ns|≤1,假設待測信號的準確值為 Fx0,則可得到下式:

所以

采用等精度法進行頻率測量可以使得測量相對誤差在6.25×10-5以內。

2 頻率信號測量及處理系統

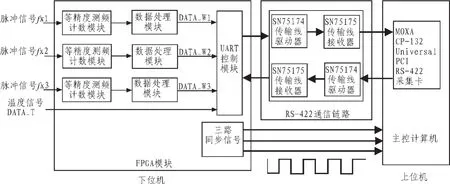

采用FPGA實現數字頻率信號的測量及處理的系統結構如圖3所示。

圖3 系統框圖Fig.3 Block diagram of system

該系統下位機主要包括:頻率信號的測量、頻率信號的計算、數據通信、同步信號的產生4部分,全部在一片FPGA芯片上實現。RS-422串口通信總線采用SN75174和SN75175分別作為傳輸線驅動器和傳輸線接收器。上位機采用MOXA公司的CP-132UL型RS-422卡,用VC++6.0提供的MScomm控件編寫測試程序,實現了工控機和下位機的高速率雙向通信。

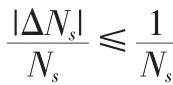

2.1 頻率測量模塊

該部分主要包括預置閘門時間產生、閘門時間同步、計數器、數據鎖存器、清零信號產生模塊。其中關鍵是解決時序問題,為保證計數的穩定輸出,需要在完成計數后進行鎖存并輸出,同時計數器清零,重新開始計數。如圖4所示,在設計中利用預置閘門時間和實際閘門時間的“相位時差”完成清零信號的產生,產生必要的清零信號。

圖4 清零信號的產生Fig.4 Clear signals generated

2.2 數據處理模塊

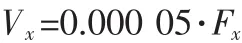

數據處理是本系統實現的關鍵之一,本系統需要進行計算的過程比較多,主要包括多位的乘法、除法以及數值比較、定點數與32位浮點數之間的轉換、32位浮點乘法,需要實現的數據處理過程順序如下:

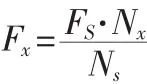

第一步:待測信號的頻率計算。

其中Fs為標準信號頻率16 MHz,Nx與Ns為計數器所得值。

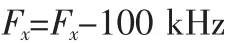

第二步:頻率歸一化。

第三步:電壓值計算。

第四步:角速度值計算。

Wx要求為32位單精度浮點數,由于FGGA很難實現小數的乘法,所以需要轉換成定點數或者浮點數乘法來實現[3]。在第二步和第三步之間進行定點數到32位浮點數轉換,采用32位單精度浮點數實現電壓值和角速度值的轉換,實現框圖如圖5所示。

圖5 FPGA數據處理方框圖Fig.5 Block diagram of FPGA data processing

伴隨著FPGA的發展,如今用它來實現定點數的乘除法是很方便,直接調用基本宏模塊提供的定點數乘除法IP核,進行相應參數的設置即可實現[4]。并且有的FPGA芯片還可以提供32位甚至64位的浮點數乘法器。方案使用的FPGA芯片是Altera公司提供的CycloneⅡ系列,該系列芯片提供了32位單精度的浮點數乘法器的基本宏模塊,利用其IP核及硬件乘法器可以加快產品的研發和提高系統的性能,因此在本模塊中采用了定點乘法器、定點除法器、定點數到單精度浮點數轉換等實用的IP核來解決系統中關鍵的運算模塊,大大提高了系統數據處理的性能[5]。

2.3 RS-422通信模塊

頻率信號采集系統需要與主控計算機進行通信,該系統中采用了RS-422串口通信總線。RS-422總線是一種單機發送、多機接收的單向、平衡傳輸規范,將傳輸速率提高到10 Mbit/s,克服了RS-232通信距離短、速率低的缺點,滿足航天系統的特定要求[6]。下位機FPGA實現串口通信框圖如圖6所示。

圖6 串口通信模塊Fig.6 Serial communication module

該部分主要由波特率產生模塊、發送與接收模塊、數據處理模塊組成。數據處理模塊完成數據發送和接收緩沖、CRC-16校驗及奇偶校驗。波特率發生模塊用于產生特定的時鐘信號。接收和發送模塊則完成數據的串行接收和串行發送。為了提高數據判決的準確性,采用16倍于波特率的時鐘信號對接收和發送波形進行采樣。

3 實驗結果及分析

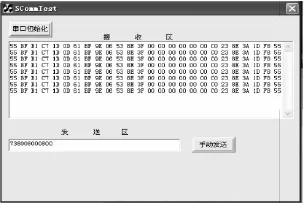

頻率輸入信號采用標準的信號發生器產生,同步信號輸出用LED燈指示。如圖7所示,將FPGA燒結文件下載到實驗系統上。每當上位機用串口調試軟件發送88請求命令(附帶CRC-16校驗碼),FPGA系統就會以0X55作為幀頭和幀尾,發送實時采集到的4組48位數據到上位機。

圖7 串口通信調試Fig.7 Debugging of serial communication

該系統經過地面衛星測試實驗環境中的長時間實驗,表明基于FPGA的衛星數字頻率處理系統工作穩定,成功實現了衛星數字頻率信號的測量、處理、通信過程。

4 結 論

采用ALTERA公司的Cyclone II系列FPGA,使用VHDL語言編寫FPGA代碼實現了對某型衛星4路頻率信號測量、數據處理、通信過程,頻率測量精度達到1.562 5×10-5。相對于MCU、DSP,采用單片FPGA完成衛星頻率信號的測量、處理和發送,具有低成本、低功耗、高速、高集成度、抗干擾的特點,具有無可比擬的優勢。

隨著FPGA技術和IP核技術的發展,今后可以采用速率更高,精度更高效的算法來實現頻率信號的測量及處理,將SOC技術應用到現代電子系統中。

[1]National Instruments.Frequency measurements:How-to guide[EB/OL]. (2011-03-18).[2011-04-10].http://zone.ni.com/devzone/cda/tut/p/id/7111.

[2]王海,周渭,宣宗強.高精度頻率測量技術及其實現[J].系統工程與電子技術,2008,30(5):981-983.

WANG Hai, ZHOU Wei, XUAN Zong-qiang.High accuracy frequency measurement scheme and its implementation[J].Systems Engineering and Electronics,2008,30(5):981-983.

[3]Lee B,Burgess N.Parameterisable floating-point operations on FPGA[J].Conference Record of The Thirty-sixth Asilomar Conference on Signals, Systems, and Computers,2002(2):1064-1068.

[4]Altera.CycloneⅡ Device Handbook,Section 1.CycloneⅡdevice family data sheet[EB/OL].(2008-02)[2011-04-23].http://www.altera.com.cn/literature/hb/cyc2/cyc2_cii5v1_01.pdf

[5]Altera.Floating-point megafunction user guide[EB/OL].(2011-05)[2011-05-23].http://www.altera.com.cn/literature/ug/ug_altfp_mfug.pdf.

[6]丁云霞,曾連蓀.基于VC++6.0的RS-422串口通信設計[J].信息技術,2010(9):73-75.

DING Yun-xia,ZENG Lian-sun.RS-422 serial communication based on VC++6.0[J].Information Technology,2010(9):73-75.