74LS161異步置零法構成任意進制計數器的Multisim仿真

任駿原

(渤海大學 數理學院物理系,遼寧 錦州 121000)

Multisim仿真軟件是由加拿大InteractiveImageTechnologies公司開發的一種基于SPICE工業標準的EDA軟件,它就像一個真正的實驗工作臺,將電路原理圖的輸入、虛擬儀器的測試分析和結果的圖形顯示等集成到一個設計窗口[1-3]。

在用Multisim仿真軟件進行計數器狀態變化過程波形仿真分析時,用虛擬儀器中的字組產生器做實驗中的信號源產生所需的各種輸入信號,用四蹤示波器觀測輸入、輸出波形,可直觀描述計數器的工作特性,且解決了計數器工作波形無法用實際電子實驗儀器進行分析驗證的問題[1]。

1 74LS161的功能及異步置零法

74LS161是集成4位二進制加法計數器[1-2],功能表如表1所示。其中CLK為時鐘脈沖輸入端、ENP及ENT為計數控制端、~LOAD為預置數控制端、~CLR異步置零控制端、DCBA為預置數輸入端、QDQCQBQA為狀態輸出端、RCO為進位輸出端,單片74LS161有從0000~1111共16個計數狀態。

利用74LS161的預置數控制端~LOAD或異步清零端~CLR在計數循環過程跳過2n~N個狀態,可構成任意N(N<2n)進制計數器,基本方法有置零法和置數法[1-2]。

用異步置零法將74LS161構成任意進制計數器時,使用計數和異步清零功能:用計數功能完成0~過度狀態(最后一個有效狀態 +1的狀態)的狀態轉換、將過渡狀態進行譯碼產生~CLR=0的異步置零信號在過渡狀態異步清零。

過渡狀態持續時間極短,~CLR=0的異步置零信號形成并完成置零后立刻消失。

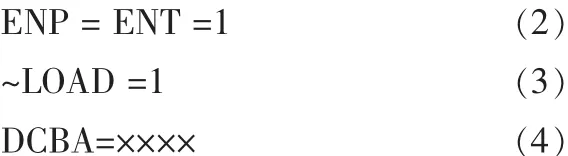

過渡狀態非完全譯碼時,僅由過渡狀態中為1的Q端狀態產生~CLR=0 信號,~CLR 的邏輯表達式為[1-2]:

即~CLR等于過渡狀態中值為1狀態變量的與非。

74LS161的其他控制端、輸入端的邏輯表達式為[1-2]:

表1 74LS161功能表Tab.1 Function table for 74LS161

2 異步置零法Multisim仿真方案設計

2.1 異步置零法的狀態圖及仿真方案設計要求

用Multisim10版本以構成10進制計數器為例,說明Multisim仿真方案設計。

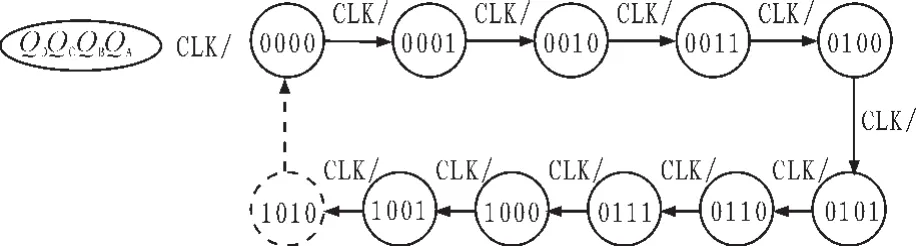

異步置零法10進制計數器的狀態圖如圖1所示,其中0000~1001為正常計數的狀態,過渡態為QDQCQBQA=1001+1=1010,1010過渡狀態形成~CLR=0信號完成置零后消失,作用10個時鐘脈沖完成一個計數周期的循環。

圖1 異步置零法的10進制計數器狀態圖Fig.1 State diagram of decimal counter using asynchronous reset method

仿真方案設計的要求是以時序波形圖方式直觀顯示計數過程、過渡狀態形成~CLR=0信號的過程,從而便于直觀理解過渡狀態的作用及計數原理。

其中,持續時間極短的過渡狀態及~CLR=0信號的形成過程的波形顯示是用Multisim軟件仿真的技術關鍵,在實際硬件實驗中是難以實現的,用Multisim軟件仿真亦需要對仿真方案進行正確的設計。

2.2 Multisim仿真實驗方法

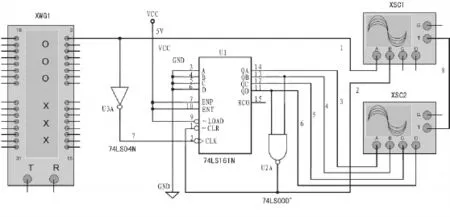

構建的仿真實驗電路如圖2所示。

1)時鐘信號選擇

選擇Multisim中的字組產生器產生計數器的時鐘脈沖信號。

字組產生器輸出10進制計數所需的10個時鐘脈沖信號,需在字組產生器的數據欄內以16進制(Hex)依次輸入 0、1、0、1、0、1、0、1、0、1、0、1、0、1、0、1、0、1、0、1、0 共 21 個 字 組數據,并對最后一個字數據進行末地址設置 (Set Final Position),完成所有字組信號的設置[3-4]。并設置頻率為fCLK=1 kHz(周期 TCLK=1 ms)。

仿真實驗時,字信號發生器的輸出方式為全部(BURST)時剛好顯示一個計數周期的波形、字信號發生器的輸出方式為單步(STEP)時可逐個脈沖輸出便于觀察每個時鐘作用后計數器的狀態變化情況。

2)74LS161集成4位二進制計數器觸發方式修正

Multisim10版本中,集成4位二進制計數器74LS161的時鐘脈沖觸發方式有錯誤,為CLK為下降沿觸發,附加反相器74LS04(圖2中U3A)修正為和實際器件一致的上升沿觸發方式。

3)顯示儀器選擇

圖2 異步置零法十進制計數器仿真電路Fig.2 Simulation circuit of decimal counter using asynchronous reset method

實驗表明,Multisim中的邏輯分析儀可以同步顯示多路數字信號的波形,但對持續時間較短的~CLR信號及過渡狀態卻顯示不出來。因此圖2中選用Multisim中的2個四蹤示波器同步顯示時鐘脈沖信號CLK、異步置零信號~CLR及狀態輸出信號QAQBQCQD,其中四蹤示波器XSC1同步顯示CLK及~CLR信號,四蹤示波器XSC2同步顯示QAQBQCQD信號,兩個示波器的面板以部分重疊方式顯示,如圖3所示,且兩個面板的Timebase區中的Scale、X position要設置一致,顯示一個計數循環周期的波形。

4)過渡態及~CLR異步置零信號的延時

圖2中U2A與非門74LS00用于在過渡態形成~CLR=0的異步置零信號,為能明顯觀察過渡態、~CLR信號的形成過程,需對與非門74LS00的上升延遲時間及下降延遲時間進行增大設置,通過Edit Model設置成rise delay=0.05 ms,fall delay=0.05 ms,使74LS00的平均延遲時間tpd=0.05 ms,亦可大于或小于0.05 ms,以能明顯顯示過渡狀態及異步置零信號為原則,但不能大于時鐘信號的周期。

3 仿真結果分析

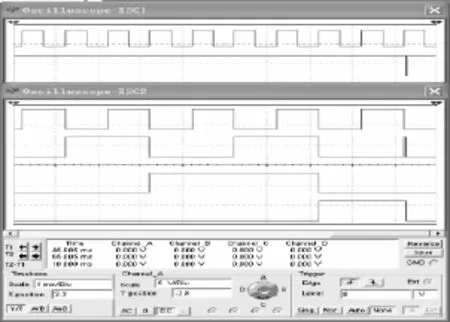

仿真顯示的時序波形圖如圖3所示。

圖3 仿真時序圖波形Fig.3 Timing diagram of simulation

圖3中,由上至下依次為時鐘脈沖信號CLK、異步置0信號~CLR、狀態輸出信號QA~QD的波形。

從左至右觀察圖3可看出:第1個時鐘脈沖信號CLK上升沿到來后計數器的狀態為QDQCQBQA=0001,~CLR=1;第2個時鐘脈沖信號CLK上升沿到來后計數器的狀態為QDQCQBQA=0010,~CLR=1;第3個時鐘脈沖信號CLK上升沿到來后計數器的狀態為QDQCQBQA=0011,~CLR=1;第4個時鐘脈沖信號CLK上升沿到來后計數器的狀態為QDQCQBQA=0100,~CLR=1;第5個時鐘脈沖信號CLK上升沿到來后計數器的狀態為QDQCQBQA=0101,~CLR=1;第6個時鐘脈沖信號CLK上升沿到來后計數器的狀態為QDQCQBQA=0110,~CLR=1;第7個時鐘脈沖信號CLK上升沿到來后計數器的狀態為QDQCQBQA=0111,~CLR=1;第8個時鐘脈沖信號CLK上升沿到來后計數器的狀態為QDQCQBQA=1000,~CLR=1;第9個時鐘脈沖信號CLK上升沿到來后計數器的狀態為QDQCQBQA=1001,~CLR=1;第10個時鐘脈沖信號CLK上升沿到來后計數器進入QDQCQBQA=1010的過渡狀態,使~CLR=0,持續暫短時間后計數器異步置零,使QDQCQBQA=0000。

經過10個時鐘脈沖信號作用后完成一個計數周期的循環,仿真實驗結果和圖1所示狀態圖的要求一致。

4 結束語

由于受實驗儀器的限制無法對計數器工作波形進行硬件實驗驗證,主要是,現有的信號發生器不能產生多路同步信號,現有的示波器多為雙蹤示波器無法同時觀測多路波形,用Multisim軟件仿真解決了這一問題。

本文的仿真電路,用2個四蹤示波器以時序波形圖形式顯示計數器輸出狀態,可直觀顯示計數過程、過渡狀態形成~CLR=0信號的過程及狀態變化與時鐘脈沖信號邊沿的對應關系。

所述方法具有實際應用意義。

[1]任駿原,騰香,馬敬敏.數字電子技術實驗[M].沈陽:東北大學出版社,2010.

[2]閻石.數字電子技術基礎[M].北京:高等教育出版社,2006.

[3]任駿原.用Multisim仿真軟件分析觸發器的狀態變化過程[J].實驗科學與技術,2011,9(1):53-56.

REN Jun-yuan.The state transition analyzing of flip-flop by multisim[J].Experiment Science&Technology,2011,9(1):53-56.

[4]任駿原.Multisim在觸發器工作波形分析中的應用[J].現代電子技術,2010,33(15):184-186.

REN Jun-yuan.An application of multisim to the working wave analyzing of flip-flop[J].Modern Electronics Technique,2010,33(15):184-186.

[5]任駿原.電子技術課程CAI教學模式的探索與實踐[J].電氣電子教學學報,2009,31(4):99-100.

REN Jun-yuan.The exploring and practice of CAI teaching mode of electronics technology course[J].Journal of Electrical&Electronic Education,2009,31(4):99-100.

[6]任駿原.基于次態卡諾圖的J、K激勵函數最小化方法及時序邏輯電路自啟動設計 [J].浙江大學學報:理學版,2010,37(4):425-427.

REN Jun-yuan.Minimization method of J and K excitation function based on next-state karnaugh maps and self-starting design of sequential logic circuits[J].Journal of Zhejiang University:Science Edition, 2010,37(4):425-427.

[7]張晶,李心廣.基于Multisim的電路設計與仿真[J].計算機仿真,2005,22(5):l09-152.

ZHANG Jing, LI Xin-guang.Multisim based schematic design and simulation[J].Computer Simulation,2005,22(5):l09-152.

[8]任駿原.數字電子技術實驗教學模式的改革與實踐 [J].渤海大學學報:自然科學版,2010,31(2):l65-167.

REN Jun-yuan.The reformation and practice of digital electronics practice teaching mode[J].Journal of Bohai University:Natural Science Edition, 2010,31(2):l65-167.