基于FPGA的任意波形發生器設計探究

徐宇寶,張曉東

(皖西學院 機械與電子工程學院, 安徽 六安 237012)

基于FPGA的任意波形發生器設計探究

徐宇寶,張曉東

(皖西學院 機械與電子工程學院, 安徽 六安 237012)

本文對 FPGA芯片實現的DDS結構中數字部分與接口部分進行了設計,將ROM改成RAM,可以實現對波形數據的更新.在對單片機控制的基礎之上,通過DDS技術的運用并利用FPGA芯片.以DDS模塊為核心的任意波形產生系統的形成得以實現.波形種類齊全、帶寬高、頻率分辨率高等是這種波形的主要特點,這是這些特點的存在,可以使得信號的調相功能得以實現.

DDS;FPGA;RAM;任意波形發生器

1 引言

當前社會信息技術發展迅猛,人們對于信息的交換(也就是通信)依賴性也越來越高,在這種背景下,提高通信的質量變成非常迫切的事情.想要提高當今通信的質量,就需要在通信的過程中著手,信號的發生、信號的傳輸和信號的處理是通信的幾個主要過程,但是最重要的過程是信號的發生,如果沒有可以進行利用的信號產生,那么信號的傳輸和信號的處理也都變的毫無意義[1].想要產生好的信號源,就需要有好的信號發生源,這樣可以降低在信號傳輸過程和處理過程中發生錯誤的概率,從源頭上避免信號發生階段的錯誤,就可以減少信號接收端出現錯誤的情況.因此,需要我們有一個技術質量非常高的信號發生器,基于 FPGA的任意波發生器就是很適合的.

2 方案選擇

當前可以實現可變頻信號的方法非常多,比如改變傳統 LC震蕩電路中電感的值,就可以產生出不一樣的頻率值,但是這種方法卻存在著輸出頻率不準確,帶寬不足等缺點.還有一種方法就是晶體震蕩電路,通常人們習慣稱之為晶振,在晶體電路中晶體決定著頻率,在以往人們通過實驗得出它的頻率穩定度可以達到 10﹣6量級,這樣我們就不需要擔心頻率輸出不穩定問題,但是又一個難題擺在了我們面前,在晶體電路中晶體決定著頻率,如果不能很好地制作晶振,就會導致頻率被固定,不可以進行調整,這樣就只能產生一種單一頻率的信號,這肯定是不符合信號實用性要求的.通過以上分析,我們可以看出這兩種方法都不是很好,但是不必擔心,隨著當前電子技術的發展的提高,以及在制作大規模集成電路工藝上的進步,出現了新的DDS技術,這為我們提供了新的選擇[2].

3 DDS 工作原理

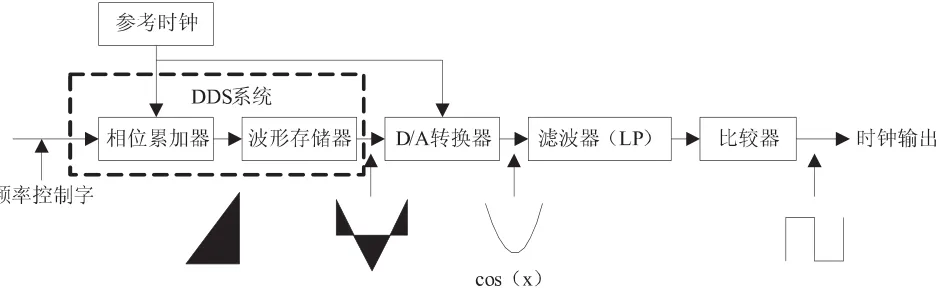

DDS工作原理如圖一所示.

圖1 基本DDS結構原理圖

相位累加器是 DDS技術的核心,它的作用就和一個計數器相似,當一個時鐘信號到來,就可以使相位累加器的輸出得到增加,增加的是一個步長的相位增加量,如圖1,頻率控制字決定了相位增加量的大小.在儲存器中有通過數據表形式保存的信號波形相位,它包含著相位信息,也就是待產生信號的一個周期的幅度.相位累加器中輸出信號的信息可以從數據表中讀出,這種信息是當前相位累加器輸出信號相位值對應的幅度數據,并將這種數據通過DAC的轉換功能變成模擬信號波形進行輸出,相位累加器通過線性相位累加的方式進行疊加,當達到滿量程時就可以進行一次計數溢出,輸出信號的頻率受溢出速率決定.想要使相位累加器有更高的溢出率,就要調高頻率控制字內的相位增加量,這樣才可以得到更高的信號輸出頻率.

4 FPGA 實現的波形數據接收模塊設計

基于 DDS的基本原理并通過 FPGA實現的任意波發生器,想要任意波的任意性得以實現必須改變 DDS的基本結構,可以通過將 ROM改寫成RAM,這樣可以利用 RAM的接口電路實現波形數據的更新,這樣就可以使任意波發生器的任意性得以實現[3].FPGA中實現的各電路中的模塊連接如圖2所示,我們結合圖 2來對控制部分、相位累加器、波形RAM等進行分析.

圖2 FPGA實現的電路示意

4.1 控制模塊的設計

DDS于單片機的接口問題需要通過控制模塊來解決,在 FPGA的實現中,對3個模塊進行了主要設計,分別是輸入寄存器模塊、地址選擇模塊、地址鎖存模塊.這三個模塊各有各的作用,接受單片機頻率控制字需要通過輸入寄存模塊來完成,單片機在FPGA各模塊進行工作時依據不同地址的選擇在地質選擇模塊內完成,對于單片機PO口地址和數據線復用問題的解決是在地址鎖存模塊內完成.在進行輸入寄存模塊的設計的時候,DDS要采用32位的相位累加器,單片機要選擇8位的,這樣單片機可以分四次寫入四個字節來形成一個頻率控制字.而地址選擇模塊的設計相對輸入寄存模塊的設計就簡單許多了,直接選用一個3—8的譯碼器就可以使地址選通的功能得以實現.因為地址鎖存模塊的PO口既是數據口也是地址總線的低8位,所以要選用51系列單片機作為單片機,在使用時就可以實現地址信號從分時復用的地址/數據總線的分離[4].

4.2 相位累加器的設計

結合FPGA本身的特性,并滿足任意波發生器的要求,即頻率分辨率達到10MHz,輸出的最大頻率要達到15MHz,所以要采用40MHz,32bit的相位累加器的系統時鐘來設計任意波發生器.本設計在采用EP1C3T144C8的FPGA器件,并直接用32bit累加器的時候,通過仿真實驗,可以看出這種情況下只能使系統時鐘最大達到約25MHz,不能達到40MHz,這肯定是和我們的設計不相符的,所以我們必須對相位累加器的結構進行改進,使之能夠達到我們要求的更高的工作速度.想要達到更高的工作速度,我們可以用一種在時序電路設計中常用的設計方法,就是流水線結構法,通過流水線結構來實現的累加器運行過程是這樣的,現將一個位數很長的加法拆分成N比較短的加法,并在N個時鐘周期內做完這個過程,然后進行結果的輸出,在采用這種流水線結構后使得加法器的字長變的更短了,這對于FPGA提高其工作頻率具有重大意義[5].

下面我們來詳細的對累加器流水結構的實現進行分析,將一個字長為N的累加器進行拆分,分成m個n位的累加器來工作,這樣拆分后的累加器的字長就變為了N=m×n.因為這m個n位的累加器之間是存在進位關系,所以這就造成了在一個周期內全部完成,這樣的情況下就可以運用流水的思想,將高位的累加器晚一個時鐘周期做累加,其對于低位累加器是延時的,這樣低位累加器在高位累加器進行累加的時候已經計算出了進位值,在低位累加器進行結果的輸出時也要延時,這是為了保證和高位累加器的結果同時輸出,這樣也可以使結果輸出的準確性得到保證.這個過程最終得出的結果是,一個值在進入累加器以后需要在m個延時以后才可以使得高位累加器計算出結果,在高位累加器計算出結果之后才可以完成最后的結果輸出.這樣通過m級延時才可以得到結果,但是不會對DDS相位累加器的工作產生影響,除了在過程中的m個延時以內,結果不會有變化,但其工作速度卻得到了很大的提高.通過流水線結構對相位累加器進行設計的時候,使m=8,n=4,這樣就可以使其工作效率達到最高值,大約是70MHz,超過了40MHz,符合我們的設計要求.

4.3 波形RAM的設計

在進行波形RAM設計的時候,要先使波形RAM的深度和字長得到確定,波形RAM的字長應該和任意波發生器設計中DAC選擇的字長一樣,都是 8位的,波形RAM選擇的地址線位數和相位累加器的輸出最高位數一樣,也是12位的.

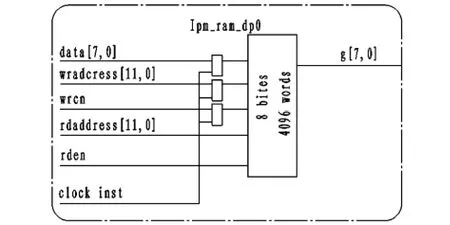

面對普通的DDS和任意波發生器不同,還要使波形RAM滿足設計要求,即具有兩個讀寫的端口這一情況,我們可以運用2套地址系統來更好地進行RAM內容的更新(也就是RAM的寫操作)和輸出波形幅度量(也就是RAM的讀操作).我們根據FPGA的特點,可以選擇EP1C3T144C8芯片內部的雙口 RAM來完成這個功能的實現.雙口 RAM示意圖如圖3所示.

圖3 雙口RAM示意

因為芯片內部的雙口具有 2組地址線,也就數讀地址和寫地址,所以數據線也有倆組,就是讀數據線和寫數據線,這樣對于完成波形 RAM的設計相對來說就簡單許多了,將寫數據線、寫地址線與單片機的數據線、地址線進行連接,這樣就可以通過單片機來實現RAM數據的更新工作.將讀地址線與相位累加器的輸出相連,將讀數據線與數據輸入相連,這樣就可以在讀數據線上進行波形幅度量化數據的輸出.

5 波形數據的生成及處理

5.1 波形數據的生成

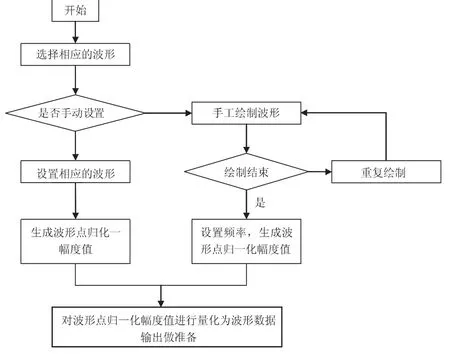

波形數據的生成總體流程圖如圖 4所示.因為下位硬件系統的波形RAM是波形點的幅度數據最終的儲存位置,由 2.3波形 RAM的儲存深度設計為 4096個單元,這樣的每個單元的字長是 8bits,這樣對于一個周期內的 4096個采樣點來說,要將這些個波形點的數據進行量化,最終要量化為0~255的整數.

5.2 波形幅度數據及頻率參數的處理

通過上述的過程可以使波形的 4096個點的數據生成,并進行儲存,但是由于 4096個點的波形數據是雙精度的,所以必須對這些數據進行處理來滿足其傳輸和儲存的需要.因為在另一個操作界面上,對信號輸出頻率值也是雙精度類型的,因此對于頻率參數也要進行數據處理.

圖4 波形數據生成總體流程圖

6 總結

本文對基于 DDS技術與 FPGA的任意波發生器的波形數據生成方法進行了研究,對DDS工作原理進行了簡單的介紹,對 FPGA實現的波形數據接收模塊設計進行了分析,主要包括控制模塊的設計、相位累加器的設計、波形 RAM的設計三種方法,這樣對于波形發生器性能的提高具有很大的意義.當前我國對于任意波發生器的研究生產還沒有真正形成產業鏈,當期國內的成熟產品大多是PC儀器插片,獨立儀器相對來說還很少,我國的任意波發生器比國外同類產片還存在相當大的差距,因為,進行基于 FPGA的任意波形發生器設計研究是非常急迫的事情.我們要通過對國外先進技術的研究分析來改進我國的技術,這樣才可以盡快的使我國技術落后的狀況得到改善.

〔1〕鄧耀華,吳黎明,張力鍇.基于FPGA的雙DDS任意波發生器設計與雜散噪聲抑制方法[J].儀器儀表學報,2009,30(11):2255-2261.

〔2〕何存富,周進節,鄭陽.超聲導波任意波形脈沖激勵源的設計與實現[J].測控技術,2011,30(10): 96-102

〔3〕韓旭,鄭磊.基于FPGA的任意波形發生器的設計與實現[J].電子測量技術,2013,11(7):824.

〔4〕張嚴,洪遠泉.基于FPGA的任意波形發生器設計與研究[J].現代電子技術,2013,34(10):157-162.

〔5〕唐建東.基于FPGA的任意波形發生器設計與實現[J].電子技術,2010,9(5):37-39.

TN9ll

A

1673-260X(2014)08-0037-03