一種基于寬帶信號的抽取濾波器設計

李 峰

(中國電子科技集團公司第20研究所,西安 710068)

?

一種基于寬帶信號的抽取濾波器設計

李 峰

(中國電子科技集團公司第20研究所,西安 710068)

級聯積分梳狀(CIC)濾波器結構簡單,所耗邏輯資源少,廣泛用于高速抽取和插值操作,但處理寬帶信號的幅頻響應不理想,難以滿足抗混疊性能。通過分析傳統CIC 濾波器結構和功率譜密度,改進型濾波器利用銳化級聯積分梳狀(SCIC)技術提高阻帶衰減并加入內插二階多項式(ISOP)補償器降低帶內容差,同時討論了現場可編程門陣列(FPGA)實現的硬件結構和寄存器位寬。仿真驗證了改進型濾波器具有更好的通、阻帶特性。

級聯積分梳狀濾波器;內插二階多項式補償器;幅頻響應;阻帶抑制

0 引 言

級聯積分梳狀(CIC) 抽取濾波器由Hogenauer[1]提出,分解為積分器(遞歸部分)和梳狀器(非遞歸部分)兩部分,其傳遞函數為:

(1)

式中:N為CIC濾波器級數,決定阻帶衰減程度;R為微分延遲,取值為1或2,決定頻譜響應中第一零點位置;M為抽取因子,由濾波器輸入、輸出采樣率決定,系數1/(MR) 確保0 dB的直流增益。其對應的頻率響應為:

(2)

實現時,可將M倍抽取器提到梳狀濾波器之前,使得積分器工作于輸入采樣率fs上, 而梳狀濾波器工作在抽取之后的低采樣率fs/M上,整個結構只用到加法器和寄存器,顯著降低了硬件資源損耗[2]。

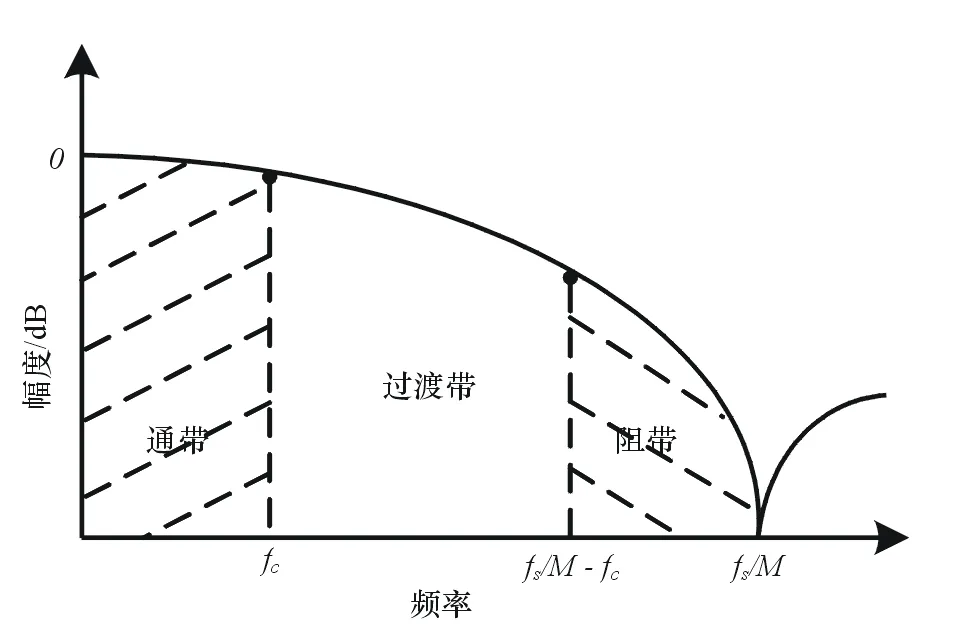

頻域上,CIC濾波器的零點位于fs/M(R=1)的整數倍處,抽取操作使得第一零點fs/M附近區域混疊到濾波器通帶中,如圖1所示。假設信號帶寬為fc,要求CIC濾波器的最小通帶截止頻率為fc,則fs/M-fc處的阻帶抑制和fc處的通帶衰減決定了濾波器的頻域性能。隨著fc的增加,幅頻曲線中的上述兩點逐漸靠近,CIC濾波器性能顯著下降。

針對寬帶信號,本文利用阻帶銳化和通帶補償技術對傳統CIC濾波器進行改進。濾波器設計輸入:輸入采樣頻率fs為160 MHz,抽取因子M為5,輸出采樣頻率為32 MHz,信號帶寬fc為9 MHz。設計指標:通帶波動小于1.5 dB,阻帶抑制大于50 dB。

圖1 CIC濾波器通帶、阻帶示意圖

1 CIC濾波器的改進

1.1 阻帶銳化

通過復用3個基本CIC濾波器,一種名為SCIC的濾波器被提出,既保持了CIC 濾波器“Multip lier - Free”的特點[3], 阻帶衰減又得到顯著銳化,其傳遞函數為:

Hsharpen(z)=3H2(z)-2H3(z)

(3)

式中:H(z)為如式(1)所示的基本CIC濾波器傳遞函數。

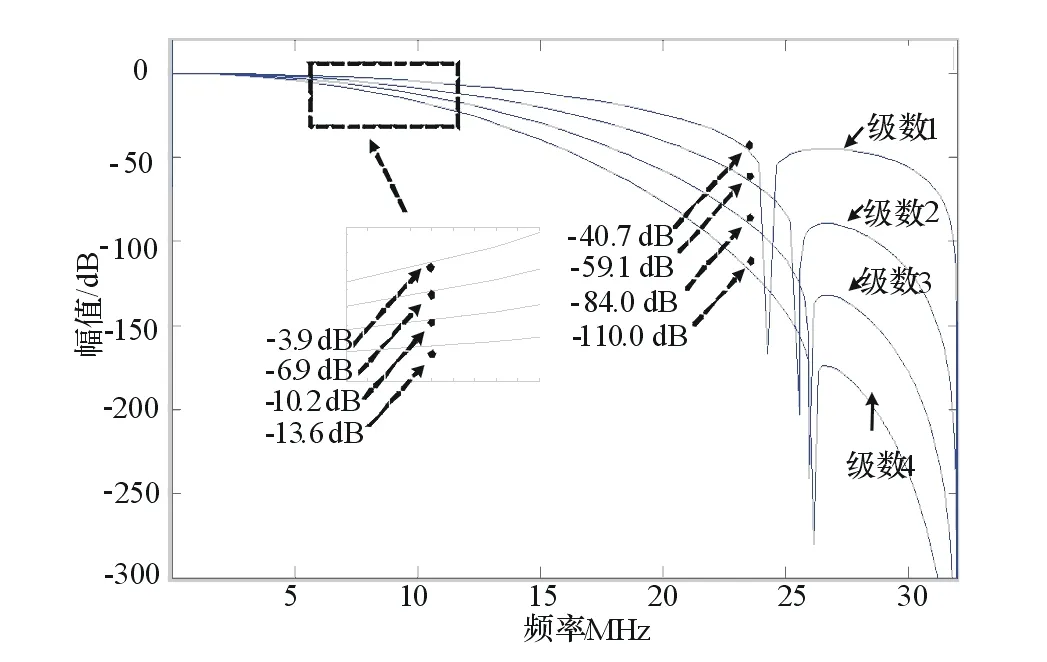

圖2反映了4種級數SCIC濾波器的幅頻曲線,在24~26 MHz之間的4條曲線分別存在一個陷波點,該點位于阻帶內,可忽略其對輸入信號的影響。由圖3可以看出,在相同微分延遲和抽取率的前提下,基本CIC濾波器的級數越高,SCIC濾波器的阻帶銳化效果越明顯,對于9 MHz的信號帶寬,SCIC濾波器采用級數1時,阻帶衰減(23 MHz頻率點)僅為-40.7 dB,不滿足設計要求;采用級數2、級數3和級數4的阻帶衰減分別為-59.1 dB、-84.0 dB和-110 dB,級數4的阻帶衰減性能最優。考慮通帶波動性能,級數3和級數4所對應的通帶波動均超過10 dB以上,顯著增加了通帶補償濾波器的設計壓力;而級數2的通帶波動為-6.9 dB,將其補償至-1.5 dB的設計指標具有可行性。綜合通帶波動和阻帶抑制性能,本文選擇級數2的SCIC濾波器。

圖2 SCIC濾波器通帶波動和阻帶抑制

(fs=160 MHz,M=5,R=1,fc=9)

1.2 通帶補償

為補償通帶6.9 dB的波動,在SCIC濾波器之后級聯1個內插二階ISOP濾波器[4],傳遞函數和頻率響應如下:

(4)

(5)

式中:I為正整數,為便于硬件實現,I是抽取因子M的整數倍。

本文設定I=M,系數1/|c+2|用于歸一化濾波器的直流增益。當c<-2時,ISOP濾波器的幅頻特性在[0,fs/2M]內單調遞增,恰好可以對SCIC濾波器的通帶衰減進行有效補償。此外,ISOP濾波器的最小幅度響應位于fs/M的整數倍處,與SCIC濾波器的零點重合,保證了補償后仍具有混疊抑制特性。

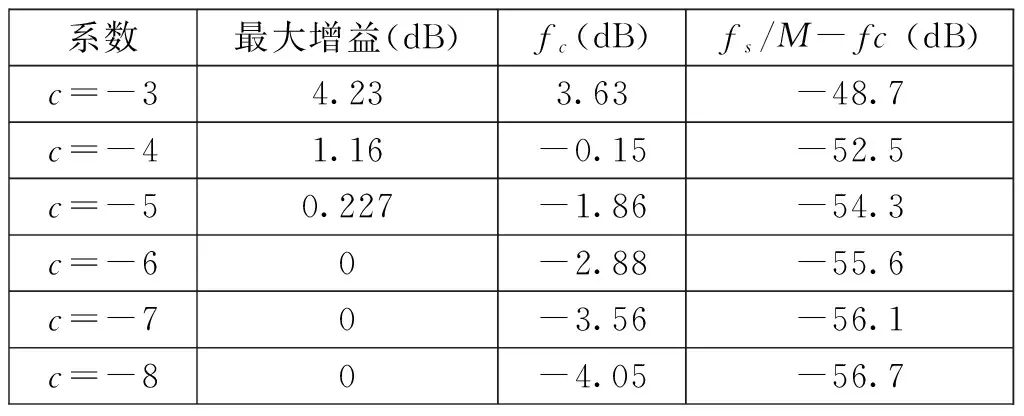

表1統計了SCIC濾波器加ISOP濾波器補償后,系數c對最大增益、通帶波動和阻帶抑制的影響。可以看出,當系數c=-3時,通帶內過補償以致出現4.23 dB的正增益,且阻帶抑制小于50 dB;隨著系數c的減小,通帶補償效果降低而阻帶抑制性能有所提高,但提高效果減緩,綜合考慮后選擇c=-4作為ISOP濾波器的實現方案。

表1 系數c對改進型濾波器的影響(fs=160 MHz,M=5,R=1,fc=9)

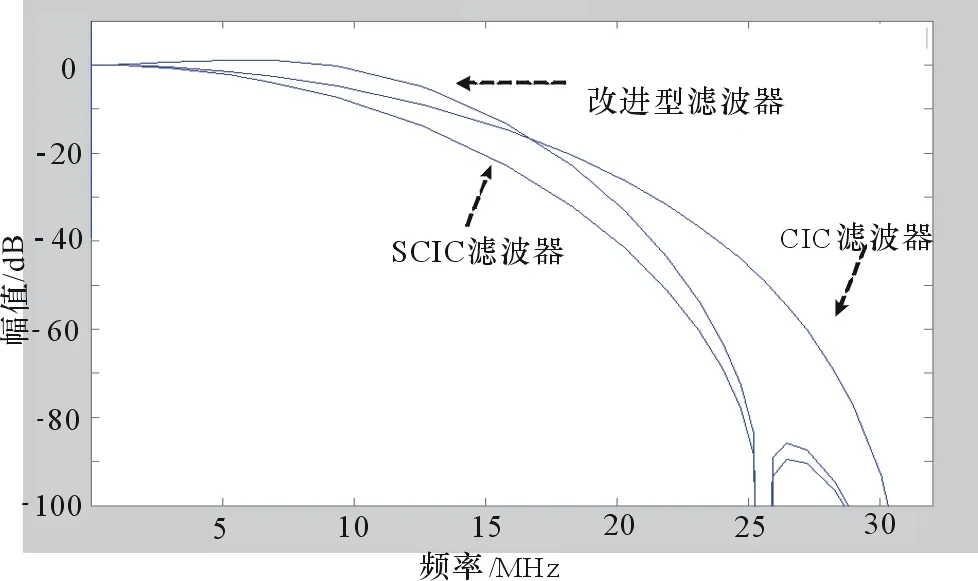

圖3給出了本文設計的改進型濾波器、SCIC濾波器和傳統CIC濾波器的幅頻曲線,對比發現:改進型濾波器在通帶波動和阻帶抑制性能上是SCIC濾波器和CIC濾波器合理的折衷。

圖3 改進型濾波器、SCIC濾波器和傳統CIC濾波器幅頻曲線(fs=160 MHz,M=5,R=1,fc=9)

2 FPGA實現

2.1 硬件結構

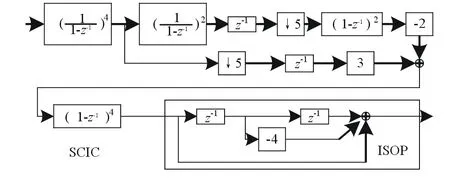

改進型濾波器由SCIC濾波器和ISOP濾波器串聯組成,而本文的SCIC濾波器又以2級傳統CIC濾波器為基礎。暫時不考慮直流增益因素,合并式(1)、式(3)和式(4)得到改進型濾波器的傳遞函數HADV(z)為:

(1+cz-M+z-2M)

(6)

借鑒傳統CIC濾波器實現過程中將抽取器置于積分器和梳狀濾波器之間的方法,使得梳狀濾波器和ISOP濾波器的系數降低至原系數的1/M,這部分的硬件處理速度也降至原速度的1/M,既便于電路設計又降低硬件功耗。基于這種方法,將式(6)進行調整得到:

式中:中括號內的減法運算使得數據通路中存在2個分支,其中1個分支為2級傳統CIC濾波器,單級CIC濾波器群延遲為(M-1)/2,2級CIC濾波器的群延遲為(M-1)[5],在該支路中再加入1個時鐘周期的延遲,使得支路延遲變為M,為保證兩支路群延遲一致,另一支路中直接引入M時鐘周期延遲,并將M倍抽取器置于該延遲單元之前,從而降低支路的運算速度。

通過上述分析,得到改進型濾波器的硬件結構如圖4所示。其中1/(1-z-1)和(1-z-1)為傳統CIC濾波器的積分和梳狀部分,乘(-2)、乘(-4)運算可以利用移位操作實現,乘3運算利用移位加法操作實現,整個濾波器不包含任何乘法電路,為現場可編程門陣列(FPGA)節省了大量邏輯單元。

圖4 改進型濾波器的硬件結構

2.2 寄存器位寬

改進型濾波器包含積分運算,即對輸入數據不斷累加,這要求內部寄存器必須具有合理的位寬,否則中間運算結果會發生溢出。寄存器位寬的設計原則為:保證改進型濾波器在最大增益處不發生溢出。

首先分析改進型濾波器的直流增益,傳統CIC濾波器直流增益為(RM)N[6],在此基礎上結合式(3)和式(5),得到改進型濾波器的直流增益計算公式為:

(8)

在ISOP濾波器的補償作用下,如果最大增益發生在直流點,最大增益和直流增益計算公式相同;若ISOP濾波器過補償,如圖3所示,最大增益發生在某一頻點,則最大增益在直流增益的基礎上乘以一個增量因子KProd,該增量因子可以通過仿真獲得,根據表2中c取-4時最大增益為1.16 dB,得到本文改進型濾波器的增量因子等于1.143。依據寄存器位寬設計原則,得到寄存器位寬WREG的計算公式為:

WREG=Win+log2KProd+2Nlog2(RM)+

(9)

式中:Win為濾波器輸入位寬。

將前面給出的設計輸入代入上述公式中得到改進型濾波器的寄存器位寬為Win+17,即內部寄存器位寬在輸入位寬的基礎上增加17位。

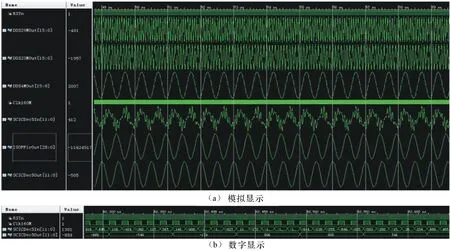

3 設計驗證

采用Verilog語言對圖4所示的改進型濾波器進行描述,選用Xilinx公司XC7K325T芯片在Vivado14.3開發環境下仿真綜合。濾波器輸入、輸出位寬12位,內部寄存器位寬29位,輸入采樣率160 MHz,5倍抽取,設計綜合后占用FPGA資源Slice 查找表(LUT) 498個、Slice 寄存器736個。

利用Vivado自帶的直接數字頻率綜合器(DDS) IP核輸出4 MHz的正弦信號,同時疊加上23 MHz、29 MHz的噪聲,產生如圖5所示的不規則信號并送入改進型濾波器。上圖將仿真結果用模擬信號形式顯示,可以看出,濾波器將23 MHz和29 MHz的高頻噪聲濾除,保留4 MHz的正弦信號,與原4 MHz正弦信號相比僅幅值減小,減小程度由改進型濾波器在4MHz頻點處的增益決定。圖5以數字形式的仿真結果顯示了濾波器輸出信號變化周期是32 MHz,實現了5倍抽取的功能。

圖5 改進型濾波器仿真結果

4 結束語

將SCIC銳化技術和ISOP補償濾波器相結合,提出了一種改進型抽取濾波器。與傳統CIC濾波器相比,該濾波器在通帶波動和阻帶抑制上得到顯著提升。文中推導出改進型濾波器的傳遞函數,對其分析后提出FPGA實現的硬件結構,并將抽取器置于數據通路的合理位置,降低了部分模塊的處理速率,在邏輯資源損耗不變的前提下,有效節省了硬件功耗。仿真綜合驗證了改進型濾波器滿足設計指標要求,使其在通信系統中具有較高使用價值。

[1] Hogenauer E B.An economical class of digital filters for decimation and interpolation[J].IEEE Transactions on Acoustic,Speech and Signal Processing,1981,29(4):155-162.

[2] 楊小牛,樓才義,徐建良.軟件無線電原理與應用[M].北京:電子工業出版社,2001.

[3] Dolecek G J,Harris F.Design of CIC compensator filter in a digital IF receiver[A].2008 IEEE International Symposium on Communications and Information Technologies.Vientiane[C].Lao PDR,2008:638-643.

[4] Hyuk J O,Sunbi Kum,Choi Ginkyu,et al.On the use of interpolated second-order polynomials for efficient filter design in programmable downconversion[J].IEEE Journal on Selected Areas in Communications,1999,17(4): 212-217.

[5] 鄭瑾,葛臨東,李冰.CIC抽取濾波器的改進及其FPGA 的實現[J].信息工程大學學報,2006,7(1): 57-59.

[6] 杜勇,路建功,李元洲.數字濾波器的MATLAB與FPGA實現[M].北京:電子工業出版社,2012.

Design of A Decimation Filter Based on Wideband Signal

LI Feng

(The 20th Research Institute of CETC,Xi’an 710068,China)

Cascaded integral comb (CIC) filters are widely used in high-speed decimation and interpolation operation due to the simple structure and fewer logical resources,but its amplitude-frequency response difficultly meets the anti-aliasing properties in dealing with broadband signals.After analyzing the traditional CIC filter structure and power spectrum density,this paper proposes a modified filter which uses sharpening cascaded integral comb (SCIC) technology to strengthen stopband attenuation and adds intertolated second polynomials (ISOP) compensator to reduce the in-band tolerance,discusses the hardware architecture of field programmable gate array (FPGA) realization and the bit width of register.The simulation verifies that the modified filter has better characteristics of pass-band and stop-band.

cascaded integral comb filter;intertolated second polynomials compensator;amplitude-frequency response;stopband rejection

2014-10-16

TN713.7

A

CN32-1413(2015)02-0093-04

10.16426/j.cnki.jcdzdk.2015.02.024