基于Spartan-6的微結構探測器APV25數字化系統設計

李興隆,胡守揚,周靜,智宇,陳雷,劉雯迪,趙明銳,李沛玉,李笑梅,2

?

基于Spartan-6的微結構探測器APV25數字化系統設計

李興隆1,胡守揚1,周靜1,智宇1,陳雷1,劉雯迪1,趙明銳1,李沛玉1,李笑梅1,2

(1. 中國原子能科學研究院 核數據重點實驗室,北京 102413; 2. 中國科學技術大學 核探測與核電子學國家重點實驗室,合肥 230026)

為滿足微結構氣體探測器多通道信號高速讀出的需求,文章基于現場可編程門陣列(FPGA)Spartan-6設計了128通道前置放大芯片APV25的數字化系統。該系統中,APV25輸出的串行模擬信號經模/數轉換芯片ADS5242進行模/數轉換,由Spartan-6接收、解串、緩沖和打包后,經千兆以太網傳送至計算機進行存儲和分析。經測試,該系統可實現APV25的最大采樣速率280kHz,基線噪聲低至716e-。輸入電荷量低于75000e-時,電荷響應線性良好。由于APV25的抗輻射特性,該系統有望用于空間多通道輻射探測系統。

APV25芯片;Spartan-6;數字化系統;千兆以太網;硬件設計

0 引言

核輻射探測器是人們認識核輻射的“眼睛”,其多以電信號輸出,需專用核電子學電路進行放大濾波等處理。APV25是一款128通道集成的模擬前置放大電路芯片,可對探測器輸出的信號進行前置放大和濾波等處理;它為大型強子對撞機(LHC)上的緊湊μ子線圈(CMS)探測系統中的硅微條探測器設計[1],具有較強的抗輻射性能,也可以應用到GEM等微結構氣體探測器的多通道信號讀出中[2]。APV25將128道模擬信號串行輸出,國外RD51合作組和意大利國家核物理研究院(INFN)分別為其設計了SRS(scalable readout system)和MPD(multi-purpose digitizer)2套數字化系統[3-4],國內則有中國科技大學設計的多通道讀出電子學系統[5],三者皆采用了現場可編程門陣列(FPGA)控制高速模/數轉換芯片(ADC)的方案。這主要得益于FPGA開發迅速、配置靈活的特點。中國原子能科學研究院核物理研究所中高能物理組(作者所在實驗室)實際測試了MPD V3.0系統,其采用VME總線傳輸數據,信號觸發率上限為3kHz,遠低于APV25的理論觸發率極限280kHz,這給高計數率應用帶來了一些限制。因此,我們開始自主研究設計數字化系統,以低成本Spartan-6 FPGA為核心,通過采用千兆以太網傳輸數據,提高觸發率。

1 系統結構

如圖1所示,該系統主要由APV25前端板、模/數轉換板、FPGA板和計算機構成。APV25前端板上載有APV25芯片,主要有穩壓供電、輸入耦合及保護、溫度檢測和地址設置等功能。前端板下通過板對板連接器連接至自主設計的背板,其主要作用為供電穩壓和接口轉換,背板與自主設計的模/數轉換板通過單根19芯HDMI A型線纜連接。該線纜同時傳輸APV25的模擬信號、FPGA對APV25的控制命令、時鐘信號和觸發信號。模/數轉換板上載TI的12位ADC芯片ADS5242以及相應的輸入信號緩沖、時鐘觸發單端信號轉差分信號、I2C信號電平轉換等電路。模/數轉換板板對板連接到黑金(ALINX)設計的Spartan-6 FPGA電路板,板載FPGA XC6SLX45、千兆以太網芯片及時鐘電源等電路。FPGA電路板經千兆以太網線連接至計算機的千兆網卡,計算機端采用C語言設計了數據采集軟件,通過網絡通信發送控制命令并接收數據。

圖1 APV25數字化系統結構框圖及實物圖

2 系統實現

下面將從APV25前端板及背板、模/數轉換板、FPGA板及邏輯設計、計算機端程序等4個部分詳細介紹該APV25數字化系統。

2.1 APV25前端板及背板

本系統采用了MPD設計方INFN設計的APV25前端板[4],由于接口不同,我們設計了新的背板進行接口轉換。考慮到芯片封裝會增大噪聲,該前端板通過金線鍵合工藝將APV25芯片裸片直接連接至印刷電路板(PCB),芯片上覆一小塊單面覆銅板進行保護和屏蔽。在輸入端,探測器的輸出信號首先經過靜電放電(ESD)保護芯片后,經電容耦合至APV25的信號輸入引腳。在輸出端,該板通過MOLEX 54722-0304板至板連接器輸出經放大、濾波等處理后的模擬信號,同時與FPGA通信,接收時鐘信號和觸發信號。

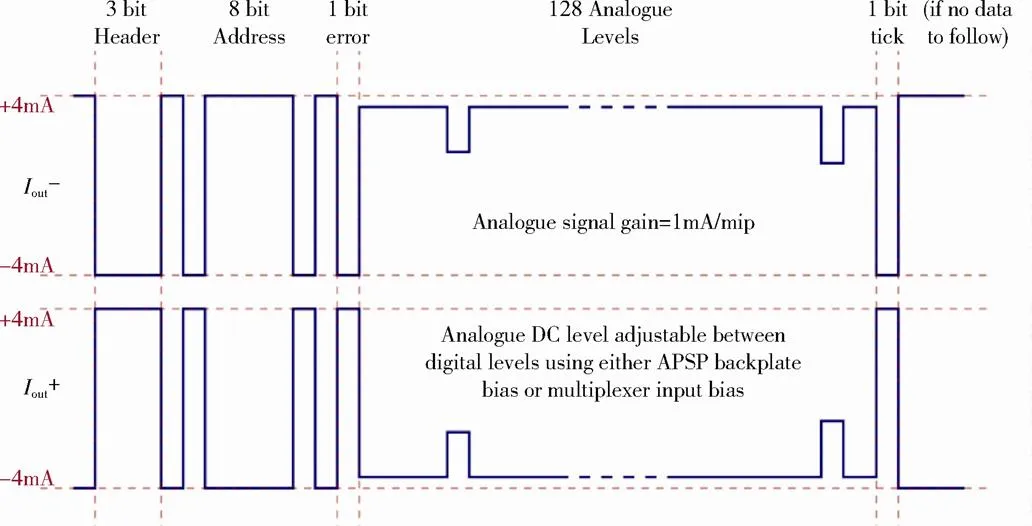

APV25芯片采用0.25μm CMOS工藝制成,其單通道的原理如圖2所示。輸入信號經增益可控的低噪聲電荷靈敏前置放大器放大后,由CR-RC成形電路進行成形濾波,輸出達峰時間50ns的脈沖信號,反相器則使得APV25可處理正負脈沖2種輸入信號。192單元的模擬管道則以40MHz的頻率對成形脈沖進行模擬采樣并緩存,模擬脈沖形狀處理器使得該芯片可工作于峰采樣、卷積和連續3次采樣3種模式。APV25的128個通道采用128∶1的時間復用方式輸出,故其輸出信號僅有1路;輸出信號采用類LVDS的差分電流模擬信號形式,故可用一般HDMI線纜進行信號傳輸,其信號構成如圖3所示[1],由起始位、地址位、錯誤位、128道模擬電平和滴答(tick)位組成,其中128道模擬電平對應各通道信號大小,其他位皆為數字電平。這種時間復用的傳輸方式,優點是簡化了系統連接,缺點是限制了事件率,當工作在峰采樣模式時,一次觸發將需要140個時鐘周期傳輸信號,即3.5μs,故其最高觸發率約為280kHz。

圖2 APV25 芯片單通道的原理框圖

圖3 APV25輸出信號結構

背板主要的作用是接口轉換和電源穩壓,19芯HDMI A接口穩定易用,其中的3組差分信號線(4、5、6;7、8、9;10、11、12)分別用于APV25模擬信號輸出、觸發信號和時鐘信號,15、16線用于APV25與FPGA的I2C通信。背板供電電壓為5V,經低噪聲線性穩壓器LT1965穩壓至3.3V,為APV25前端板供電。

2.2 模/數轉換板

模/數轉換板(圖4)的核心器件為TI公司的ADS5242芯片,該芯片為4通道12位ADC,最大采樣率為65MSPS,以串行LVDS信號輸出轉換后的數據,1對差分線傳輸1個通道的轉換結果,簡化了系統連接和PCB布線。該系統現連接1片APV25芯片,故只用到了4個ADC通道中的1個。APV25的輸出信號為幅值8mA的差分電流信號,該電流信號經板載100Ω電阻端接后,再經低失真差分ADC驅動器AD8138放大2倍,得到的最大輸入電壓幅值為1.6V。考慮到ADS5242最大差分輸入電壓為2.03V,AD8138的輸出是較為合適的。ADS5242提供共模電壓輸出引腳VCM,其電壓為1.45V,將該引腳連接至AD8138的共模輸出電壓設置引腳VOCM,如此二者的差分輸出/輸入便具有了相同的共模電壓。

圖4 模/數轉換板實物圖

模/數轉換板上采用SN65LVDS9638芯片將來自FPGA的單端觸發信號和時鐘信號轉換為APV25所需的LVDS信號,而FPGA的3.3V I2C信號則經PCA9306D轉換至APV25所需的2.5V I2C信號。轉換板輸入電源電壓為5.0V,各電路所需3.3、2.5、1.25V電壓則由低噪聲低壓差線性穩壓芯片LT1763提供。在PCB設計上,該板采用4層板結構,頂層為信號層,所有信號線均走該層,中間2層分別是地平面和電源平面,底層為各路電源走線。轉換板與FPGA板的連接為雙排標準2.54mm插針母座連接,ADC時鐘、轉換結果輸出、復位使能、串行通信以及APV25時鐘信號、觸發信號、復位信號、I2C通信信號均通過該接口連接至FPGA。

2.3 FPGA板及邏輯設計

該系統所用黑金LX45 FPGA板上載FPGA型號為XC6SLX45,屬XILINX最高成本優化的Spartan-6系列,其串行收發器和千兆以太網IP核完全滿足數字化系統需求。同時,該板上的RTL8211E千兆以太網物理層芯片和RJ45接口可直接用于與計算機的網絡通信。

該系統使用Verilog語言設計了FPGA的邏輯功能,如圖5所示,來自ADC的LVDS串行數字信號經Spartan-6的串/并轉換器ISERDES2轉換為6位并行數據,后經對齊、拼接還原為12位ADC值;這些ADC數據先送入異步FIFO緩存,讀出后按用戶數據報協議(UDP)打包,加入奇偶校驗字節,后經三模以太網介質訪問控制層IP核(TEMAC)以GMII接口發送至RTL8211E PHY芯片,最后經6類雙絞線傳輸至計算機千兆網卡。同時,利用FPGA的時鐘資源為ADC和APV25提供外部時鐘,方便調整時鐘相位同步。I2C模塊則負責配置APV25工作參數,對ADC的工作參數配置同樣采用串行通信。

考慮到APV25輸出的信號為40MHz的模擬信號,當APV25工作在最高觸發率280kHz左右時,模擬信號幀連續輸出,因此經12位ADC轉換后,最大有效數據速率為480Mbit/s;再考慮到以太網數據包的封裝,實際在FPGA的千兆網通信邏輯設計中,基本的要求是要能達到500Mbit/s以上的通信速度。考慮到邏輯資源的占用量,這里使用了UDP協議結合計算機端數據接收程序的累積確認機制實現。

圖5 FPGA邏輯設計框圖

2.4 計算機端程序

在計算機端,以C語言調用SOCKET API編寫了獨立的通信控制及數據存儲程序,通過以太網對系統采樣模式、參數等進行設置,并接收數字化后的數據。

相比于TCP協議,UDP通信協議有丟數據包的風險,因此在接收數據時,額外加入了累積確認機制[6],即計算機每接收到8個數據包后向FPGA返回一個確認信號,FPGA在接收到確認信號后再繼續發送接下來的8個數據包。為盡可能提高數據接收速率,確認信號的發送在另一個線程進行。如此,既避免了丟包,也不影響高速數據傳輸。經此設計,在迄今為止的實際測試中,包括APV25工作在最高觸發率(280kHz)的情況下,均未曾丟包。

接收到的數據經校驗無誤后,使用高能物理領域廣泛應用的ROOT程序進行數據分析。

3 測試結果

APV25及其數字化系統在輻射探測器系統中的作用是對探測器輸出的電荷信號進行測量和記錄,因此電荷測量的噪聲和線性范圍是需要測定的基本參數。對于數字化系統,其模/數轉換部分的標定是系統測試的基礎。下面分別給出這3方面的測量結果。

3.1 數字化系統標定

模/數轉換板將APV25輸出的模擬電流信號轉換為模擬電壓信號后,由ADC進行模/數轉換,故標定時,我們將不同大小和方向的電流輸入該系統,記錄并統計ADC輸出值。標定結果如圖6所示,線性擬合的2=0.999995。可見該系統線性很好,另外,標定中ADC值的方均根值小于0.65ADC單位。

圖6 數字化系統標定及擬合結果

3.2 噪聲測量

圖7所示為無輸入信號時該系統各通道的噪聲測量結果,經統計其平均值為4.82ADC單位,遠大于標定時的0.65ADC單位,故知該系統噪聲主要來源于APV25前放電路,后級模/數轉換部分的影響可以忽略。另外,由文獻[1]可知,APV25輸出1mA電流對應的輸入電荷為25000e-,結合標定擬合結果知1ADC單位對應148.6 e-,4.82ADC單位噪聲對應為716e-,滿足一般微結構氣體探測器的需求。

圖7 無輸入信號時APV25各通道噪聲測量結果

3.3 APV25線性范圍測試

APV25芯片內置有校準用的電荷脈沖產生器,產生的電荷經APV25輸入端輸入。調節輸入的電荷量,APV25成形后的波形變化如圖8所示。在無反相器的模式下,統計不同輸入電荷量對應的輸出波形幅值,得到APV25的電荷響應測量結果(圖9)。由圖9可知,在75000e-的輸入電荷范圍內,APV25的線性度都很好,這與APV25的設計者給出的測試結果[7]一致。

圖8 不同輸入電荷量時APV25的波形采樣結果

圖9 不同輸入電荷量時APV25的輸出波形幅值

4 結束語

本文以Spartan-6 FPGA為核心,采用ADS5242進行模/數轉換,以千兆以太網傳輸數據,設計并實現了APV25數字化系統。據測試結果,該系統實現了對APV25輸出信號數字化并傳輸存儲的功能,可工作在APV25最大觸發率下,累積確認機制的引入避免了UDP傳輸丟包問題,系統噪聲主要由APV25前放產生,在75000e-的輸入電荷范圍內,系統線性良好。得益于APV25芯片的抗輻射性能,該系統有望用于空間核輻射監測系統或輻射探測實驗的多通道探測器的信號讀出上。

[1] JONES L L, FRENCH M J, MORRISSEY Q R, et al. The APV25 deep submicron readout chip for CMS detectors[C]//5thConference on Electronics for LHC Experiments. Snowmass, CO, USA, 1999: 162-166

[2] 胡守揚, 蹇司玉, 周靜, 等. 基于APV25芯片的GEM探測器讀出電子學系統的測試與改進[J]. 原子能科學技術, 2014, 48(6): 1143-1146

HU S Y, JIAN S Y, ZHOU J, et al. Test and improvement of readout system based on APV25 chip for GEM detector[J]. Atomic Energy Science & Technology, 2014, 48(6): 1143-1146

[3] MARTOIU S, MULLER H, TARAZONA A, et al. Development of the scalable readout system for micro-pattern gas detectors and other applications[J]. Journal of Instrumentation, 2013, 8(3): C03015

[4] MUSICO P, BELLINI V, CAPOGNI M, et al. Hybrid silicon μstrip and GEM tracker for JLab hall: a high luminosity experiments[C]//Nuclear Science Symposium and Medical Imaging Conference, IEEE. Valencia, Spain, 2011: 1306-1308

[5] 李誠, 劉樹彬, 田靜, 等. 基于APV25多通道讀出電子學系統設計[J]. 核電子學與探測技術, 2016, 36(1): 5-9

LI C, LIU S B, TIAN J, et al. An APV25 based multi-channel readout electronics system[J]. Nuclear Electronics & Detection Technology, 2016, 36(1): 5-9

[6] CALVET D. A versatile readout system for small to medium scale gaseous and silicon detectors[J]. IEEE Transactions on Nuclear Science, 2014, 61(1): 675-682

[7] RAYMOND M, BAINBRIDGE R, CANDELORI A, et al. APV25 production testing and quality assurance[J]. Testing and Quality Assurance for Component-Based Software, 2003(3): 50

(編輯:閆德葵)

Design of APV25 digitization system for MPGD based on Spartan-6

LI Xinglong1, HU Shouyang1, ZHOU Jing1, ZHI Yu1, CHEN Lei1, LIU Wendi1, ZHAO Mingrui1, LI Peiyu1, LI Xiaomei1,2

(1. Science and Technology on Nuclear Data Laboratory, China Institute of Atomic Energy, Beijing 102413, China; 2. State Key Lab of Particle Detection and Electronics, University of Science and Technology of China, Hefei 230026, China)

To meet the demand of high-speed readout of multi-channel signals from micro pattern gas detectors, a digitization system is designed for the 128-channel preamplifier chip APV25 based on the field programmable gate array (FPGA) Spartan-6. In this system, the serial analog signal output by the APV25 is digitized by the analog-to-digital conversion (ADC) chip ADS5242. After the serial-to-parallel conversion by the Spartan-6, the data are acquired, buffered and packaged to the user datagram, and then sent to the computer via the gigabit ethernet for storage and analysis. In the test, the system reaches a maximum sampling rate of 280kHz for the APV25, and the pedestal noise is as low as 716 electrons. The linearity of the charge response is good when the input amount of charge is less than 75000 electrons. This system is expected to be used in the multi-channel radiation detection system in space thanks to the radiation tolerance of the APV25.

APV25 chip; Spartan-6; digitization system; gigabit ethernet; hardware design

O572.21

B

1673-1379(2018)02-0200-05

10.3969/j.issn.1673-1379.2018.02.017

李興隆(1990—),男,博士研究生,粒子物理與原子核物理專業。

李笑梅(1973—),女,滿族,博士學位,研究員,研究方向為中高能物理研究和先進氣體探測器研制;E-mail: xiao_mei_li@foxmail.com。

2017-12-12;

2018-04-01

國家重點研發計劃項目(編號:2016YFE0100900,2016YFA0400300);國家自然科學基金項目(編號:11775313);核探測與核電子學國家重點實驗室開放課題基金項目