SOI工藝抗輻照SRAM型FPGA設計與實現

郝 寧,羅家俊,劉海南,李彬鴻,吳利華,于 芳,劉忠利,高見頭,孟祥鶴,邢 龍,韓鄭生

(1. 中國科學院大學,北京 100029;2. 中國科學院微電子研究所,北京 100029;3. 中國科學院硅器件技術重點實驗室,北京 100029)

0 引 言

隨著半導體制造技術的發展,現場可編程門陣列(Field Programmable Gate Array, FPGA)電路的集成度、邏輯規模大幅提高,電路架構和可配置資源不斷優化,應用領域也隨之拓展。SRAM型FPGA電路因其具有靈活的可重復編程特性和快速產品化特性使其不僅在集成電路初始設計中被大量使用,在消費電子、通信、軍事和航天等領域也得到廣泛應用。目前,針對SRAM型FPGA電路在惡劣工作環境,特別是在航天[1]、核輻射等復雜電離環境下的應用引起廣泛關注[2-7]。商用SRAM型FPGA多采用體硅工藝的非加固設計,工藝自身的特點使其工作在惡劣電離環境下可靠性大幅降低,面向FPGA設計和工藝的輻照加固技術在應用需求的牽引下被不斷提出。

國內外多家機構已開展抗輻照FPGA電路的研發工作并形成系列產品,其中具有代表性的如Xilinx公司宇航級FPGA電路XQR4VSX55,配置存儲器單粒子翻轉飽和截面為4.37×10-8cm2/bit,塊存儲器單粒子翻轉飽和截面為4.19×10-8cm2/bit。國內某設計公司開發的規模為55K邏輯資源的高可靠FPGA電路,配置存儲器單粒子翻轉飽和截面為1.05×10-8cm2/bit,塊存儲器單粒子翻轉飽和截面為4.20×10-7cm2/bit。某航天研究所研制的百萬門級高可靠FPGA系列產品,其典型產品300萬門級FPGA配置存儲器單粒子翻轉閾值大于15 MeV·cm2·mg-1,抗總劑量水平為100 krad(Si)。顯然FPGA電路的抗單粒子翻轉能力除了受限于邏輯規模和特征尺寸外,體硅工藝在抗單粒子翻轉能力方面的局限性也是無法回避的因素。

SOI MOS器件制作在隔離層上的硅島中,因其全介質隔離有效消除背面寄生晶閘管,同時減小PN結面積和器件寄生電容等優點,在抗單粒子鎖定和單粒子翻轉方面有其先天優勢[8]。因此,基于SOI工藝的抗輻照FPGA電路研究也是當前集成電路領域的一個重要研究方向。

本文基于0.18 μm SOI CMOS工藝實現一款30萬門級抗輻照FPGA—IC300R電路,該款FPGA的邏輯規模和可配置資源與Xilinx公司的XCV300型FPGA[9]近似。

本文的組織結構如下:第1節IC300R電路架構介紹;第2節重點闡述IC300R電路的單粒子翻轉加固設計方法;第3節列舉了IC300R FPGA的電路特征;第4節為電路的電參數和抗輻照性能指標;第5節為總結和結論。

1 IC300R FPGA架構設計

IC300R FPGA電路的可配置資源以邏輯塊(Logic Tile, LT)為主,整體電路架構由圖1所示。電路主要由以下模塊組成:LT、數字時鐘管理模塊(Digital Clock Manager, DCM)、64k位存儲容量的塊存儲器(Block RAM,BRAM)、4個可編程管理模塊(Programmable Manager, PGM)以及可編程輸入輸出模塊(Input Output Block, IOB)。

圖1 IC300R FPGA架構示意圖Fig.1 IC300R FPGA architecture

IC300R FPGA芯片面積的65%由邏輯塊組成,共1536個邏輯塊呈32行、48列矩陣排布,其結構示意圖由圖2所示,每個邏輯塊由1個可編程邏輯單元(Configurable Logic Block, CLB)和1個通用布線模塊(General Routing Module, GRM)組成。

圖2 邏輯塊(LT)結構示意圖Fig.2 LT architecture

可編程邏輯單元包含3種電路模塊,分別為邏輯子塊、三態總線和輸入、輸出多路選擇電路,通過配置實現查找表、乘法器和進位等邏輯功能。通用布線模塊是可編程邏輯單元的布線資源,由單倍線、長線和16倍長度線三種類型連線資源,通過對通用布線模塊編程實現預期的互聯方式和邏輯功能。

表1 IC300R FPGA架構參數Table1 Architecture parameters of IC300R FPGA

2 輻照加固設計

SRAM單元作為位流文件和運算數據的臨時存儲節點廣泛分布于SRAM型FPGA電路中,該單元在單粒子事件敏感性方面有其結構上的弱勢,其中比較關鍵的影響是配置存儲器的單粒子翻轉事件[10]。業內同行已對FPGA單粒子翻轉加固技術進行了大量的研究,提出許多不同的加固方法,主要有以下三種:1)采用三模冗余技術(Triple Modular Redundancy, TMR),利用硬件備份關鍵數據實現加固效果[11-12];2)采用時序冗余技術,利用兩路相互之間存在延遲的時鐘,對單粒子入射產生的瞬時脈沖進行屏蔽[13];3)采用位流文件刷新技術(Scrubbing),通過不斷寫入配置信息抵御翻轉風險[7,14-15]。并在此基礎上衍生出許多類似的加固方法[16-19]。

上述方法在實現過程中,首先要面對的問題是芯片面積和功耗的增加,如三模冗余技術需三組相同的存儲電路配合表決電路實現,面積為非加固方案的三倍以上,電路待機功耗也隨之呈線性增加。其次是與加固方法相配合的硬件模塊自身的加固問題,硬件模塊不具備足夠的加固能力,在輻照條件下并不能正常實現加固性能。為提升IC300R FPGA的抗單粒子翻轉性能,電路設計采用輻照加固設計技術(Radiation Hardened by Design, RHBD)和輻照加固工藝(Radiation Hardened by Technology, RHBT)相結合的加固方法。

SRAM型FPGA電路中塊存儲器和配置存儲器均采用SRAM單元結構是輻照加固的關鍵模塊。SRAM單元通過反相器交叉反饋的方式存儲數據,當高能粒子射入存儲節點產生的電荷超過存儲單元翻轉的臨界電荷時,會將原有的數據改寫,造成FPGA電路功能中斷或存儲數據改變。大量研究表明,通過在SRAM單元交叉反饋回路中通過加入電阻、電容等延遲器件,增大兩個存儲節點之間數據變化的響應時間差,是提高SRAM單元單粒子翻轉性能的有效技術[20-22]。

在IC300R FPGA電路中我們采用了一種脈沖屏蔽加固的SRAM單元結構,并應用于塊存儲器和配置存儲器設計。如圖3所示,當粒子入射A點,在入射路徑上產生電子-空穴對,根據高能粒子入射電流雙指數函數模型,

(1)

式中:I(t)為收集電荷過程中產生電流;Q為粒子入射路徑上的沉積電荷數量;τα為電荷收集時間;τβ為粒子入射的持續時間。電荷收集過程產生的脈沖電壓造成A點數據翻轉,在電荷收集完成后消失,當脈沖電壓持續時間滿足存儲單元鎖存條件時,單元存儲的數據被改寫。六管單元反饋通路傳輸延遲較小,較低能量粒子入射產生的脈沖電壓即可滿足鎖存條件要求,因此抗單粒子翻轉能力較弱。

在脈沖屏蔽單元中,反饋回路中加入延遲結構D,通過調節D的參數改變反饋延遲時間。如圖4所示,假設在給定節點A處寄生電阻值固定,則粒子入射的脈沖電壓V(t)與電流I(t)值呈線性關系。存儲單元中反相器翻轉閾值為VTH,脈沖電壓高于VTH的持續時間Δt,

Δt=t2-t1

(2)

圖3 脈沖屏蔽加固SRAM單元Fig.3 Pulse shielded SRAM cell

在入射粒子能量確定的情況下,D的延遲時間tD滿足如下條件:

tD>Δt

(3)

高能粒子入射產生的脈沖電壓在傳遞到節點B時候已消失,實現單粒子翻轉加固的效果。

圖4 粒子入射電流雙指數函數曲線Fig.4 Double exponential function curve

由圖5仿真波形所示,其中V(A)為輸入對應圖3中的A點,V(B)為輸出對應圖3中的B點。從仿真結果可知,6管單元在B點的響應時間最小,加入延遲結構后,延遲時間tD隨參數的設置逐漸增大。

圖5 不同延遲條件存儲單元翻轉波形Fig.5 SRAM cell in/out waveforms with different tD

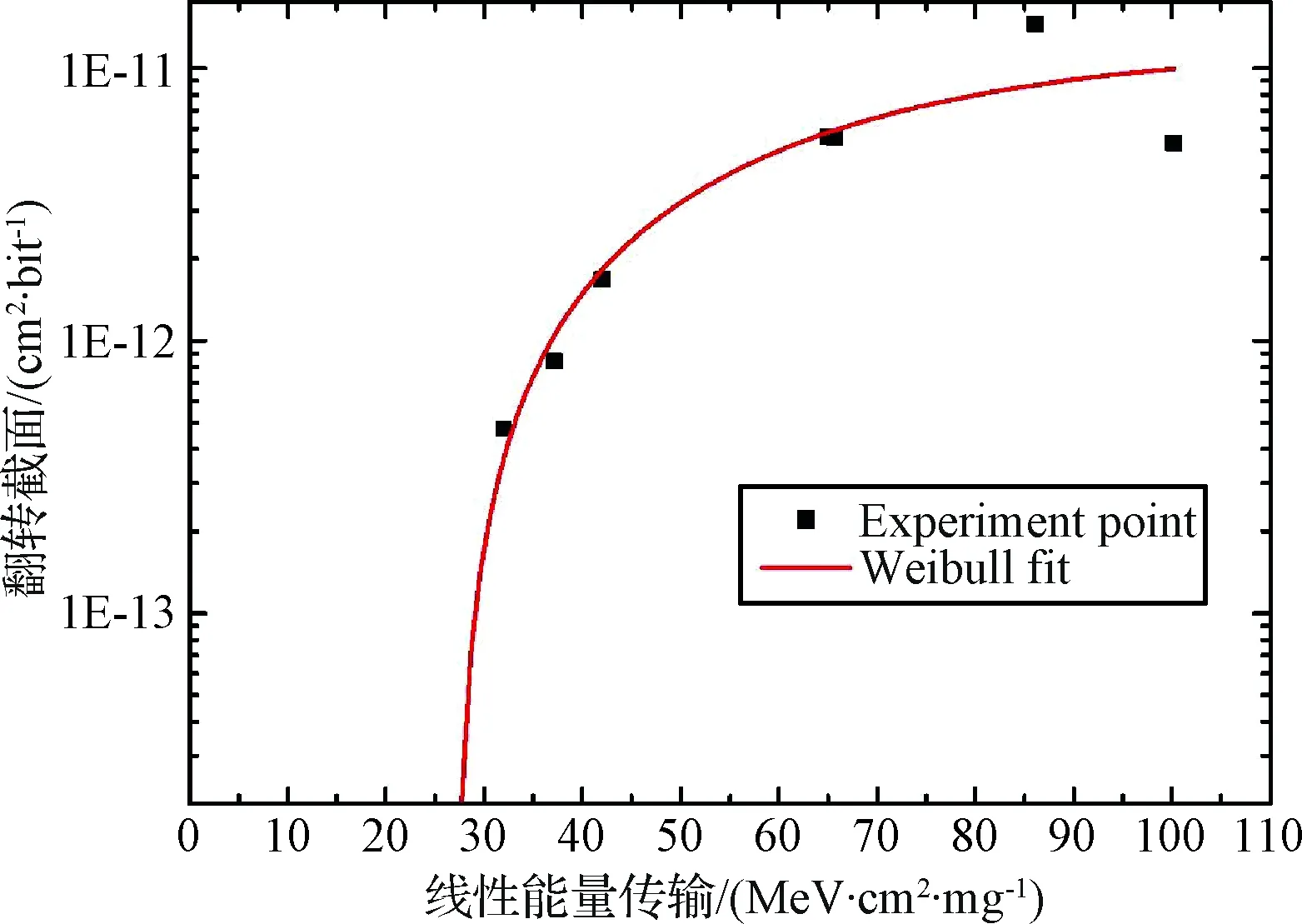

通過兩款基于0.18 μm SOI工藝設計的64k SRAM對6管單元和圖3所示脈沖屏蔽加固單元的抗單粒子翻轉性能進行評估,加固單元選用表2中CELL_RH2條件對應延遲參數。為了排除其他設計因素影響,兩款SRAM僅存儲單元存在差異。由圖6、圖7中Weibull擬合曲線所示,選取電路翻轉飽和截面值的10%對應的LET值為電路的單粒子翻轉閾值[23],采用脈沖屏蔽加固單元的電路單粒子翻轉閾值為SEULETTH>45 MeV·cm2·mg-1,采用6管單元電路翻轉閾值為SEULETTH>25 MeV·cm2·mg-1。在加固單元面積方面,延遲結構中不包含MOS器件,因此面積對比6管單元并未顯著增加,為3.32 μm×4.16 μm,6T單元為3.32 μm×3.43 μm,加固單元比6管單元增加約21.3%。

表2 加固單元與6管單元延遲時間仿真對比Table 2 Delay time comparison between different conditions of pulse shield cell and 6T cell

圖6 加固單元單粒子翻轉Weibull曲線Fig.6 Pulse shield cell SEU LET Weibull curve

圖7 六管單元單粒子翻轉Weibull曲線Fig.7 Standard 6T cell Weibull curve

3 FPGA電路實現

IC300R FPGA是基于0.18 μm部分耗盡SOI CMOS工藝設計,I/O電源電壓為3.3 V,內核工作電壓為1.8 V,采用6層金屬互聯。電路設計采用定制設計和自動布局布線相結合的設計方法。IC300R版圖根據LT模塊分布情況進行優化布局,水平方向1個塊存儲器與4個邏輯塊寬度基本一致,2個PAD與1個邏輯塊寬度基本一致;在豎直方向3個PAD與1個邏輯塊高度基本一致,通過全局規劃實現電路版圖在X方向和Y方向長度近似,為管殼選型和封裝提供便利條件。IC300R電路整體版圖面積為12.7 mm×13 mm,采用CQFP228形式封裝。

圖8 IC300R FPGA版圖和電路開帽圖Fig.8 IC300R FPGA layout and package outlook

4 功能測試和輻照測試

4.1 功能測試

FPGA測試和其他超大規模數字集成電路測試情況類似,面對不同的IP(Intellectual Property)和復雜的邏輯,不可避免的需要大量測試算法和資源[24]。當前FPGA電路以異質結構為主,其內部包含可編程互聯單元、邏輯塊和內嵌SRAM等模塊以及大量的IP,資源的豐富性和邏輯的復雜性對測試的完整性也提出了很高要求。大量的研究報告和文獻分析并提出整體或功能模塊級的測試方法[25-27]。

本文結合已有的研究成果開發針對IC300R FPGA的測試向量集,包括可編程邏輯塊矩陣、寄存器鏈、RAM測試、互連測試、查找表測試等共150條功能測試向量,覆蓋93%的邏輯資源和80%的互聯資源,并基于Teradyne J750EX測試平臺(如圖9所示),通過JTAG模式實現電路的配置和測試。

圖9 IC300R FPGA測試板Fig.9 IC300R FPGA test board

表3 IC300R與XCV300電路對比Table 3 Comparison between IC300R and XCV300

4.2 輻照測試

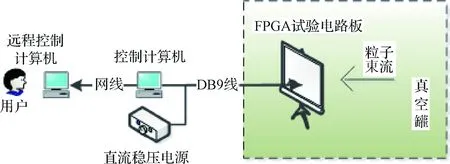

IC300R FPGA的輻照測試包括單粒子翻轉(Single Event Upset, SEU)、單粒子鎖定(Single Event Latch, SEL)和總劑量(Total Ionizing Dose, TID)測試。單粒子測試系統如圖10所示,控制計算機通過JTAG接口完成對待測FPGA的配置和回讀,并對回讀數據是否翻轉進行對比。直流穩壓電源完成對監控待測電路供電和對功耗實時監控,遠程控制計算機主要完成在線測試及試驗過程中特殊情況下的復位和離線操作。

圖10 IC300R單粒子翻轉試驗系統示意圖Fig.10 IC300 SEU test system sketch

圖11 IC300R FPGA單粒子翻轉測試Fig.11 IC300R FPGA SEU test

單粒子翻轉通過對塊存儲器和配置存儲器進行靜態測試[23]完成評估。照射源選用中國原子能研究院串列加速器(HI-13)進行Ge離子照射,能量為208 MeV,硅中射程為30.3 μm,LET值為37.3 MeV·cm2·mg-1,注量率為1×104ions/(cm2·s)。離子總注量達到1×107ions/cm2時,IC300R電路塊存儲器和配置存儲器無數據發生翻轉。

單粒子鎖定測試[23]選用蘭州重離子加速器Bi離子照射,該離子在硅中LET值為99.8 MeV·cm2·mg-1,注量率為1×104ions/(cm2·s)。IC300R電路在離子累積總注量達到1×107ions/cm2時為測試終止條件,無單粒子鎖定現象發生。

總劑量測試[28]選用Co-60放射源,在劑量率為50 rad(Si)/s條件下進行,累積總劑量達到200 krad(Si)時,進行電測試并加照50%劑量,經100 ℃、168小時高溫加電退火。終點電測試結果顯示IC300R電路功能正常,試驗前電路靜態電流為34.4 mA,退火后靜態電流為37.2 mA。表4列舉了全部輻照試驗結果。

表4 IC300R FPGA輻照測試結果Table 4 IC300 FPGA radiation test results

5 結 論

本文介紹的IC300R電路是一款抗輻照FPGA,采用0.18 μm SOI CMOS工藝并結合設計加固共同實現其抗輻照性能。輻照測試結果顯示,IC300R FPGA抗電離總劑量水平大于200 krad(Si),抗單粒子翻轉閾值大于37.3 MeV·cm2·mg-1,抗單粒子鎖定閾值大于99.8 MeV·cm2·mg-1。

在抗輻照設計加固方面,脈沖屏蔽加固SRAM單元被用于塊存儲器和配置存儲器中,僅比相同工藝條件的6管單元面積增加21.3%,實現了抗單粒子翻轉閾值大于37.3 MeV·cm2·mg-1設計預期。該加固單元應用在64k SRAM驗證電路中,使電路抗單粒子翻轉性能有明顯提升,單粒子翻轉閾值由采用6管單元SEULETTH>25 MeV·cm2·mg-1提升至SEULETTH>45 MeV·cm2·mg-1。

最后,電路級單粒子翻轉加固是一項系統工程,我們通過對64k SRAM電路和IC300R FPGA電路抗單粒子翻轉性能分析并確認,脈沖屏蔽加固單元是一種有效提升電路抗單粒子翻轉水平的SRAM單元結構。