電子束掃描線圈高速驅動器研制

楊波,許海鷹,桑興華

(中國航空制造技術研究院,北京 100024)

0 前言

電子束高速掃描是實現背散射電子成像、電子束圖像掃描、電子束多束焊等技術的基本要求。控制電子束高速掃描在電子束增材制造、電子束物理氣相沉積(EBPVD)等領域也有重要作用[1-2]。目前國外在電子束高速掃描的研究領域上較國內領先,且已達到工程化應用。以德國SST公司所研制的電子束高速掃描裝置為例,該裝置工作頻率可達100 kHz,最大輸出電流±8 A,直流供電電壓160 V[3]。相比國內成熟的電子束焊機上所配備的掃描系統,其頻率基本在10 kHz以內,驅動電流大多小于2 A。因此,研究電子束高速掃描技術,研制一套控制電子束高速掃描的裝置在打破國外技術壟斷,實現高端設備國產化上具有重要現實意義。電子束高速掃描裝置包括信號發生器、高速驅動器及偏轉掃描線圈,其中高速驅動器是核心部件,是影響電子束掃描性能優劣的關鍵因素。由于電子是在磁場中受到洛倫茲力的作用發生偏轉,在洛倫茲力公式中,電子電荷量及電子速度均為定量,從而改變磁感應強度成為改變電子所受洛倫茲力大小的唯一方式。為實現電子高速偏轉掃描,必須要實現掃描線圈中的磁感應強度高速變化。由于掃描線圈等效為電感器,實現其磁感應強度快速變化亦即需要實現電感電流快速變化。因此,要求驅動器能夠處理來自波形發生器的高速變化的電流給定信號,同時需要驅動器主回路中電流能夠高速跟隨給定信號,實現高速變化的電流閉環調節。

文中將根據通用型運放的工作特點、功率晶體管的工作狀態及負載特性,分別設計高速跟隨的輸入級電路、高速動態電流閉環電路及輸出電流能高速響應輸入信號的主回路電路,并通過Cadence進行電路仿真,優化電路參數,最終實現電路在100 kHz下輸出±2 A驅動電流。

1 高速驅動器電路設計

1.1 高速響應輸入級電路設計

高速驅動器的輸入波形信號來自波形發生器。通常該信號不會直接用作閉環調節,一般先經過由運算放大器及電阻電容構成的差分運算放大電路進行阻抗變換、干擾信號處理后,輸入下一級電路中。而采用運算放大器處理高速信號,尤其為高幅值階躍信號時,電路性能顯著受到運放的轉換速率SR制約。在運放的SR較低時,其輸出電壓無法快速通過負反饋電路匹配輸入信號,使得輸出波形失真。采用高速運放,可以有效提高電路的高頻特性。而對于常規運放,由于SR的限制,輸出電壓無法快速改變。因此,文中通過降壓的方式,降低運放輸出電壓值,亦即降低運放增益的方式減小轉換時間。輸入級電路如圖1所示。

圖1 輸入級電路

電路由TL082及電阻電容組成,此處Vin電壓最大幅值為±10 V,經低寄生參數電阻R1,R2組成的分壓電路衰減成±1 V電壓信號,通過R4,R3與TL082形成1∶1負反饋電路,TL082輸出電壓最大幅值為±1 V。TL082的SR為16 V/μs,-1~1 V的理論增長時間為125 ns[4]。

由于電路輸入端接收高速突變信號時,在信號的突變沿處,電路輸出波形將出現超調現象。為有效減小這部分超調產生的波形失真,在電路中加入補償電容C1,圖1所示。U1的7腳通過給C1充電,調整其電壓上升速度,使7腳匹配6腳電壓的動態變化速率,改善輸出波形。將C1取值為10 pF,其與R3的時間常數為100 ns,此參數對電路的上升時間影響不大。

電路輸入端Vin信號先通過R1,R2電阻分壓后進行1∶1反向比例運算,而非直接通過10∶1反向比例運算,原因為若采用10∶1反向比例運算電路,在輸入信號為方波信號,且發生電壓階躍時,輸入信號將通過反饋電阻施加到運放輸出端,使得運放輸出電壓出現尖峰,具體過程將在后續章節的測試波形中進行分析說明。

1.2 高速任意波形閉環調節電路設計

由于驅動器工作于高頻動態過程中,電路的輸入輸出信號均為高速任意波形。在如此快的響應速度下,常規PI調節方式基本無法正常工作,采用PI調節將使電路產生嚴重振蕩現象,輸出波形大幅失真。為有效解決上述問題,實現驅動器輸出電流波形可靠跟隨輸入信號,設計電路如圖2所示。

此閉環調節電路由運算放大器TL082,推挽三極管BC327,BC337,以及二極管、電阻、電容組成。其中,給定信號Ig來自輸入級電路的輸出,Drive_H,Drive_L與主回路中功率晶體管基極相連。閉環調節電路、功率晶體管、負載電流采樣電阻三者構成射極跟隨器,實現電流采樣電阻端電壓強制跟隨于閉環調節電路的輸出值,從而達到負載電流高速可控調節的目的。

圖2 閉環調節電路

閉環電路主體為1∶1反相比例運算電路,由TL082通過R5,R20構成,電路的輸出端采用Q1,Q2組成的推挽電路放大運放輸出能力,當輸入信號Ig的幅值為±1 V,通過Q1,Q2后輸出為等值反向電壓±1 V。將R5,R20設為500 Ω,選擇較低的阻值,一方面可減小其與電容C2的時間常數,提高電路的響應速度,另一方面提高電阻上的功耗,減小噪聲對有效信號產生的干擾。R10,R11,D3,D4構成補償電路,補償Q1與Q2的BE間壓降,二極管選用1N4148,R10,R11阻值為500 Ω,則電阻上流過的電流約8 mA,滿足對Q1與Q2的驅動要求。同理,采用D1,D2的二極管導通壓降補償主電路中TIP41C,TIP42C的BE間導通壓降。通過微調R7與R8的阻值,實現主電路晶體管TIP41C,TIP42C處于臨界導通狀態。R6,R9阻值為100 Ω,在±5 V供電電源的左右下,其上流過約43 mA電流值,滿足主回路中功率晶體管的驅動要求。

驅動信號Drive_H,Drive_L信號分別通過功率晶體管TIP41C與TIP42C的BE施加至電流采樣電阻R12上,形成射極跟隨器,如圖2所示,實現采樣電阻電壓始終反向跟隨運放輸入電壓Ig。通過調節電流采樣電阻端電壓,實現串聯在回路中的線圈電流的實時調節。同時,將閉環電路的輸入輸出信號幅值均控制在±1V以內,有助于TL082響應更快的頻率。

1.3 高速驅動器主回路設計

主回路供電電壓為±50 V,需求的最大負載電流為±2 A。由于主回路需滿足高頻狀態下實現任意電流波形的輸出,而所驅動的目標負載為對電流具有阻礙作用的電感線圈,因此主回路功率晶體管必須工作在放大狀態。為了實現電感電流能夠有效跟隨輸入信號,設計主回路射極跟隨電路,通過強制主回路電流采樣電阻端電壓實時跟隨電流給定信號,實現電感電流按要求進行高速變化。通過這種方式代替常規的PI調節,輸出電流將不易產生超調、波形振蕩現象。考慮到雙極性晶體管在射極跟隨器的設計上更靈活,文中采用TIP41C,TIP42C作為電路的功率調節器件。設計的電路如圖3所示。

圖3 主回路電路

由于電路負載為掃描線圈,等效為電感器,當驅動器輸入信號帶突變特性(如方波)時,在正向信號突變沿,功率晶體管Q3~Q5將快速開通,50 V供電電源快速對負載充電;當負載電流達到目標值時,功率晶體管Q3~Q5內阻增大,電路電流繼而維持穩定。實際上,Q3~Q5存在調節時間,此刻負載在正向電壓的作用下,電流仍將繼續增大,導致負載電流超調,隨后發生波形振蕩。為減小這部分失真,在主回路中加入電阻R15與R16,與電感負載形成RL電路,在響應階躍信號時,負載電流的增長受到回路中電阻R15,R16的制約產生了一定的上升時間,通過調整阻值大小,使上升時間匹配Q3~Q5的調節時間,從而達到負載電流的穩定。另一方面,R15,R16的引入可用于分擔一部分功率晶體管上的電壓,從而減小功率晶體管工作過程中的損耗。受輸出電流最大2 A的制約,R15,R16的阻值不能超過25 Ω,阻值過大將增加電感電流上升時間,過小則無法產生良好的調節效果。經綜合考慮,此處阻值選為5 Ω,可計算得主回路電流從0 A增長至2A的時間增加47 ns,對系統的響應速度影響較小,同時也夠匹配功率晶體管的調節時間。

負載電壓變化是通過功率晶體管的調節實現,進而達到改變負載電流變化率的目的。在高速變化過程中,功率晶體管BE間結電容容易與感性負載形成LC振蕩,影響輸出波形。因此,加入電阻R13,R14,R18,R19,其中R13,R14串聯在驅動電路中限制振蕩電流幅值,其阻值不宜過大,否則將影響閉環控制的效果,此處選擇阻值為10 Ω。R18,R19用于衰減振蕩能量,同時可防止功率晶體管間因干擾信號產生的誤導通,選值為1 K。R17為負載提供可靠的放電回路。各參數的取值將在仿真軟件中進一步驗證。

2 高速驅動器電路仿真

電路仿真是驗證電路功能、優化電路參數、提高電路工作可靠性的有效工具。由于電路中部分器件的非線性特性,在高頻動態下其寄生參數的作用效果明顯,導致采用常規方式計算電路參數將存在一定偏差。文中通過Cadence仿真軟件對驅動器電路進行仿真分析,驗證電路功能并優化參數,進而指導實際驅動器的設計工作。

2.1 高速閉環電路仿真

采用Cadence SPB 16.6對閉環電路進行仿真分析,驗證上述參數下電路的工作特性,并優化各項電路參數[4]。在Design Entry CIS環境下編輯測試電路,通過Pspice A/D模塊對電路進行仿真計算,設定仿真時長為40 μs,每步計算時間為0.01 μs。電壓測試點分為位于Ig,Drive_H及Drive_L處,Ig信號由軟件自帶的電壓源提供。測試波形為方波時,波形參數設為幅值±1 V,周期為10 μs,脈寬為4.95 μs,上升沿下降沿均為0.05 μs;測試波形為正弦波時,波形參數設為幅值±1 V,頻率100 kHz,相位角0°,兩種輸入波形狀態下,電路的仿真波形如圖4所示。圖4中紅色波形為Ig處電壓信號,藍色波形為Drive_H處電壓信號,粉色波形為Drive_L處電壓信號。根據仿真結果分析可知,在輸入波形為上述參數的方波信號時,Drive_H及Drive_L兩處波形與輸入波形之間成反相比例關系,跟隨性較好,其上升沿與下降沿約200 ns,波形失真度很小,無超調量;相較于輸入信號,Drive_H的波形是在原波形基礎上直流偏置約0.8 V,Drive_L波形直流偏置電壓約-0.8 V。當輸入波形為上述正弦波信號時,Drive_H及Drive_L兩處波形與輸入波形之間成反相比例關系,輸出波形失真度很小,可以很好的反映輸入波形的狀態變化。仿真結果表明,所設計的閉環電路能有效響應100 kHz的高速信號。

圖4 驅動電路仿真波形動波

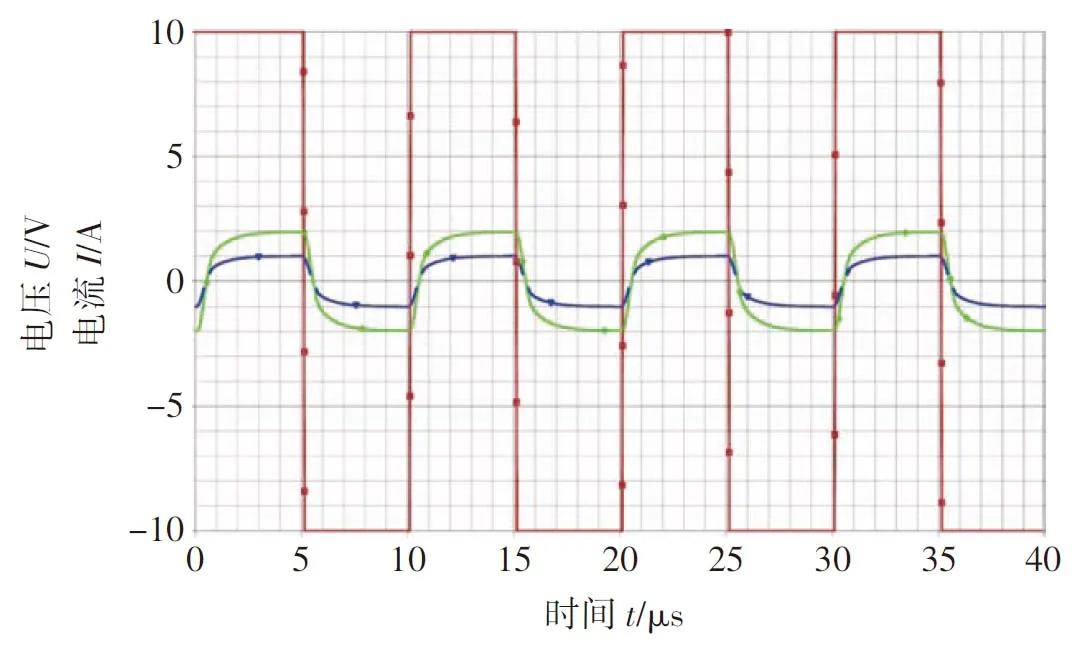

2.2 高速驅動器仿真

對驅動器整體電路進行仿真,在Design Entry CIS環境下編輯輸入級電路、閉環電路及主回路電路,通過Pspice A/D模塊對其進行仿真,設定仿真時長為40 μs,每步計算時間為0.01 μs。驅動器輸入波形為方波,其參數為幅值±10 V,脈寬4.95 μs,上升沿與下降沿0.05μs,周期10 μs,頻率100 kHz。測量輸入波形,采樣電阻端電壓,電感電流波形如圖5所示。圖5中紅色波形為輸入信號,藍色波形為電流采樣電阻端電壓,綠色波形為電感電流。可以看到,在輸入為±10 V方波信號時,采樣電阻電壓與電流波形的一致性較好。按幅值10%~90%的時間計算上升沿與下降沿,兩者波形的上升沿與下降沿約為1.8 μs,采樣電阻穩定時的端電壓為±1 V,對應電感電流為±2 A。根據仿真結果可知,所設計的驅動器能夠在100 kHz下有效輸出,且波形失真度小。

圖5 驅動器仿真波形

3 高速驅動器研制與性能驗證

采用上述電路結構與參數研制出了電子束掃描線圈高速驅動器,并分別對輸入級電路、高速閉環電路以及驅動器主回路進行性能測試與對比驗證。

3.1 輸入級電路波形測試與分析

輸入級電路如圖1所示,采用函數發生器AFG3022在圖1中Vin與0 V處施加100 kHz,幅值為±10 V,50%占空比的方波信號,并通過示波器TPS2024測試輸出端波形如圖6所示。圖6a與圖6b中同一通道對應的測試點為同一點,其中通道1為函數發生器輸出波形,通道2為圖1所示電路運放7腳的輸出波形,通道3為直接采用10∶1反向比例運算電路時運放7腳的輸出波形,即將圖1中R1短路,R2,C1斷路,R4改為1K時,運放的輸出波形,通道4為反向1∶1運算電路運放7腳的輸出波形,亦即將圖1中R1短路,R2,C1斷路時,運放的輸出波形。對比四個通道的波形可以看出,通道4因為運放直接采用1∶1反向比例運算電路對輸入信號進行處理,因此其輸出電壓從-10 V上升至10 V所需的時間達到了1.14 μs,且出現一定量的超調;而通道2和3的電壓上升時間很短,特別是通道3的上升時間僅116.9 ns,但產生的尖峰電壓比較大。其原因分析為:通道1高電平時,電流由Vin通過R3,R4流向運放7腳;當通道1由高電平跳變為低電平時,運放輸出電壓不能立即發生改變,但電流卻變成由運放7腳經R4,R3流向Vin,R4端電壓反向,疊加在7腳上,導致7腳出現電壓尖峰。采用圖1所示電路將Vin先進行分壓后再1∶1反向比例運算,可大幅減小這部分電壓疊加量,同時由于補償電容C1的引入,改善了電路的充放電特性,有效減小的運放輸出波形的尖峰值,但輸出波形的上升與下降時間將適當變長,如圖6中通道2波形所示,為258.7 ns,但仍在接受范圍內。

圖6 輸入級電路測試波形圖

因此,采用分壓、補償及反向比例運算的方式有效的提高了通用型運放對高速信號的處理速度,使得輸入級電路能快速響應高頻輸入信號。

3.2 高速閉環電路波形測試與對比分析

對圖2所示電路進行測試,測試工具包括泰克函數發生器AFG3022一臺,泰克TPS2024示波器一臺,P2220示波器探頭三根。函數發生器產生波形信號輸入至Ig處,波形參數為與仿真參數一致的方波與正弦波,分別通過示波器測量Ig,Drive_H及Drive_L處電壓波形并進行分析。所測波形如圖7所示。圖7中通道1為Ig波形,通道2為Drive_H波形,通道3為Drive_L波形。由圖可知,測試波形與仿真結果較為接近,輸入波形為方波時,驅動波形的上升時間為280 ns,兩者的跟隨性較好;輸入波形為正弦波時,輸入波形與Drive_H及Drive_L輸出波形的直流偏置電壓分別為0.6 V與-0.6 V,波形跟隨性良好。可見,閉環電路能夠滿足100 kHz的工作要求。

圖7 驅動電路測試波形

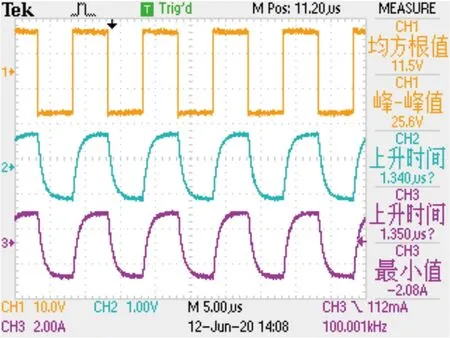

3.3 高速驅動器特性測試與驗證

將驅動器輸出端接至電感量為10 μH的掃描線圈兩端,電路的輸入端接收±10 V的100 kHz方波信號,通過示波器測量輸入波形,電流采樣電阻端電壓以及電感電流波形,所得結果如圖8所示。圖8中通道1為

圖8 驅動器實際輸出波形

輸入信號,通道2為采樣電阻端電壓,通道3為負載電流波形。可以看到,在輸入信號為±10 V的方波信號時,采樣電阻電壓波形與電感電流波形一致性較好,電流采樣電阻端電壓正向幅值為1.03 V,負向幅值為-1.06 V,上升時間為1.34 μs,較仿真波形的上升時間短;負載電流正向幅值為2.02 A,達到設計值2 A的101%,負向幅值為-2.08 A,達到設計值的104%,電流上升時間為1.35 μs。

受負載供電電源電壓與負載電感量的制約,50 V供電電壓下10 μH電感的電流在±2 A間進行躍變的極限時間為800 ns。更好的電流波形意味著更高的線圈供電電壓;而供電電壓的上升,使主回路電流上升沿變得更陡的同時,也使得電路自身的電磁干擾變得很大,且功率器件的損耗也呈指數級增長,這將對電路的設計及優化提出新的挑戰。

而在實際的電子束設備中,控制電子束掃描使其在兩點或者多點間跳躍時,在1.35 μs跳躍時間內,電子束能量釋放在跳躍路徑上的平均線能量相對于3.65 μs定點停留時間下產生的能量而言,其實所占比重并不大。因此,上述負載電流波形可以滿足電子束在100 kHz下進行高速掃描。

分別在背散射電子成像系統及電子束高速圖像掃描系統中驗證高速驅動器的實際掃描效果,獲得圖9所示的掃描圖像。圖9為背散射電子成像系統對零件實時觀測的效果圖,圖10為控制電子束在金屬板件掃進行高速圖像掃描的效果圖,可見兩者圖案紋理清晰,電子束掃描效果較好。

上述測試結果表明,所研制的電子束掃描線圈高速驅動器可快速精確的控制電子束進行高速偏轉掃描,滿足設計要求。

圖9 背散射電子成像

圖10 電子束高速圖像掃描

4 結論

(1)采用分壓、補償及反向比例運算的方式設計高速響應差分輸入電路,實現通用運放能快速有效的響應高速電壓信號。

(2)通過射極跟隨的方式設計驅動器電流閉環電路,強制主回路電流高速跟隨輸入信號。

(3)通過Cadence仿真軟件進行驅動器電路功能驗證與參數優化,實現驅動器電路與負載特性匹配。

(4)根據電路設計與仿真結果,研制了電子束掃描線圈高速驅動器,并對其進行測試分析。結果表明,該驅動器驅動電感值為10 μH的掃描線圈時,輸出電流波形能在100 kHz高頻下可靠跟隨輸入信號,正向最大電流2.02 A,負向電流最大-2.08 A,滿足設計要求。