基于FPGA的人臉識(shí)別系統(tǒng)實(shí)驗(yàn)設(shè)計(jì)

韓力英 寧欣波

摘?要:隨著科技的快速發(fā)展,人臉識(shí)別技術(shù)逐漸進(jìn)入了人們的生活中,成為了生活中密不可分的一部分。FPGA不僅能夠進(jìn)行數(shù)字系統(tǒng)設(shè)計(jì),在人工智能領(lǐng)域也嶄露頭角。電子信息類(lèi)本科生的實(shí)驗(yàn)安排也必須跟上人才培養(yǎng)的需求、時(shí)代的步伐,為此,開(kāi)發(fā)了基于FPGA的人臉識(shí)別系統(tǒng)實(shí)驗(yàn)設(shè)計(jì)。該設(shè)計(jì)使用PYNQ實(shí)驗(yàn)板,利用Vivado?HLS高級(jí)綜合工具搭建電路系統(tǒng),用python調(diào)用設(shè)計(jì)的電路建立卷積神經(jīng)網(wǎng)絡(luò)模型并訓(xùn)練神經(jīng)網(wǎng)絡(luò),實(shí)現(xiàn)人臉識(shí)別技術(shù),進(jìn)一步加強(qiáng)學(xué)生學(xué)習(xí)EDA技術(shù)的意識(shí)。

關(guān)鍵詞:人臉識(shí)別;卷積神經(jīng)網(wǎng)絡(luò);PYNQ

中圖分類(lèi)號(hào):G642??文獻(xiàn)標(biāo)識(shí)碼:B

眾所周知,我國(guó)集成電路領(lǐng)域人才缺口巨大,EDA技術(shù)是集成電路設(shè)計(jì)的核心。因此,EDA技術(shù)的發(fā)展才是集成電路卡脖子問(wèn)題的關(guān)鍵所在。

隨著人工智能以及機(jī)器學(xué)習(xí)、深度學(xué)習(xí)的快速發(fā)展,電子信息類(lèi)本科學(xué)生的課程在不斷地與時(shí)俱進(jìn),傳統(tǒng)的實(shí)驗(yàn)設(shè)計(jì)已經(jīng)不適合人才培養(yǎng)的需求,開(kāi)發(fā)新的能夠反映現(xiàn)代前沿信息技術(shù)的實(shí)驗(yàn)設(shè)計(jì)勢(shì)在必行。對(duì)于公共場(chǎng)所,無(wú)接觸識(shí)別生物特征識(shí)別系統(tǒng)開(kāi)始成為確認(rèn)用戶身份的重要方式,其中人臉識(shí)別具有使用方便、識(shí)別更準(zhǔn)確等優(yōu)勢(shì),廣受用戶喜歡[1]。

本實(shí)驗(yàn)設(shè)計(jì)就是基于Xlinx公司的PYNQ開(kāi)發(fā)板,采用Vivado?HLS高級(jí)綜合工具利用硬件資源搭建電路系統(tǒng),用python調(diào)用設(shè)計(jì)的電路建立卷積神經(jīng)網(wǎng)絡(luò)模型并訓(xùn)練神經(jīng)網(wǎng)絡(luò),實(shí)現(xiàn)人臉識(shí)別技術(shù),進(jìn)一步加強(qiáng)學(xué)生學(xué)習(xí)EDA技術(shù)的興趣,激發(fā)學(xué)生解決我國(guó)集成電路領(lǐng)域卡脖子技術(shù)的熱情,培養(yǎng)學(xué)生的大國(guó)工匠精神。

1?系統(tǒng)整體框架

盡管在不同的應(yīng)用環(huán)境下,人臉識(shí)別系統(tǒng)的結(jié)構(gòu)也有所不同,但大部分的人臉識(shí)別系統(tǒng)結(jié)構(gòu)都包括人臉采集和檢測(cè)部分、圖像預(yù)處理部分、特征提取部分和人臉識(shí)別部分。人臉圖像被輸入系統(tǒng)后,將進(jìn)行人臉檢測(cè)和人臉對(duì)齊,然后用特征提取器提取特征,系統(tǒng)再將提取的特征與圖庫(kù)人臉進(jìn)行比較,進(jìn)行人臉匹配。

人臉圖像采集和檢測(cè)是根據(jù)人臉圖像的模式特征,在采集到的圖片中對(duì)人臉?biāo)趨^(qū)域進(jìn)行數(shù)據(jù)提取。

人臉圖像預(yù)處理的目的主要是消除各種干擾,為后續(xù)人臉識(shí)別準(zhǔn)確性做準(zhǔn)備。人臉圖像特征提取是提取包括口、鼻、眼等特征,主要是根據(jù)位置構(gòu)成的幾何結(jié)構(gòu)等,以作為人臉圖像特征數(shù)據(jù)。人臉圖像識(shí)別就是通過(guò)提取一個(gè)人臉圖像的特征數(shù)據(jù)。當(dāng)提取到特征數(shù)據(jù)與某個(gè)模板相似度超過(guò)了設(shè)定的概率時(shí),則認(rèn)為這個(gè)特征匹配成功,否則匹配失敗,同時(shí)輸出一個(gè)特征匹配結(jié)果。

2?硬件設(shè)計(jì)

在卷積神經(jīng)網(wǎng)絡(luò)中,大量的計(jì)算是卷積的計(jì)算,F(xiàn)PGA的計(jì)算速度要比軟件計(jì)算速度快,這也是為什么FPGA能夠用于人工智能領(lǐng)域的原因,模型中所有的卷積計(jì)算和池化部分通過(guò)FPGA器件實(shí)現(xiàn),這樣可以使計(jì)算速度更快。

PL端的設(shè)計(jì)首先使用Vivado?HLS軟件實(shí)現(xiàn)卷積計(jì)算,然后將一些變量分別設(shè)置為輸入和輸出端口,在HLS軟件中通過(guò)pipeline和unroll等方法進(jìn)行優(yōu)化設(shè)計(jì),通過(guò)軟件綜合后查看硬件資源的使用量以及時(shí)序約束等情況,最后利用此高層次綜合工具生成IP核。當(dāng)使用unrolling方法進(jìn)行優(yōu)化時(shí),折疊的for循環(huán)被展開(kāi),相當(dāng)于電路被復(fù)制成需要的數(shù)量,假如使用N個(gè)相同電路,則只需要一步計(jì)算就完成,這就是為什么FPGA可以作為硬件加速器。如圖1中,一個(gè)循環(huán)次數(shù)為6的for循環(huán),當(dāng)使用unrolling將其分為3個(gè)for循環(huán)后,原來(lái)需要6步完成的計(jì)算只需要2步就可以了。

幾乎所有的優(yōu)化方法都是以增大硬件資源開(kāi)銷(xiāo)來(lái)達(dá)到提高計(jì)算效率的目的。沒(méi)有進(jìn)行優(yōu)化前使用的硬件資源(solution1)遠(yuǎn)低于使用unroll優(yōu)化(solution2)后使用的硬件資源數(shù)量。隨著集成電路制造工藝的發(fā)展,在單片F(xiàn)PGA上已經(jīng)能夠集成大量的硬件資源,所以在硬件上進(jìn)行加速設(shè)計(jì)已經(jīng)完全可行。可以通過(guò)同樣的步驟做最大池化IP核,如圖2所示。

設(shè)計(jì)好IP核之后就可以通過(guò)Vivado中的Block?Design進(jìn)行整體的電路設(shè)計(jì)。將設(shè)計(jì)好的電路通過(guò)軟件生成bit文件和tcl文件,再將bit文件、tcl文件和hwh文件改為相同的文件名,放到PYNQZ2的文件夾中即可使用。

3?軟件設(shè)計(jì)

LFW人臉數(shù)據(jù)庫(kù)[5]是設(shè)計(jì)用于人臉識(shí)別問(wèn)題的人臉照片數(shù)據(jù)庫(kù)。這個(gè)數(shù)據(jù)庫(kù)里面的圖像是RGB彩色圖像。本實(shí)驗(yàn)設(shè)計(jì)可以使用LFW人臉數(shù)據(jù)庫(kù),也可以采集自己、同學(xué)等人臉照片進(jìn)行識(shí)別訓(xùn)練。由于數(shù)據(jù)集不只是包含人臉數(shù)據(jù),還包括身體等很多背景,所以需要對(duì)數(shù)據(jù)集中的圖像進(jìn)行篩選,首先提取出人臉部分,再進(jìn)行隨機(jī)旋轉(zhuǎn)、翻轉(zhuǎn)等幾何變換,以增大訓(xùn)練集。現(xiàn)在流行的卷積神經(jīng)網(wǎng)絡(luò)算法如圖3所示。

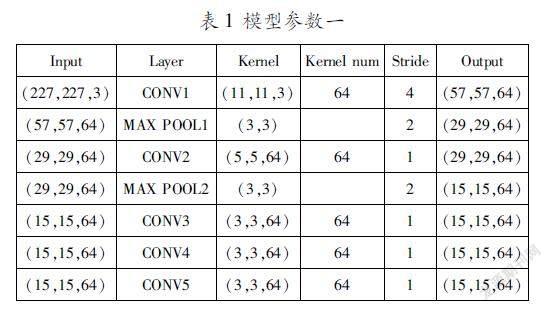

學(xué)生可以選擇AlexNet網(wǎng)絡(luò)模型,注意網(wǎng)絡(luò)參數(shù)數(shù)量要適應(yīng)PYNQZ2的內(nèi)存空間大小。例如表1模型參數(shù)雖然可以滿足訓(xùn)練要求,但是在移植到PYNQZ2開(kāi)發(fā)板上時(shí),由于參數(shù)數(shù)量太多,開(kāi)發(fā)板的緩存根本裝不下,但是在AlexNet模型上刪減使用的卷積核數(shù)量,又會(huì)使訓(xùn)練效果不理想,準(zhǔn)確率低,所以大家要考慮如何選擇模型參數(shù)。例如可以降低最后一層的輸出種類(lèi)數(shù),即將人臉識(shí)別的結(jié)果分為正確和錯(cuò)誤兩種,可以使正確率大大增加。如圖4所示,是以LFW數(shù)據(jù)集作為訓(xùn)練集、訓(xùn)練的結(jié)果。

從圖4中可以看出,隨著訓(xùn)練次數(shù)的增加準(zhǔn)確率在逐漸增加,采用二值結(jié)果,最后訓(xùn)練得到的模型準(zhǔn)確率可達(dá)97%以上。但由于卷積核的數(shù)量越多,計(jì)算量就越大,相應(yīng)的程序運(yùn)行時(shí)間就越長(zhǎng),可以通過(guò)降低卷積核的數(shù)量來(lái)提高運(yùn)行速度。表2是降低卷積核數(shù)量后的模型參數(shù)。

按照表2參數(shù)訓(xùn)練情況如圖5所示,在圖中可以看到訓(xùn)練的準(zhǔn)確率在訓(xùn)練的第15次就穩(wěn)定在了98%以上,盡管訓(xùn)練時(shí)間有所延長(zhǎng),但程序運(yùn)行時(shí)間僅為按照表1參數(shù)的七分之一。

隨著參數(shù)的降低,程序需要運(yùn)行的時(shí)間雖然大幅度減少,但是訓(xùn)練所需要的時(shí)間也成倍增加,訓(xùn)練的準(zhǔn)確率有所降低。要求學(xué)生綜合訓(xùn)練時(shí)間、程序運(yùn)行時(shí)間、準(zhǔn)確率三方面因素,選擇合適的模型參數(shù)進(jìn)行訓(xùn)練和測(cè)試。

4?系統(tǒng)測(cè)試

可以在程序中設(shè)定檢測(cè)到非人臉圖片時(shí),提示不是人臉,跳過(guò)人臉識(shí)別步驟,直接輸出結(jié)果,不是人臉,結(jié)束識(shí)別任務(wù)。

可以針對(duì)所給出的前三種訓(xùn)練的模型進(jìn)行人臉識(shí)別測(cè)試,當(dāng)然也可以自己重新修改模型參數(shù),找到最優(yōu)模型。對(duì)比在什么情況下,識(shí)別效果最好。下面僅給出使用模型參數(shù)一對(duì)數(shù)據(jù)庫(kù)中一幅圖片進(jìn)行識(shí)別的結(jié)果,要求學(xué)生自己進(jìn)行其他圖像或者自拍照片進(jìn)行人臉識(shí)別。

結(jié)論

本實(shí)驗(yàn)設(shè)計(jì)采用協(xié)同異構(gòu)的方法,在PYNQ上利用FPGA設(shè)計(jì)卷積IP核和池化IP核等硬件電路,利用開(kāi)發(fā)板中的ARM部分調(diào)用硬件電路逐層搭建卷積神經(jīng)網(wǎng)絡(luò),最終實(shí)現(xiàn)人臉識(shí)別設(shè)計(jì),使學(xué)生對(duì)FPGA的認(rèn)識(shí)從數(shù)字系統(tǒng)設(shè)計(jì)轉(zhuǎn)變到人工智能領(lǐng)域設(shè)計(jì)。

參考文獻(xiàn):

[1]李霖潮.淺析人臉識(shí)別技術(shù)的發(fā)展[J].新型工業(yè)化,2020,10(03):129133.

[2]HSIAO?J?HW,COTTRELL?G.Two?fixations?suffice?in?face?recognition[J].Psychological?science,2008,19(10):9981006.

[3]CHANDRA?S?R,PATWARDHAN?K,PAI?A?R.Problems?of?Face?Recognition?in?Patients?with?Behavioral?Variant?Frontotemporal?Dementia[J].Indian?journal?of?psychological?medicine,2017,39(5):653658.

[4]SUN?C?C,AHAMAD?A,LIU?P?H.SoC?FPGA?Accelerated?SubOptimized?Binary?Fully?Convolutional?Neural?Network?for?Robotic?Floor?Region?Segmentation[J].Sensors,2020,20(21),6133:117.

[5]YANG?Y?X,WEN?C,XIE?K,et?al.Face?Recognition?Using?the?SRCNN?Model[J].Sensors,2018,18(12),4237:124.

基金項(xiàng)目:河北省高校教學(xué)改革項(xiàng)目“產(chǎn)學(xué)合作、協(xié)同育人背景下電子信息類(lèi)創(chuàng)新實(shí)踐課程的改革研究與實(shí)現(xiàn)”(2020GJJG033),河北省新工科教學(xué)改革項(xiàng)目“面向新工科建設(shè),改革電子信息類(lèi)實(shí)踐教學(xué)模式,培養(yǎng)新型工科人才”(2020GJXGK055)

作者簡(jiǎn)介:韓力英(1977—?),女,博士,副教授,主要從事數(shù)字電子技術(shù)、EDA技術(shù)、DSP技術(shù)等相關(guān)課程的教學(xué)工作以及醫(yī)學(xué)圖像處理研究。