原子級控制的約瑟夫森結中Al2O3 勢壘層制備工藝

李中祥 王淑亞 黃自強 王晨 穆清?

1)(鄭州大學國家超級計算鄭州中心,鄭州 450001)

2)(數學工程與先進計算國家重點實驗室,鄭州 450001)

3)(鄭州大學計算機與人工智能學院,鄭州 450001)

4)(復旦大學微電子學院,上海 200433)

5)(上海集成電路制造創新中心,上海 200433)

傳統熱氧化方式制備約瑟夫森結中AlOX 勢壘層是將高純度氧氣擴散到Al 表面進行,但該方式制備的勢壘層氧化不完全,厚度難以精準控制.本文采用原子層沉積方式在金屬Ti 表面逐層生長Al2O3 勢壘層,并制備出三明治結構的Ti/Al2O3/Ti 約瑟夫森結.通過調節Al2O3 勢壘層的沉積厚度和約瑟夫森結的面積研究了其相應的微觀結構及電學性質.實驗結果表明,原子層沉積方式生長的單層Al2O3 薄膜厚度約為1.17 ?(1 ?=10-10 m),達到原子級控制勢壘層厚度,通過調節勢壘層厚度實現了對結室溫電阻值的控制,并通過優化結面積獲得了室溫電阻均勻性良好的約瑟夫森結.

1 引言

作為超導量子電路中唯一的無損耗非線性元件[1],約瑟夫森結通常是一種超導體-絕緣體-超導體結構的超導隧道結,其工作原理是基于極低溫下由電子形成的庫珀對的隧穿效應.由于半導體工業的兼容性,約瑟夫森結是實現超導量子比特的重要方式之一,中間超薄絕緣體構成的勢壘層是實現兩側超導電極相干性的關鍵所在[2].在材料選擇上,由于Al 的氧化物質地堅固,鈍化性能好且適合庫珀對的隧穿,一般采用Al 的氧化物作為約瑟夫森結的勢壘層[3,4].目前,通常采用原位熱氧化方式將氧氣擴散到Al 表面制備AlOX勢壘層[5],但該反應是自限制的,形成的AlOX薄膜會阻礙氧原子擴散到下方的Al 表面,隨著反應時間增加,AlOX薄膜逐漸變厚,最終將徹底阻擋氧原子,使其無法擴散至Al 表面,從而達到生長極限厚度[6].同時,由于氧分壓難以精確控制等問題,熱氧化工藝難以制備出均勻且厚度精準控制的勢壘層.此外采用熱氧化方式制備的AlOX勢壘層(其化學計量是不確定的,一般利用退火工藝將AlOX轉變為質量較高的Al2O3[7]),存在例如氧空位等缺陷會引起量子電路中的兩能級漲落,這也是造成量子比特退相干的主要原因[8].想要進一步提高退相干時間,關鍵在于提升勢壘層質量,所以使用一種新的勢壘層生長方式制備約瑟夫森結勢在必行.

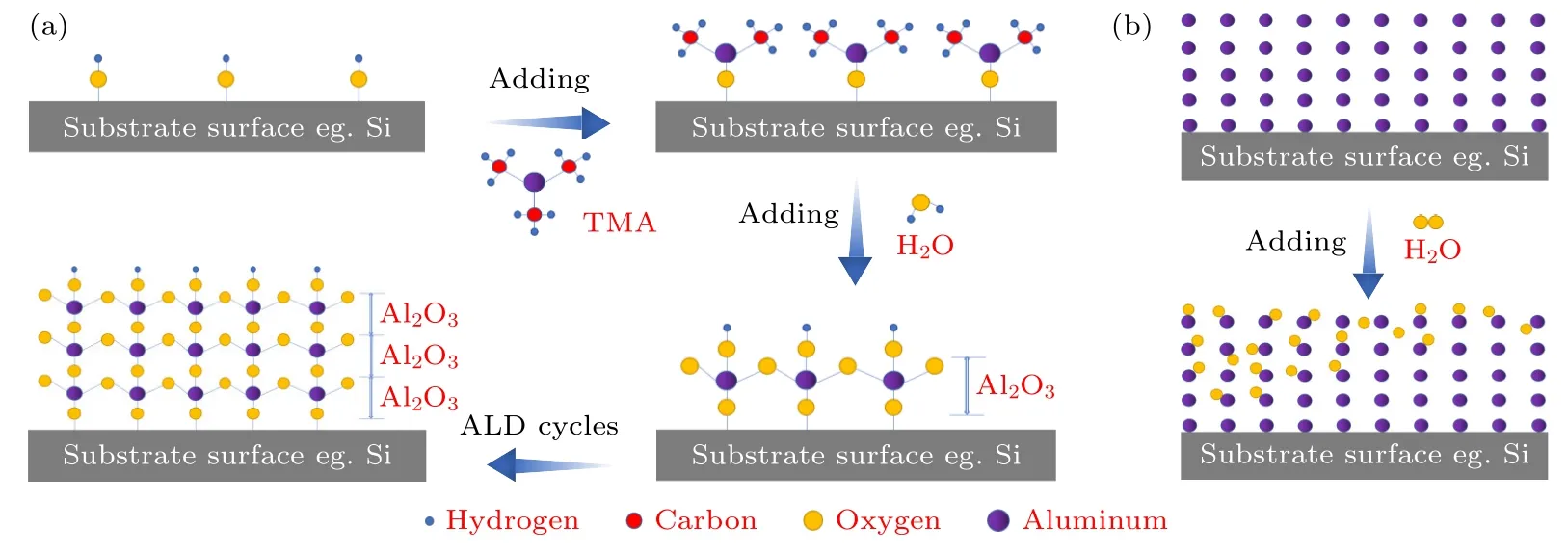

原子層沉積(atomic layer deposition,ALD)是一種化學沉積過程,能夠滿足連續、自限制表面反應的原子層控制和共形沉積的需要[9],自限制表面反應限制外界原子向薄膜下方擴散,從而在薄膜上方不斷堆積,每個循環生長一層原子薄膜.如圖1(a)所示,ALD 生長Al2O3發生在水和三甲基鋁(trimethylaluminium,TMA)交替暴露的過程中,這一過程可以描述為[10-12]

圖1 ALD 與熱氧化方式生長氧化鋁勢壘層的過程示意圖(a)ALD 生長Al2O3 的過程;(b)熱氧化方式生長AlOX 的過程Fig.1.Schematic diagram of the process of growing aluminum oxide layer by ALD and thermal oxidation:(a)Process of growing Al2O3 by ALD;(b)process of growing AlOX by thermal oxidation.

其中,帶*號表示表面物質.襯底可選用硅(Si)或者一些金屬,因其表面比較容易羥基化.TMA(Al(CH3)3)與表面羥基(OH-)反應,會在表面沉積一層Al(CH3)2,之后通入惰性氣體引入水,水在表面反應物上又再次羥基化,形成一個完整的ALD循環,生長一層Al2O3薄膜.重復這一過程可以獲得連續、均勻、無孔的高質量Al2O3薄膜[13],制備出的薄膜兩能級缺陷密度較低[14].然而,熱氧化(圖1(b))是通過氧氣從Al 表面向下擴散形成氧梯度生長AlOX隧道勢壘層,可控性較差.因此ALD通過逐層向上生長的方式制備Al2O3隧道勢壘層具有顯著優勢.在上述研究背景下,本文對ALD方式生長的Al2O3隧道勢壘層及制備出的相應Ti/Al2O3/Ti約瑟夫森結進行了探索和研究,利用ALD 生長Al2O3薄膜的各項優點,通過剝離工藝制備出了多組勢壘層厚度不同、結區面積不同的Ti/Al2O3/Ti約瑟夫森結,并對其斷面微觀結構以及電學性質進行了測量研究.

2 實驗

2.1 約瑟夫森結制備

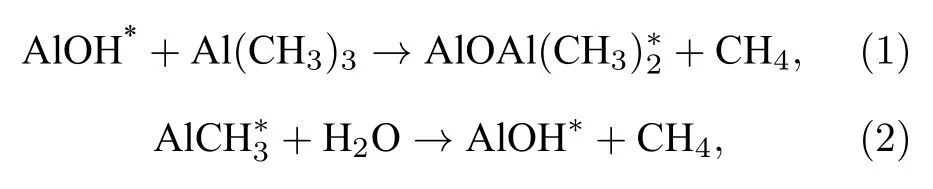

首先,沉積底電極.在Si 襯底上旋涂光刻膠,利用光刻技術定義出底層金屬圖形,然后采用磁控濺射方式以0.28 nm/s 的速率沉積Ti 金屬薄膜(圖2(a)),之后使用剝離工藝將圖形轉移到金屬層,形成底電極.隨后,開始制備勢壘層.由于樣品在剝離工藝結束后在轉移過程中會接觸空氣,底電極表面不可避免會形成一層自然氧化層(圖2(b)).使用基于氦氫混合氣體(95%He∶5%H2)的反應預清潔(reactive pre-clean,RPC)技術去除底電極表面自然氧化層[15](圖2(c)),并在真空(9.9×10-6Torr,1 Torr=1.33×102Pa)中原位傳輸樣品到薄膜生長腔室.在進行ALD 反應之前,由于腔室溫度較高,一般將樣品在腔室內預熱5 min,有利于襯底表面羥基化,使反應更加順利.采用ALD方式在底電極表面生長Al2O3勢壘層(圖2(d)),腔室溫度為300 ℃,每次循環通入0.5 s 的水,氮氣吹掃反應殘余物9 s,接著通入TMA 0.5 s,氮氣吹掃反應殘余物5 s.最后,沉積頂電極.頂電極定義方式和沉積方式(圖2(e))與底電極相同,剝離后,頂電極與底電極金屬線條垂直相交形成完整的約瑟夫森結(圖2(f)).其中,約瑟夫森結的面積固定為44 μm×44 μm,在該結面積下分別生長12,15,20,25 個循環的勢壘層,制備出4 組不同勢壘層厚度的約瑟夫森結,底部與頂部的Ti 電極厚度均為100 nm.此外,將勢壘層ALD 循環次數固定為12 次循環,在相同勢壘層厚度下,分別制備0.04,0.09,0.25,0.49,1.00 μm2等5 組不同面積的約瑟夫森結,頂部與底部的Ti 電極厚度均為30 nm.

圖2 約瑟夫森結制備過程示意圖(a)光刻后第一次濺射Ti 示意圖;(b)光刻膠剝離后,Ti 金屬電極表面立即形成自然氧化層;(c)使用RPC 技術利用活性氫去除氧化層;(d)去除自然氧化層后原位ALD 生長Al2O3;(e)第二次光刻確定頂電極圖案,并進行第二次濺射Ti;(f)金屬剝離形成完整的結Fig.2.Schematic diagram of Josephson junction preparation process:(a)Schematic diagram of the first sputtered Ti after photolithography;(b)natural oxide layer formed on the Ti metal electrode surface immediately after lift-off process;(c)removal of the oxide layer using the RPC technique by reactive hydrogen;(d)in situ ALD growth of Al2O3 after removal of the natural oxide layer;(e)the second photolithography to determine the top electrode pattern and sputtered Ti again;(f)lift-off process to complete the junction.

2.2 約瑟夫森結的表征測試

利用透射電子顯微鏡(transmission electron microscope,TEM)對約瑟夫森結中Al2O3隧道勢壘層的厚度進行表征.利用擁有0.5 μm 鉑探針的多點接口(multi point interface,MPI)探針臺以及是德科技(Keysight)4200 參數分析儀測量約瑟夫森結室溫下的電流-電壓(I-V)曲線,并從I-V曲線的斜率中提取室溫電阻(Rn).安倍戈卡-巴拉托夫(Ambegaokar-Baratof)公式[16]預測隧道電阻,即室溫電阻和結面積(A)的乘積,與其臨界電流密度(JC)成反比:

其中Δ為超導能隙,e是元電荷.為實驗測量室溫電阻判斷參數是否符合要求提供了依據[17,18].此外,約瑟夫森結室溫電阻值的波動會受到結區面積變化的影響[19,20],不同結面積的約瑟夫森結的室溫電阻值波動程度不同.

3 結果分析與討論

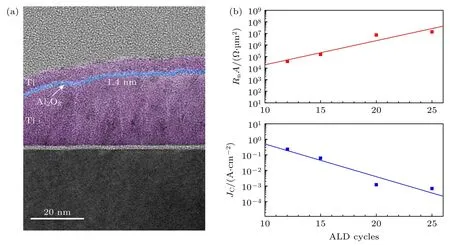

為了研究ALD 逐層生長Al2O3勢壘層的效果,我們使用TEM 對勢壘層斷面微觀結構進行了測量表征.圖3(a)顯示了勢壘層厚度為12 次循環(12 層Al2O3薄膜)的Ti/Al2O3/Ti 約瑟夫森結斷面結構.測量得到的Al2O3勢壘層厚度為1.4 nm,則單層 Al2O3薄膜厚度約為1.17 ?(1 ?=10-10m),說明使用ALD 工藝通過控制循環的次數,可以實現對Al2O3勢壘層厚度的原子級控制.

接下來測量了不同勢壘層厚度下約瑟夫森結的室溫電阻,來探究勢壘層厚度與室溫電阻之間的關系,見圖3(b).結面積固定為44 μm×44 μm,勢壘層厚度的變化通過ALD 循環次數來控制.對不同勢壘層厚度下約瑟夫森結的室溫電阻進行了多次測量,并統計其平均值.當勢壘層厚度大于12 次循環時,隨循環次數增加,室溫電阻值呈指數變化增長,RnA變化范圍約為104-108Ω·μm2,說明室溫電阻值與勢壘層厚度呈指數關系.根據測量得到的電阻值以及(3)式,在Ti 的超導臨界轉變溫度0.4 K 下計算得到臨界電流密度JC與ALD循環次數之間的關系.隨著循環次數增加,臨界電流密度JC呈指數下降,其變化范圍約為10-4-100A/cm2.這些結果表明可以通過調節循環次數,實現原子級控制勢壘層厚度,從而精準地控制室溫電阻值,得到所需的臨界電流密度.

圖3 (a)勢壘層厚度為12 層Al2O3 薄膜的約瑟夫森結斷面結構TEM 圖像;(b)隧道電阻RnA,計算得到的JC 與ALD 循環次數的關系Fig.3.(a)TEM image of Josephson junction cross-sectional structure with Al2O3 tunnel barrier’s thickness is 12 layers;(b)relationship between the tunnel resistance RnA,the calculated JC and the ALD cycles.

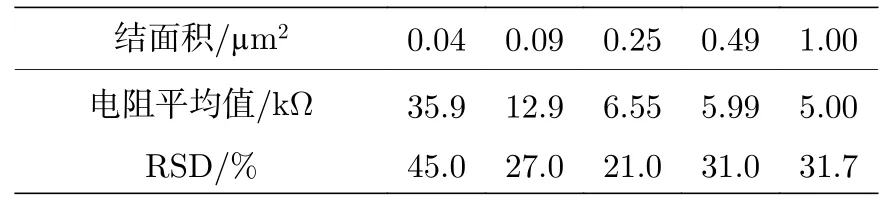

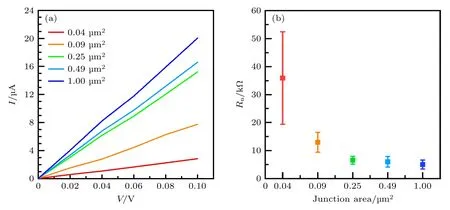

為了探究ALD 方式制備的約瑟夫森結室溫電阻均勻性問題,在勢壘層厚度為12 次循環(12 層Al2O3薄膜)下,制備了5 組Ti/Al2O3/Ti約瑟夫森結,其結面積大小分別為0.04,0.09,0.25,0.49,1.00 μm2.通過測量其室溫電阻值并采用相對標準偏差(relative standard deviation,RSD)的方式來計算其均勻性.圖4 顯示了不同結面積下約瑟夫森結的典型I-V曲線以及電阻均勻性與結面積之間的關系,具體測量值見表1.

表1 不同結面積的約瑟夫森結室溫電阻比較Table 1. Comparison of room temperature resistance of Josephson junctions with different areas.

圖4 不同結面積下約瑟夫森結的室溫電阻測量結果以及其均勻性數據圖(a)室溫下測量的不同結面積下約瑟夫森結的I-V曲線;(b)結面積與電阻值之間的關系(圖中點表示測量電阻的平均值,Y 誤差棒使用標準差計算)Fig.4.Room temperature resistance measurements of Josephson junctions at different junction areas and their uniformity data plotted:(a)I-V curves of Josephson junctions at different junction areas measured at room temperature;(b)relationship between junction areas and resistance values(The dots in the graphs indicate the mean values of the measured resistances,and the Y error bars are calculated using the standard deviation).

約瑟夫森結的電阻值與結面積成反比,結面積越小,其電阻值越大.此外,器件尺寸越小,對制備工藝的要求越高,結面積越小的約瑟夫森結在制備過程中越難以控制參數,因此會導致其電阻值的RSD 偏大.通過約瑟夫森結面積的優化以及電阻均勻性的對比,在結面積為0.25 μm2時獲得了均勻性較好的室溫電阻值,其RSD 為21%,該結論可為將來批量制備約瑟夫森結以及可擴展的量子芯片提供參考.

4 結論

采用原子層沉積Al2O3薄膜制備技術和剝離工藝,以Al2O3薄膜作為勢壘層在Si 襯底制備了三明治結構的Ti/Al2O3/Ti 約瑟夫森結,并對制備約瑟夫森結的微觀結構以及室溫條件下的電學性質測試進行研究.實驗結果表明,單層Al2O3薄膜厚度約為1.17 ?,達到了原子級控制.隨著ALD循環次數增加,Rn呈指數增長(循環次數變化范圍為12-25 時,其對應電阻變化范圍約為104-108Ω·μm2),因此可通過調節ALD 循環次數來控制勢壘層厚度,進而實現對室溫電阻的調控.此外,通過優化約瑟夫森結面積,在結面積為0.25 μm2時獲得了RSD 為21%的均勻性較好的室溫電阻.后續工作中,我們將持續優化ALD 生長Al2O3薄膜的條件,并通過多樣化基底材料與多樣化勢壘層生長工藝相結合的探索,為實現高質量可擴展的超導量子芯片提供有價值的技術參考.