半導體納米薄膜導電特性測試

熊 淑 平

(黃岡職業技術學院,湖北 黃岡 438002)

0 引 言

半導體產業制程演進速度愈來愈快,隨著對各式產品微小化的需求,人類的科技文明即將由微米時代逐步進入所謂的奈米時代[1]。納米結構是藉由原子、分子、超分子等級的操控能力以產生具有新分子組織的較大結構,這些結構具有新穎的物理、化學和生物的特性與現象。納米科技實際上并無統一的定義,一般說法系指物質在納米尺寸下呈現出有別于巨觀尺度下的物理、化學或生物特性與現象。所謂納米科技是運用這方面的知識,在納米尺寸等級的微小世界中操作、控制原子或分子組合成新的納米尺度結構(納米材料),以展現新的機能與特性。以此為基礎,設計、制作、組裝成新的材料、器具或系統,使之產生全新功能,并加以利用的技術總稱。納米科技的最終目標是依照需求,透過控制原子、分子在納米尺度上表現出來的嶄新特性,加以組合并制造出具有特定功能的產品。

隨著科技高速發展,日常生活用品將朝更微小、精細化的方向前進,半導體工業已進步到現今的0.13 μm水平。因此,在半導體材料的研發上,納米科技可以說是目前的趨勢,半導體納米薄膜即半導體納米顆粒所鍍的膜或納米厚度的膜。 半導體納米薄膜具有導電特性,如納米Si晶膜導電度為10~2 S/cm(bulk 10-11 S/cm)。納米級薄膜的技術開發極為重要,因為它在未來積極發展的積體電路制程扮演極關鍵的角色[2],面對納米世紀的來臨,如何在不斷微型化的積體電路制程里提供高效率與高性能同時高可靠度的超薄各型薄膜,是納米結構與材料研究學者與團隊最迫切的工作之一,預期這樣的制作技術將被研發成功并正式加入積體電路的生產流程可把現今的積體電路制作技術拓展至納米尺度的微型領域[3],朝著35 nm甚至更極限的線寬挑戰,制作出性能更為杰出且尺寸更小的各式電子電路元件。

1 樣品測試方案

1.1 納米薄膜膜面方向Seebeck系數與電導率

1.1.1膜面方向電導率測試方案

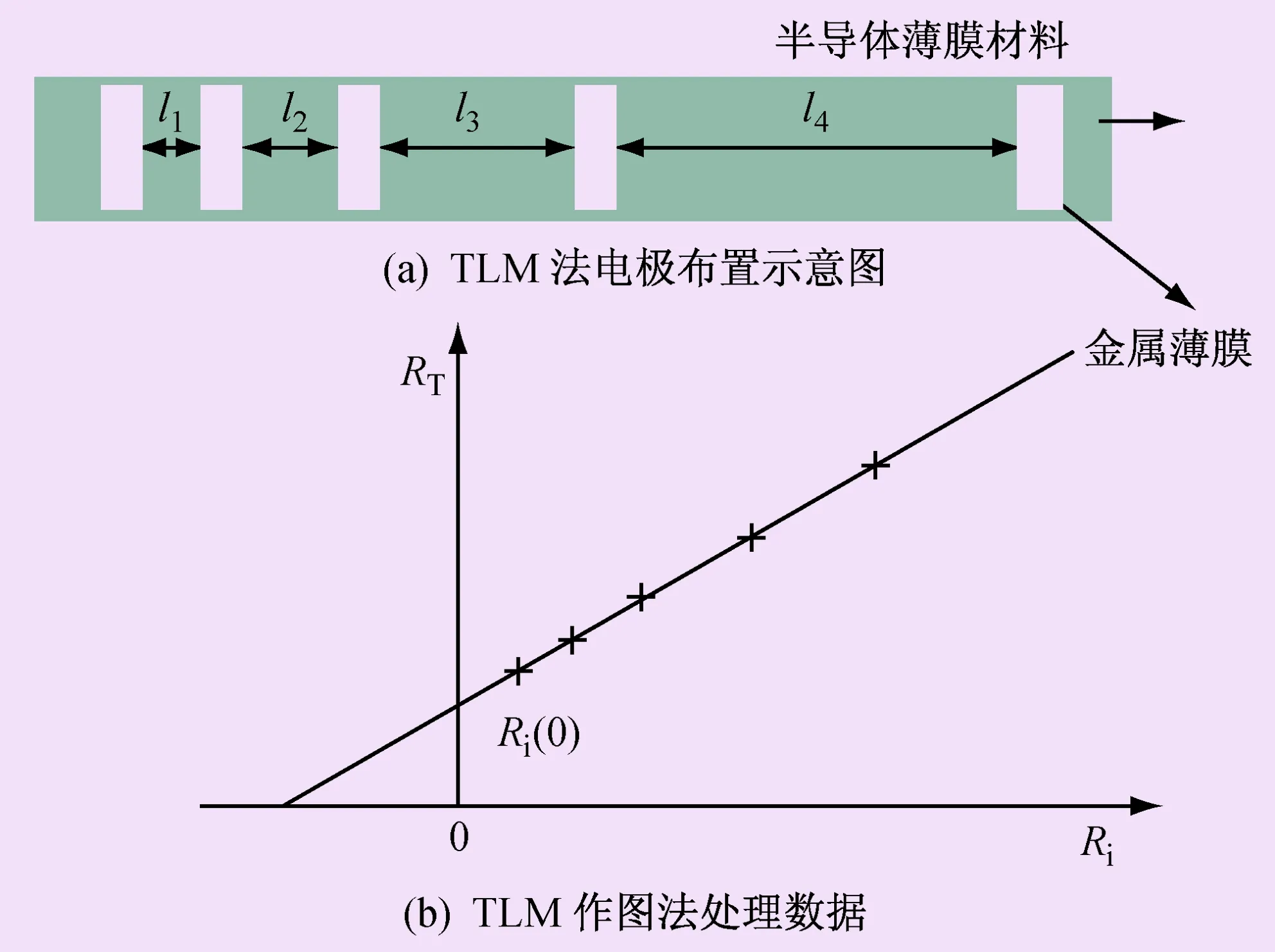

TLM法常用于金屬與薄膜之間接觸電阻的測量,在得到接觸電阻的同時也可以得到薄膜膜面方向的電導率。為提高測試精度,測試薄膜膜厚方向電導率時需要扣除接觸電阻的影響,因此綜合考慮,本測試系統采取TLM測試薄膜膜面方面電導率,并同時得到接觸電阻,為膜厚方向電導率的測量提供必需的數據。傳輸線法布置圖及作圖求解電導率和接觸電阻如圖1所示。

圖1 TLM法測試薄膜膜面方向電導率和接觸電阻率示意圖

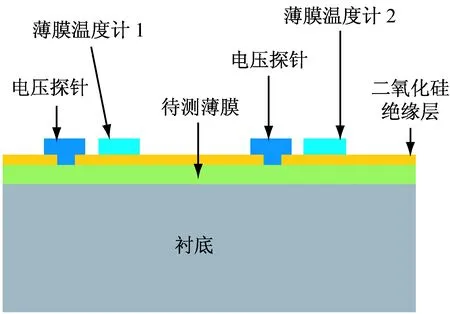

1.1.2膜面方向Seebeck系數測試方案

膜面方向Seebeck系數樣品布線方案設計圖如圖2所示[4]。由于樣品采用球柵陣列(BGA)封裝,測試系統使用樣品座代替直接接線方式通電測試及收集電壓信號,沿襲這一設計思想,因此采用直接在樣品上光刻微加工的方式[5],加工出薄膜溫度傳感器,在保證測量準確的前提下,可提高樣品的集成度,徹底擺脫接線方式的繁瑣操作。在樣品的兩端分別沉積兩個電壓探針,并在電壓探針附近分別沉積薄膜溫度傳感器,薄膜溫度傳感器材料選用鎳金屬,因為鎳金屬具有較大的電阻溫度系數(Temperature Coefficient of Resistance,TCR),且在較低溫度下的電阻與溫度有很好的線性關系。由電壓探針1、2采集到的電壓值和薄膜溫度計1、2采集到溫度差得到薄膜熱電材料的Seebeck系數。在樣品的一端沉積有金屬薄膜加熱器[6],通電可直接對襯底和薄膜樣品加熱,樣品的另外一端與大的銅塊接觸吸熱降溫,使襯底在某一方向上產生較為明顯的溫差和較大的溫度梯度,有利于膜面方向Seebeck系數的測試[7]。

圖2 膜面方向Seebeck系數測試方案

1.2 膜厚方向電導率的測試方案

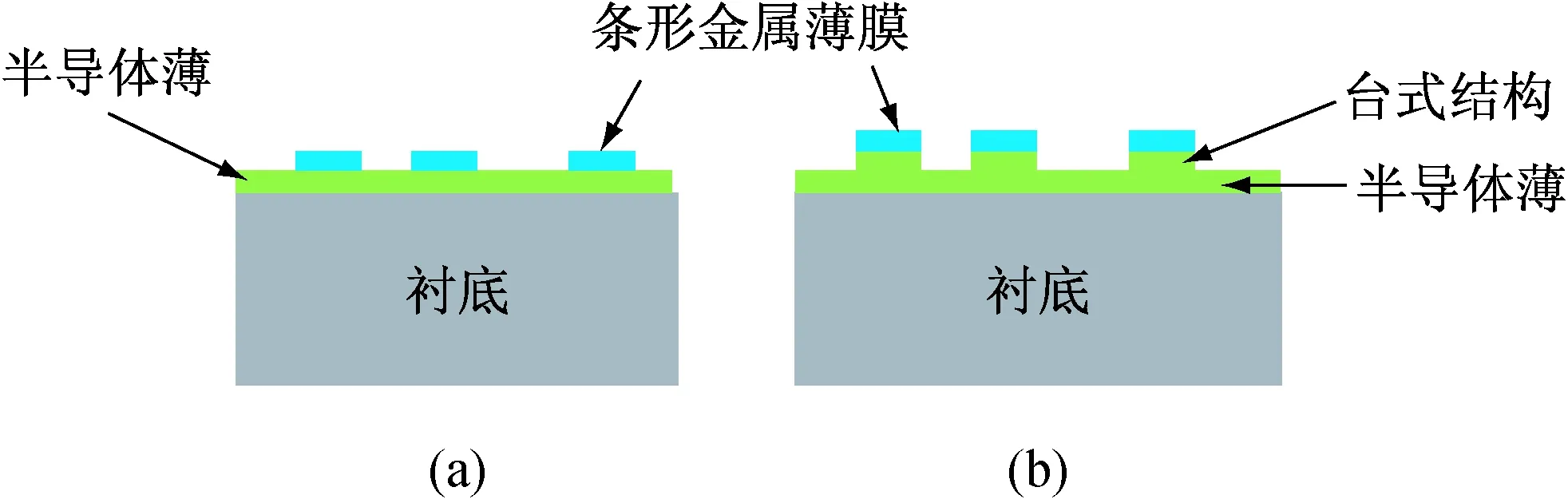

改進的傳輸線法(ETLM)一直是用來測試膜厚方向電導率的常用方法[8],該方法是在測試接觸電阻的TLM法基礎上,通過改進,加工出樣品的臺式結構,如圖3(b)所示,采取與測試接觸電阻相同的測量步驟并作圖,最終通過與TLM法所得電阻值求差,可得膜厚方向的電導率。

圖3 ETLM法測膜厚方向電導率

ETLM法由于需要加工臺式結構,而且要準確測得臺式結構的臺階高度,這在樣品制備的過程中需要花費較大的精力,難度較大,且所測得薄膜電導率為臺式結構的厚度方向電導率,而并非薄膜本身厚度方向的電導率。如果薄膜的電導率隨著厚度方向有所改變,則該方法所得到的臺式結構的電導率并不能等同于膜厚方向的電導率。因此本測試系統在設計過程中提出了全新的測試方案,與傳統四探針法測電導率的方法有一定的相似之處,稱之為準四探針法。

2 以納米科技增進半導體薄膜接點導電特性

歐姆接點是指施加電壓于其上時能提供元件所需的電流,但不會影響元件特性之接點,也就是在接點處的電壓降與元件工作區的電壓降相比要夠小[9]。傳統為了改進半導體薄膜介面而獲得歐姆接點,一般都是將金屬蒸鍍在半導體表面后,再進行所謂的退火處理即一種加熱處理,例如:鋁、矽接點須加熱至約450 ℃,以增進半導體接點導電特性,但在元件日益縮小的趨勢中,加熱所造成的滲雜原子擴散效應,會影響元件的功能[10]。此低溫制程是可行的改進方式。研究的目的即在提供有別于退火處理的另外一種選擇,即應用納米科技來改進半導體接點的導電特性,本實驗室應用電子束微影技術(Electron Beam Lithography),在矽晶片表面制造納米孔洞陣列結構,以改善半導體薄膜介面性質并增進其導電性,目前研究結果顯示,在矽晶片表面建構方型孔洞陣列,且在孔洞夠小的情況下,與未建構納米孔洞而只做退火處理的對照樣品相比,其金屬半導體薄膜接面的導電特性可獲致2~6倍的改善,而將具納米孔洞樣品再做退火處理時,可達到約4個數量級改進,而且其退火溫度及時間皆小于傳統退火處理者。

設計從200 nm至數十μm的方型孔洞陣列[11],以探究納米孔洞陣列結構特性對半導體導電特性影響。首先將設計好的陣列結構圖型經由電子束微影制程,將其刻劃在涂布于矽晶片表面光阻材料上,再經反應式離子蝕刻(Reactive Ion Etching,RIE)制程將圖型轉至矽晶片上,隨即將殘留于矽晶片表面之光阻材料去除,并清潔其表面及做去氧化層處理,即完成納米孔洞陣列的制作。接著將鋁蒸鍍在矽晶片表面[12],并涵蓋所有方型孔洞陣列區域,即構成一個金屬半導體接點,而4個接點依續兩兩之間距離為20、30及40 μm。形成一組基于傳輸線法的測量架構,以測量接點導電率。實驗結果顯示,在孔洞陣列涵蓋率夠大時(約大于8%),單位孔洞面積電導值即導電率與其涵蓋率無關[13],因為在高涵蓋率時導電性由流經孔洞內的電流來決定,而在低涵蓋率時導電性由流經孔洞外的電流來決定,從中并發現導電率會受到孔洞大小影響。導電率隨著孔洞的變小而增加。為了與不具孔洞陣列而只做退火處理的實驗樣品作比較[14],將一系列的實驗樣品從300 ~600 ℃,每隔50 ℃做退火處理,退火時間為10 min,得出在450 ℃作快速熱退火處理者可獲得最大導電率,為進一步確認此最佳值,以該溫度及550 ℃再進行退火處理30 min,結果亦獲得450 ℃為最佳退火溫度,遂將此條件下所獲得的導電率作為比較標準[15]。在孔洞小到480 nm以下時,其導電率已超越未具孔洞而只做退火處理之樣品,且達到2~6倍的改進。

3 結 語

使用本實驗室核心設備——電子束微影系統設計出的方型奈米孔洞陣列結構,成功地改進金屬半導體介面性質并達成增進其接點導電率的目標。實驗結果顯示,當孔洞小到480 nm以下時,其導電率能超越傳統退火處理的接點導電率,這也說明了小孔洞陣列結構可以取代退火處理,尤其是在低溫制程的應用中。

[1] L. Wang, C. Analysis of clipping noise and tone reservation algorithms for peak reduction in OFDM system[J]. IEEE Transactions on Vehicular Technology, 2008, 57(5): 1675-1694.

[2] A. Violation, Proto filter design for filter bank based multicarrier transmission[M].In Proceeding of European Signal Processing Conference, 2009, 9:56-59.

[3] H. Li, T. Jiang, and Y. Zhou. An improved tone reservation scheme with fast convergence for PAPR reduction in OFDM systems[J]. IEEE Transactions on Broadcasting, 2011, 57(4): 902-906.

[4] T. Jiang, Y. Wu. An overview: Peak-to-average power ratio reduction techniques for OFDM signal[J]. IEEE Transactions on Broadcasting, 2008, 54(2):257-268.

[5] J. Tell ado. Peak to average power reduction for multicarrier modulation. Ph.D. dissertation[J]. Stanford University, 1999, 8:90-93.

[6] J. Armstrong. Peak-to-average power reduction for OFDM by repeated clipping and frequency domain filtering[J]. Electronics Letters, 2002, 38(5):246-247.

[7] X. Li, L. J. Camino. Effects of clipping and filtering on the performance of OFDM[J]. IEEE Communication Letters, 1998, 2(5): 131-133.

[8] T. Jiang, G. Zhu. Nonlinear commanding transform for reducing peak-to-Average power ratio of OFDM signals[J]. IEEE Transactions on Broadcasting, 2004, 50(3): 342-346.

[9] X. Wang, T. T. Thong, and C. S. Ng. Reduction of peak-to-average power ratio of OFDM system using a commanding technique[J]. IEEE Transaction on Broadcasting, 1999, 45(3): 303-307.

[10] L. T. Lam, N. P. Haigh,etal. TMS320C6000 Inter-Integrated Circuit Module Reference Guide[M]. SPRU175A. Texas Instrument, 2002, 10:310-112.

[11] Huang, M. J., Y. L. Thou, DSP/BIOS Textual Configuration (Ton) User’s Guide[M]. SPRU007E. Texas Instrument, 2004, 4:167-168.

[12] 唐寅生. 基于MCR的SVC及其廣闊前景[J]. 電力電容器, 2003(1):77-78.

TANG Yin-sheng MCR SVC and its broad prospect of[J]. Power Capacitor Based, 2003(1):77-78.

[13] 張建生.半導體納米薄膜熱電性能測試儀器系統研究[J].華中科技大學學報,2012(9):33-36.

ZHANG Jian-sheng. Nano semiconductor thermoelectric properties of thin film testing instrument system[J]. Journal of Huazhong University of Science and Technology, 2012(9):33-36.

[14] 劉 詣.高職教育的實訓教學模式探究[J].天津大學學報,2008(5):91-92.

LIU Yi. Practical teaching of higher vocational education[J]. Journal of Tianjin University, 2008(5): 91-92.

[15] 黎中立.以奈米科技增進金屬的半導體接點導電特性[J]. 華中科技大學學報,2013(7):89-91.

LI Zhong-li. Promote semiconductor contact conductive properties of metal based on Nanotechnology[J]. Journal of Huazhong University of Science and Technology, 2013(7):89-91.