一種基于中頻信號的雷達原理實驗儀

甘 軼, 鄧有為, 張智軍

(空軍工程大學 航空航天工程學院,陜西 西安 710038)

0 引 言

電子類課程體系中“雷達原理”課程占據十分重要的地位,但由于其概念抽象,原理深奧,模型復雜,工作和處理方式多,學習難度較大。受限于雷達實裝缺失、雷達實驗儀器昂貴稀少等因素,院校難以有效開展雷達原理方面的實驗。另一方面,隨著計算機技術、數字信號處理技術的發展,雷達信號產生、信號處理完全可以依靠先進的數字處理器件DSP和大規模集成電路FPGA予以實現。這種趨勢下,使得基于雷達中頻信號建設一個仿真各種雷達信號及其工作狀態以開展雷達原理實驗內容的低成本實驗室成為可能[1-5]。

本文介紹一種基于雷達中頻信號的原理實驗儀的設計與研制,能夠實現真實雷達中頻信號產生、接收處理、解析上報,能通過計算機進行通信控制和結果顯示,為雷達發射信號測試、回波測試、處理演示、抗干擾等一系列課程內容提供了實驗手段,對深化學員理解雷達理論具有重要的意義。

1 系統功能與指標設計

1.1 功能設計要求

(1) 提供關鍵信號節點的輸入輸出接口;能夠與計算機進行通信,受計算機(上位機)操作軟件的控制,并能將處理結構上報到上位機進行顯示;

(2) 基于PD雷達體制,產生60 MHz中頻信號,并按控制要求形成中頻信號的波形調制,可以設置簡單脈沖、PRF可變,PM調制、LMF連續波等信號形式;可設高、中、低重頻模式;

(3) 能夠設置成搜索掃描模式和跟蹤模式。在任意模式下,完成中頻信號的采樣、加權處理、FFT、脈沖壓縮、CFAR、MTI、模糊解算等處理,并解算出模擬目標參數;

(4) 能夠產生設定模式下的干擾信號,并根據指令調整模擬目標與干擾信號的幅度,實驗不同干擾信號下的處理效果。

(5) 模擬天線掃描,關聯數據處理過程與結果。

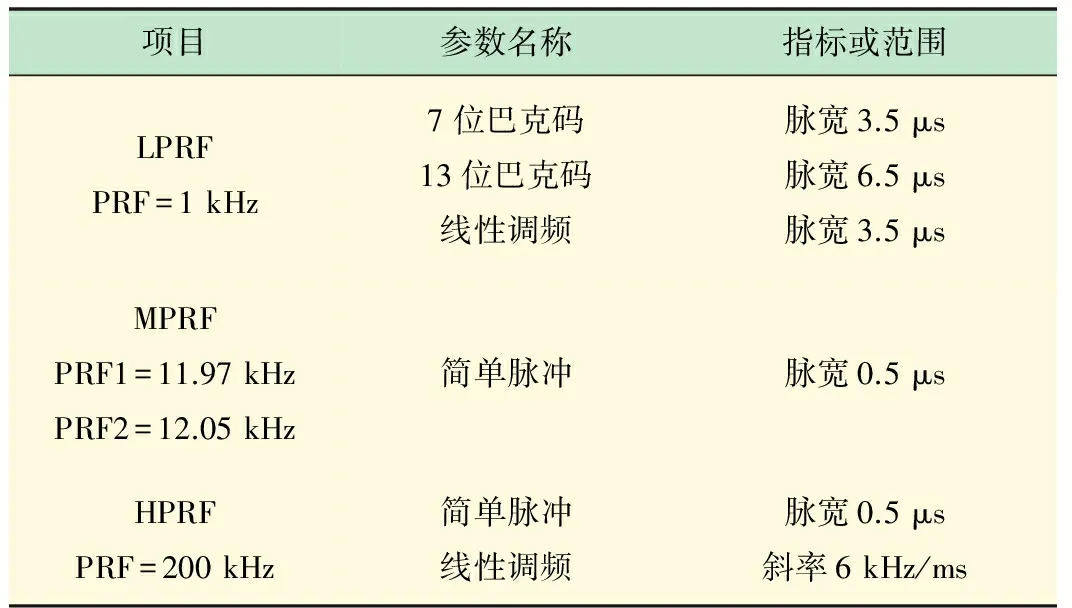

1.2 關鍵指標設計

實驗儀主要指標設計包括脈沖重頻、脈沖寬度、信號樣式與帶寬;其主要參數如表1所列。

表1 關鍵設計指標

而對于實驗儀自身產生的模擬目標和干擾信號,兩者具有獨立的頻率和幅度控制。其中按照雷達工作波長λ=0.03 m設計,模擬目標多普勒頻移范圍為±60 kHz;干擾信號預置不同干擾樣式,預置高斯白噪聲調幅干擾信號樣式。模擬目標回波與干擾信號強度分別可設定,模擬目標幅度設定采用256等級,干擾設定64等級。

對于信號處理環節,設定可選處理模式和門限參數。處理模式分為相參、非相參處理。對于門限調整則按照CFAR處理機制,預置參考門限。

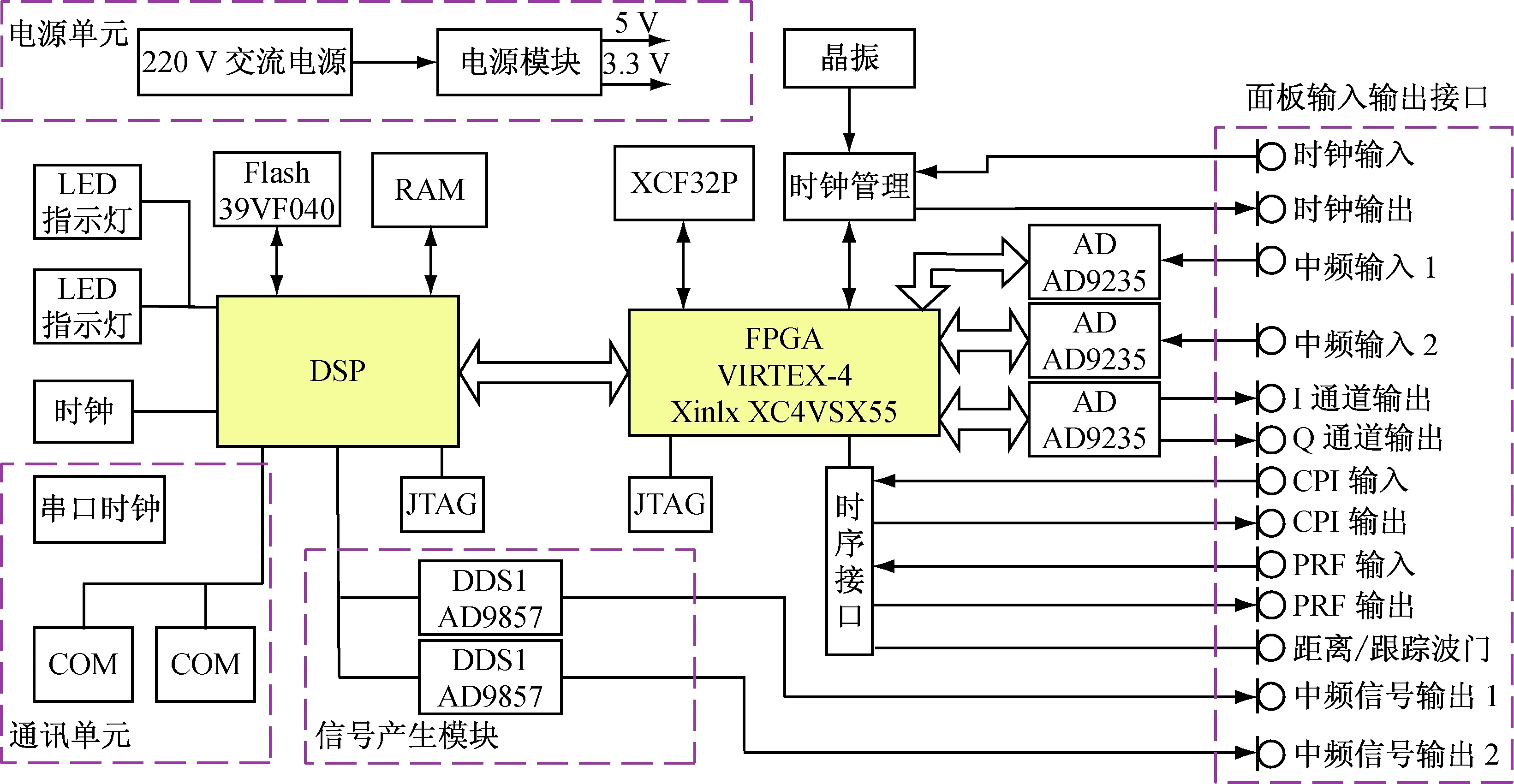

2 總體技術方案

規劃實驗儀主要針對雷達中頻信號進行硬件設計,實現采樣、數字信號處理,完成雷達核心功能,并能輸出節點的實際信號,用于實驗。基本方案是基于DSP和FPGA用硬件構成中頻信號產生、目標模擬、采樣、雷達信號處理的小型系統,實現雷達發射信號模擬、回波信號模擬,提供時序脈沖輸出,能夠通過上位機實現參數設置與結果輸出[6-8]。其總體技術方案框圖如圖1所示。

圖1 總體構成框圖

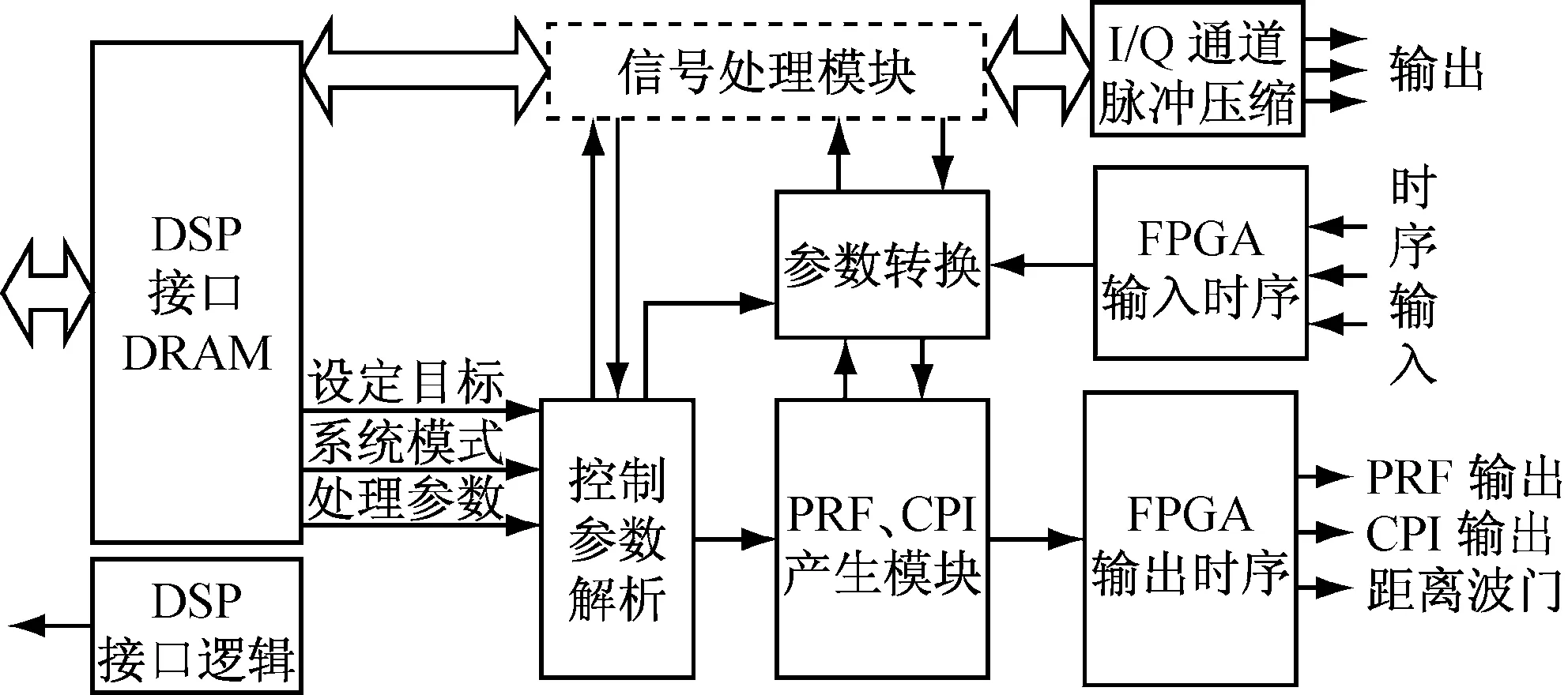

實驗功能主要依靠DSP和FPGA構成的處理系統實現。其中DSP主要負責與上位機的通訊,解析上位機的控制命令,按要求進行中頻信號產生的控制,并能接收FPGA模塊對信號的一次硬件處理結果,按照PD雷達數據處理機制實現對目標數據處理、解算,最終將目標數據和狀態通過通訊單元上報給上位機顯示。

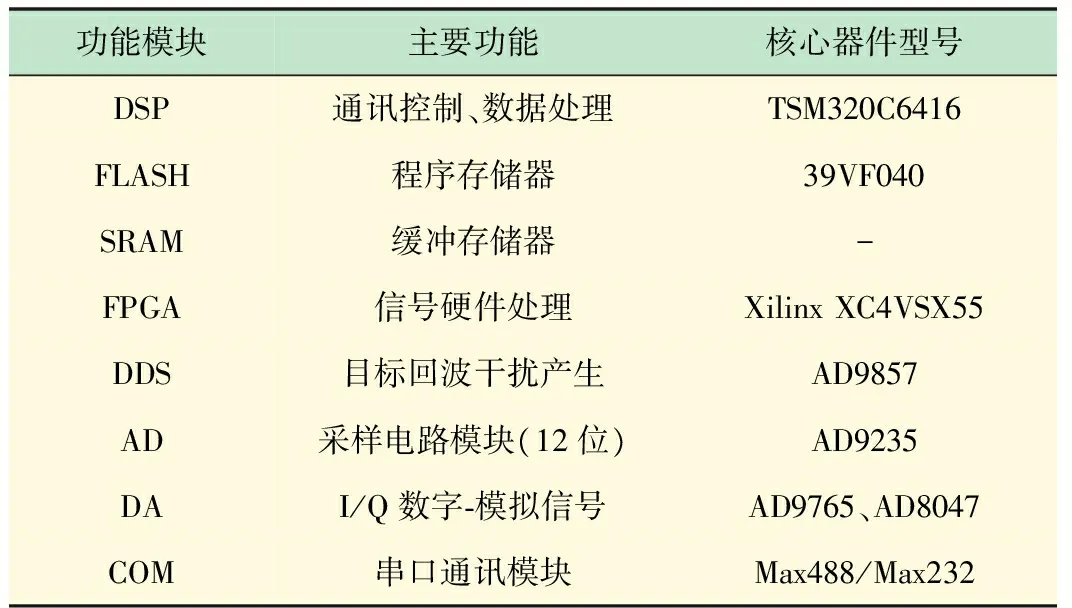

FPGA模塊主要負責對輸入信號的AD數據流進行處理,完成模擬回波信號的加權、脈沖壓縮、FFT以及恒虛警等信號處理,并將處理結果通過并行總線輸出給DSP模塊[9]。FPGA模塊中還實現了時序邏輯的輸出,依據上位機的控制指令要求,產生不同的脈沖重復頻率PRF,形成雷達處理節拍CPI時序,并按距離設置和跟蹤波門產生距離/跟蹤波門[10-11]。上述信號均能通過視頻脈沖形式進行輸出,方便測試。其中主要器件選型列表如表2所示。

3 主要功能設計與實現方法

3.1 回波與干擾信號產生

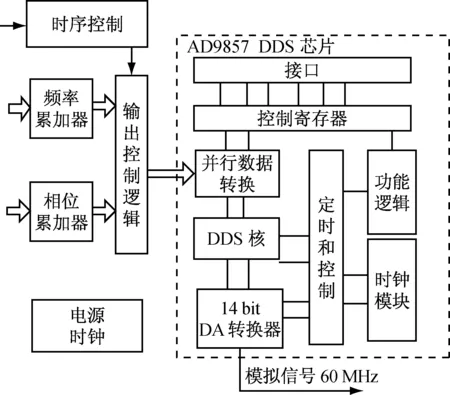

回波與干擾信號的產生是依賴于兩個DDS模塊實現的。其中一個模塊負責完成雷達目標回波信號產生,而另一個主要負責按照設定的干擾樣式進行干擾信號形成。核心芯片為AD9857,是一款14 bit高性能的數字上變頻器,內部集成一個32 bit正交DDS,實現8 bit的輸出幅度控制;其信號產生結構如圖2所示。

表2 主要器件選型表

圖2 信號產生結構

基帶信號參數改變時,DSP芯片更新基帶信號波形并寫入存儲器。

模擬目標參數是按照上位機設定的初值進行,可以設定為距離-速度關聯。其中模擬目標距離R指標要求為0.15~150 km,距離分辨為50 m。本設計中采用50 MHz時標,距離設置采用16 bit,則距離遲延數值N(R)與目標當前距離設定值R的控制關系為:

(1)

模擬目標多普勒頻率相位累加器時鐘采用10 MHz,16 bit字長,保證2 bit有效相移位,采用14 bit-ADC,相位累加器的加數N(F)與fd的控制關系為:

(2)

當fd小于零時,N(F)為補碼。在最高速度下,變化單位距離所用時間作為軟件定時時間,采用16 bit累加法控制距離運動,滿足距離-多普勒同步運動。

將回波基帶信號通過DDS調制和轉換輸出,中心頻率為60 MHz。干擾信號的產生與目標回波信號產生類似。

3.2 采樣與處理

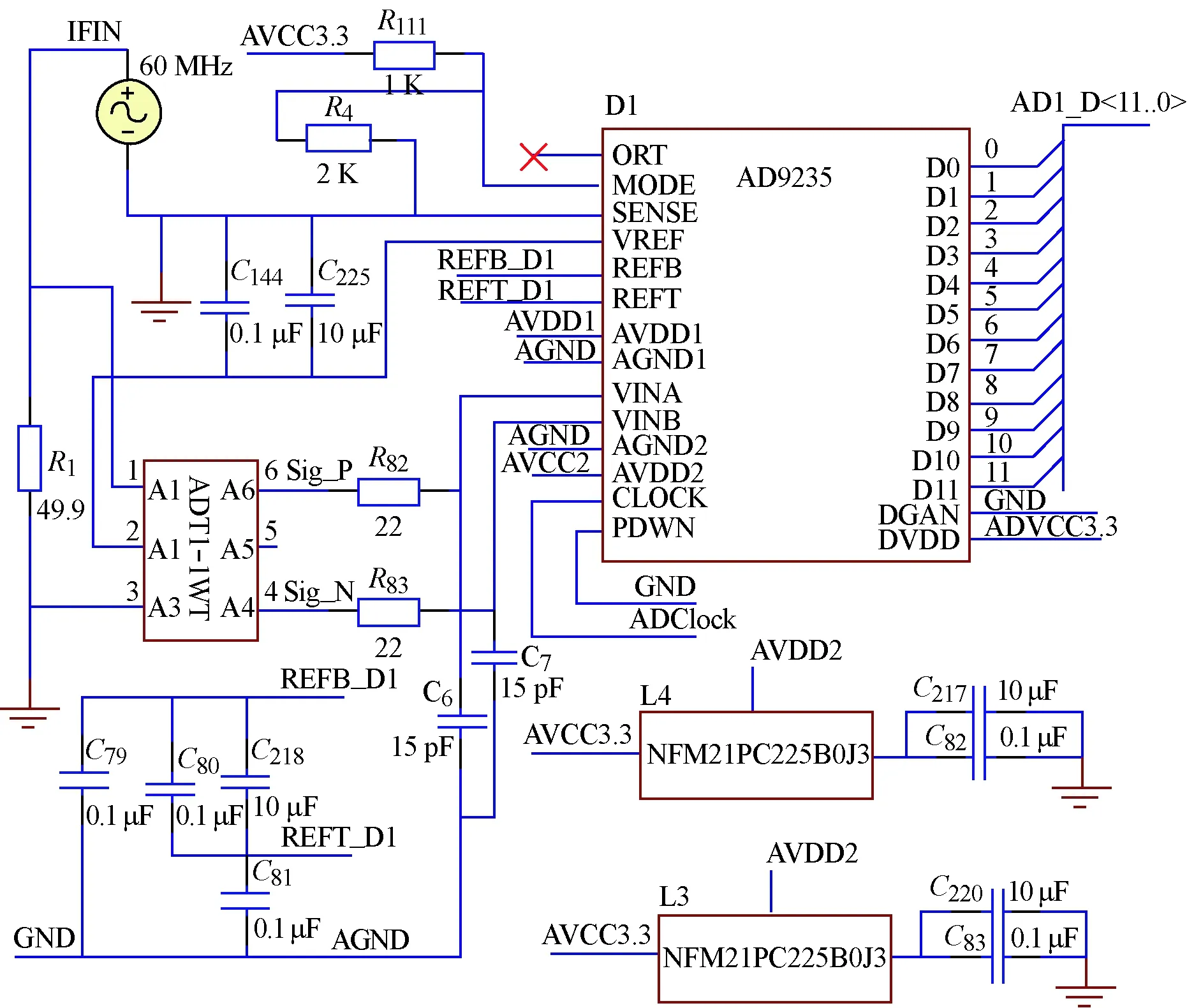

系統設計是在限定信號帶寬的基礎上進行的[12]。采樣電路采用AD9235進行設計,其轉換精度12位,采樣頻率48 MHz。通過數字混頻、濾波方式實現信號的變化。由于中頻60 MHz,采樣48 MHz,故混頻NCO頻率為12 MHz。其中采樣電路部分設計如圖3所示。

圖3 采樣電路的設計

考慮到濾波器的影響,經過抽取后的數據率應大于等于信號帶寬的1.25倍,在信號帶寬為2 MHz條件下,抽取后的數據率應大于2.5 MHz。在LPRF及MPRF模式下,選取抽取率為8,則抽取濾波器的階數為160階,抽取后數據速率為6 MHz。在HPRF模式中,選取數據抽取率為16,抽取后數據速率為3 MHz(48 MHz/16)。

3.3 信號處理與檢測

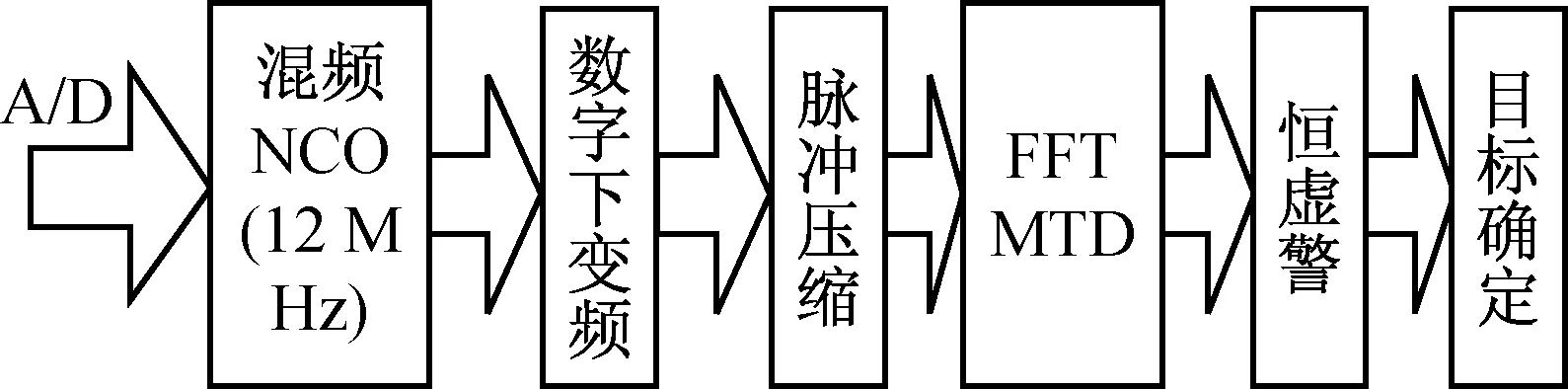

雷達信號處理與檢測主要依靠Xilinx公司的一片XC4VSX55高性能的數字信號處理FPGA實現,該器件具有SLICE、BLOCK RAM、DSP48、DCM等豐富資源,功能強大。對信號的主要處理結構如圖4所示[10-11,13]。

圖4 信號處理主要結構

根據處理結構和外部接口關系,可以把FPGA進行功能分區,如圖5所示。

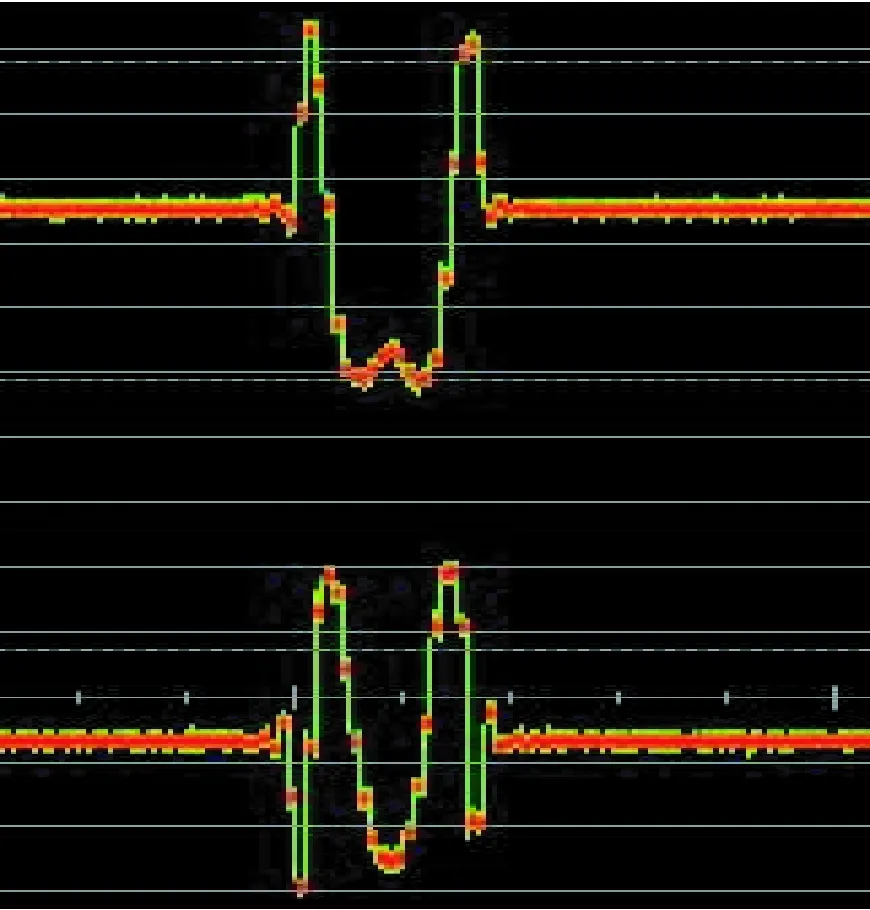

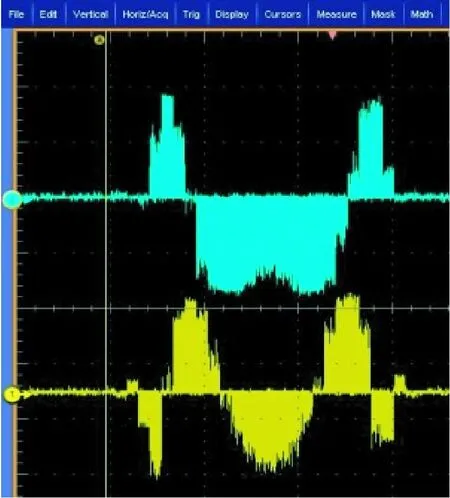

下變頻后信號I、Q由AD9765芯片進行DA轉換為模擬信號,并通過AD8047進行兩級放大輸出,供測試觀察。在LPRF模式下(線性調頻)實測的波形如圖6所示(測試儀器Tektronix DP07054)。

[7]的仿真圖對比,IQ通道信號輸出正確。另外設計中MTD采用8點FFT實現,恒虛警采用兩邊單元距離單元平均算法[14],保護單元為2,平均單元為8。在HPRF時進行頻率分析,FFT點數為1 024點。

圖5 FPGA的功能分區

圖6 實測的IQ通道信號

3.4 數據處理

數據處理部分以TI公司的TMS320C6416高性能定點數字信號處理器為核心進行設計。該器件最高工作時鐘600 MHz,可達4 800 MIPS。主要硬件資源有128 Kb L1P cache, 128 Kb L1D cache, 8 Mb L2 cache。兩個外部存儲器接口(EMIF),EMIFA為64 bit,EMIFB為16 bit,共1280M字節外部地址。

數據處理部分主要完成MPRF、HPRF模式下解模糊計算。其中MPRF模式下距離模糊解算依據PRF1、PRF2下測得距離Rprf1、Rprf2確定。在HPRF模式中以CPI為單位時間進行處理,對節拍內不同的PRF上同一個距離單元的數據做FFT運算。關于信號強度估計、距離門、頻率量一次給出在DSP中進行目標參數確定[12-13]。

3.5 輸出與通訊接口

試驗儀設計了時鐘、中頻RF、CPI、PRF等信號的輸入、輸出接口。工作時,單機可以依靠輸入輸出接口自環進行工作,以可以雙機互聯工作。互聯時,一臺設備及上位機實現目標初值設置,產生目標,并提供時間基準輸出;另一臺設備接收處理完成目標檢測處理和上報顯示。

與上位機的通訊采用串口通信。波特率為115.2 kb/s,分別設計上下行通訊協議。協議按包進行,每包數據自定義數據字幀頭、類型標識、數據內容、校驗與幀尾。其中數據內容包括目標方位、俯仰、距離、速度、備份字節構成,每信息2 byte。下行協議主要傳輸上位機給出的狀態控制、初值設定。

4 結 語

基于DSP與FPGA構成信號處理系統,可以方便地對系統進行升級和功能擴展,方便、靈活的模擬產生不同雷達信號樣式、設置不同目標的參數,開發不同的處理方法,為雷達信號處理提供了有效的調試平臺,加深了對雷達工作機理的理解,大大降低了對雷達實裝的依賴,具有很好的應用前景。

參考文獻(References):

[1] 梁 麗. 基于FPGA的雷達信號處理系統設計[D].南京:南京理工大學,2006.

[2] 楊 劍. 數字化雷達通用信號處理機設計[J].電路與系統學報,2009,14(4):25-28.

YANG Jian. Design of digital radar universal signal processor[J].Journal of Circuits and Systems,2009, 14(4):25-28.

[3] 張智軍,夏海寶. 雷達信號處理教學實驗系統的研制[J].實驗室研究與探索,2012(4):0148-04.

ZHANG Zhi-jun,XIA Hai-bao. Development of an Experimental System for Radar Signal Processing Teaching[J]. Research and Exploration in Laboratory, 2012,31(4):0148-4.

[4] Skolnik M I. Introduction to Radar System[M]. 3rded. New York: McGraw-Hill Companies, 2001.

[5] 任宇峰. 基于虛擬儀器技術的雷達信號模擬器設計[J].現代電子技術,2010,33(19):67-70.

REN Yu-feng. Design of Radar Echo Simulator Based on Virtual Instrument Technology[J]. Modern Electronics Technique,2010, 33(19):67-70.

[6] 楊鴻鵠, 許蘊山. 基于FPGA+DSP的雷達回波發生器設計[J].電子技術應用,2009,35(12):57-60.

YANG Hong-hu, XU Yun-shan. Design of a radar echo generator based on FPGA and DSP[J]. Application of Electronic Technique, 2009, 35(12): 57-60.

[7] 孫實澤,杜春鵬. 多體制雷達視頻模擬器設計及實現[J] .中國雷達技術論壇, 2008, 31(7):014-04.

SUN Shi-ze, DU Chun-peng. Design and Realization of Multi-system Radar Emulator[J]. Modern Electronics Technique, 2008, 31(7):014-04.

[8] 邱燕軍,申功勛. 基于DSP+FPGA的高速信號采集與處理系統的信號完整性分析[J]. 測控技術,2007,12(26):12-15.

QIU Yan-jun, SHEN Gong-xun. Analysis on Signal Integrity of High Speed Signal Collection and Processing System Based on DSP and FPGA[J].Measurement & Control Technology, 2007,12(26):12-15.

[9] 周 杰,劉 鎏. 一種TMS320C6000 DSP與FPGA通訊方法的研究[J].硅谷, 2010(24):88-89.

ZHOU Jie, LIU Liu. Study of a communication method between TMS320C6000 DSP and FPGA[J].Silicon Valley, 2010(24):88-89.

[10] 張建華.PD雷達接收機及信號處理系統仿真研究[D]. 成都:電子科技大學,2006.

[11] 劉冬利.雷達中頻信號直接采樣與正交相干檢波的設計與實現[J].現代雷達,2001,23(3):38-41.

LIU Dong-li. The Design and Implementation of Radar IF Signal Sampling and Quadrature Coherent Detection[J]. Modern Radar,2001,23(3):38-41.

[12] 車志超.基于FPGA的數字中頻接收機設計[J].探測與定位,2011,6(2):35-39.

CHE Zhi-chao. Design of Digital IF Receiver Based on FPGA[J]. Detection and Location, 2011,6(2):35-39.

[13] 戈 穩. 雷達接收機技術[M].北京:電子工業出版社,2005.

[14] 馬 健,王晟達. CMCAM恒虛警檢測器性能分析[J]. 空軍工程大學學報, 2009(4):29-32.

MA Jian,WANG Sheng-da. Performance analysis of CMCAM CFAR[J]. Journal of Air Force Engineering University,2009(4):29-32.

[15] 郭 博. 機載PD雷達系統的模擬與仿真[D].西安:空軍工程大學工程學院,2009.

[16] 向道樸. 一種通用雷達回波模擬器的設計與實現[J].現代雷達,2007,29(10):84-86.

XIANG Dao-pu. Design and Implementation of a General Digital Radar Echo Simulator[J]. Modern Radar, 2007,29(10):84-86.