論房地產價格影響因素與發展趨勢

摘要:本文研究房地產價格的影響因素,對供求因素進行梳理,通過對以前數據的收集、分析。發現其中的規律與聯系,并作出推論。影響房地產價格內在因素:數據顯示,人口的老齡化加深、城鎮化比率較高、市場的高度競爭化和市場存量大,總體形成了供大于求的發展趨勢,逐漸形成了買方市場,價格繼續上升的壓力較大。而順應其變化,房地產市場的發展趨勢也出現了新的變化方向,如何打破瓶頸,實現新發展。需要從需求、供給兩端入手。以人為本,滿足不同層次的需求:不同城市因地制宜,根據自身情況制定相應的政策,發揮優勢資源,實現協同化發展。

關鍵詞:房地產價格;影響因素;發展趨勢

Abstract:This paper studies the influencing factors of the real estate price,summarizes the factors of supply and demand,and draws a conclusion through the collection and analysis of the previous data. Discover the laws and connections among them,and make inferences. Internal factors affecting real estate prices:data shows that the deepening of population aging,high urbanization rate,highly competitive market and large market stock have generally formed a development trend of supply exceeding demand,gradually forming a buyers market,and the pressure for prices to continue to rise is large. In accordance with its changes,the development trend of the real estate market has also shown a new direction of change,how to break the bottleneck and achieve new development. We need to start from both sides of demand and supply. People oriented,to meet the needs of different levels:different cities adapt to local conditions,formulate corresponding policies according to their own conditions,give full play to the advantages of resources,and achieve coordinated development.

Key words:real estate price; influencing factors; development trend

引言:改革開放以來中國經濟騰飛,而房地產市場更是得到了蓬勃的發展。而因為城市的發展和人們對美好生活的追求,房屋供不應求,房價飛速上漲,不斷的出現“天價房”“地王”的消息。大城市,人們排隊買房卻“一房難求”,高額的首付款更是讓人望而興嘆,三四線卻大量小區變成“空城”,背后更多的是城市之間如何才能協同發展的問題。越來越多的人選擇租房,除了高額的房價,更多是現在人們的生活壓力逐漸變大儲蓄意愿的增強。面對新時代下的種種情況,房地產市場必須要謀求轉型,當地政府出臺改革措施,才能更好的滿足人們的需求。

1 房地產市場價格的影響因素

1.1 人口因素影響

改革開放以來,人民物質生活水平不斷提升,我國人口變化出現了新的特點:1.我國人口增長模型轉向現代型:人口增速放緩,購房適齡人口下降。2風險預期增加,儲蓄率上升:撫養比上升,人們儲蓄意愿增強。而這些新情況的出現,將會對房地產的有效需求造成沖擊。

1.2 人口增長模型轉向現代型

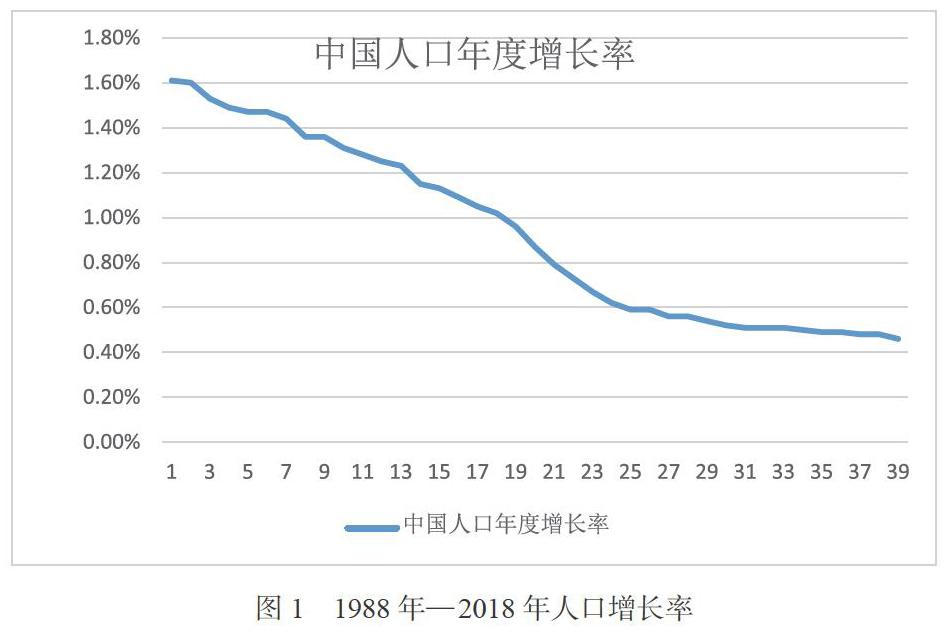

通過收集了1988年—2018年的數據,如圖一所示,我國的人口增長速度呈現持續下跌的趨勢,特別使近二十年,呈現出加速下跌的趨勢。而根據統計數據顯示:我國的購房適齡人口(25-49歲人口)在2015年達到5.68億人的高峰,隨后開始減少。2016年,我國購房適齡人口為5.66億人,占總人口的40.93%,相比2015年減少257萬人。購房適齡人口的下降在一定程度上降低房地產行業的總需求,

而這也對現有的房地產市場產生了影響,之前,城市需求熱度從東部向中西部蔓延的過程,三四線城市銷售也高歌猛進,成交創歷史新高。而進入 2018 年后,這種熱度蔓延的趨勢進一步擴散、 進一步下沉,但增速呈現放緩。前 4 月全國商品房銷售面積僅同比增長 1.3%,4 月單月同比增速已轉為負增長。

1.3 人們的風險預期增加

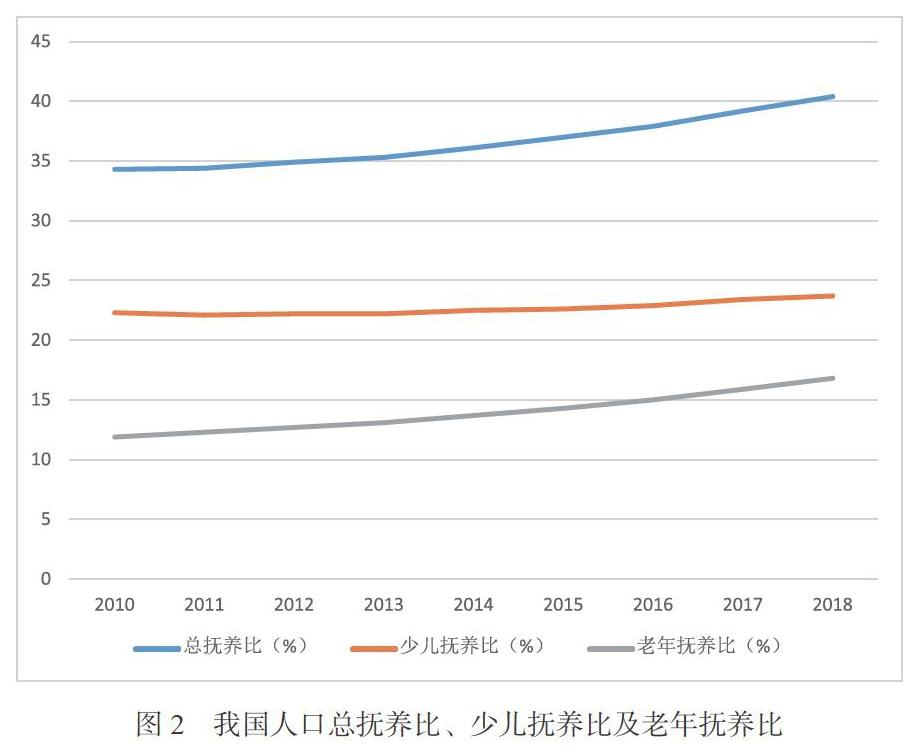

隨著人口結構老齡化,勞動力人口比例下降,社會負擔加大,養老、醫療會擠壓相應的市場。而421的家庭模式,更是導致了我國的撫養比上升,撫養比的上升也會導致了儲蓄率的下降,加大我國的經濟下行壓力,對房地產的市場價格產生不利影響。

根據國家統計局數據顯示,2019年末,全國0-15歲人口為24977萬人,占總人口的17.8%;16-59歲人口為89640萬人,占64.0%;60歲及以上人口為25388萬人,占18.1%,其中,65歲及以上人口為17603萬人,占12.6%。與2018年末相比,16-59歲勞動年齡人口減少89萬人,比重下降0.28個百分點;老年人口比重持續上升,其中,60歲及以上人口增加439萬人,比重上升0.25個百分點;65歲及以上人口增加945萬人,比重上升0.64個百分點。

從上圖可以看出,雖然目前我國的人口基數較大,但是勞動人口的占比不斷下降,人口撫養比逐漸上升,人們經濟負擔壓力加大,儲蓄意愿加強,對房地產市場的產生擠壓,需求減少。

2 城市因素影響

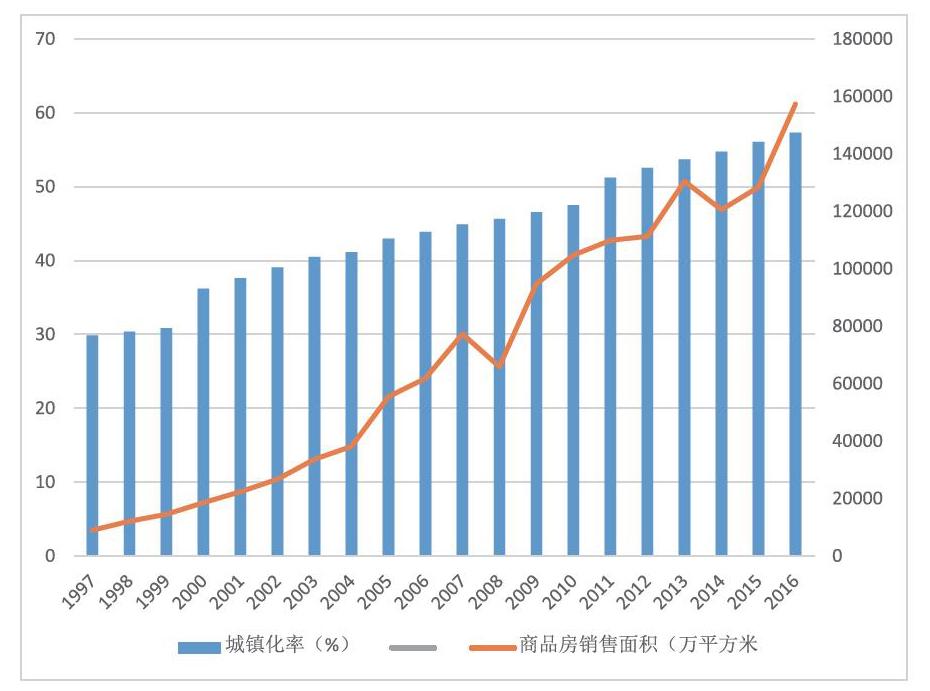

由上圖的數據我們可以發現,改革開放二十年來城市化率拖動了房地產市場的發展,城鎮化的進程和房地產市場呈現了正相關。但是到了2020年我國的城市化率達到60%左右,城鎮化水平到達了一個相當高的水平。當達到這個數值的時候,城市化的速度將會大幅下降,也就是說我國的房地產市場價格會受城鎮化速度下降的趨勢影響。

3 市場因素影響

市場方面的因素,則主要從市場目前的參與者、競爭者、市場目前的房屋存量兩個方面來分析其對價格的影響。

(1)從整個市場的競爭來看,市場競爭較大,生產者對價格掌控力度較小。從銷售情況來看,2019年上半年中國房地產企業銷售金額TOP100的門檻值為114.1億元,較去年同期的58.4億元增長95.39%。緊隨其后的是TOP50門檻,為322.2億元,同比增長37.16%。增長較為緩和的是TOP3、TOP5以及TOP20,分別為-2.84%、12.38%和9.62%。也就是說目前來看房地產市場寡頭競爭和壟斷資本趨勢并不明顯,而整個市場的活力較為充足,市場供應量較為充足,同等情況下,競爭者會考慮具有價格優勢的競爭者。

(2)目前的市場存量相對較大,由西南財經大學中國家庭金融調查與研究中心主任甘犁發在《2017中國城鎮住房空置分析》報告中說出了幾個數據:一線城市、二線城市、三線城市住房空置率分別為16.8%、22.2%、21.8%,其中商品房空置率為26.6%,并且空置率呈逐年上升趨勢。而2018年前11個月,中國土地出讓收入最高的50大城市合計“賣地”收入3.27萬億元,同比上漲7.3%。而去年同期的上漲速度在30%以上,增速明顯放緩。房地產將逐漸從增量市場,轉為存量市場,這市場價格波動將會變小。

4 房地產行業的未來發展趨勢

面對市場環境的快速變化,我們可從房地產供需兩側分別著手,在政府政策的支持領導下,從最大化滿足社會現實需求,實現社會有效供給的角度對未來房地產行業發展趨勢進行如下預測:

4.1 需求端:以人為本,多元化發展以滿足不同人群需求

4.1.1 健康+房地產

以生態健康為導向,通過將休閑旅游與健康養老相結合,建立起各種養老山莊,老年公寓等。并完善相應的醫療配套措施等。以滿足我國人口老齡化的需求和解決大量空巢老人無人照顧的現狀。堅持生態化建設,拒絕過去的粗放簡單的開放模式。基于5R原則(減量化、再使用、再循環、再生、拒用),提升產業的生態附加值和住宅的使用舒適度。

4.1.2 交通+房地產

以交通樞紐為導向,整合城市間和城市內交通資源,高鐵、輕軌、快速公交一體化建設,推動城市之間要素的流動。在A城上班,B城工作的推廣,緩解大城市用地緊張,小城市空置率居高不下的問題。加強城際軌道交通建設,打造更多的一小時經濟圈。

以交通站點為中心,合理產業布局,使城市規劃和住房分布結構相適應,完善配套措施,合理化人口分布。

4.2 供給端:優化市場資源配置,釋放產業活力

4.2.1 因城施策,發揮好頭部引擎作用

因為我國處于社會主義初級階段的時代背景,“京津翼”“長三角”“珠三角”等地區,城市化水平、人口增速等明顯高于其他地區。要引導和鼓勵高端資源不斷數量集聚和結構優化,外圍城市完善服務和配套措施,在適度集聚基礎上建立多中心的良性格局。

4.2.2 優化房地產市場結構

提高行業準入門檻,淘汰過去粗放型的發展模式。推動企業間的合并重組,發展房地產“大企業融資+中小企業代建”的商業合作模式,通過共享大中小房地產企業各自優勢,來降低房屋成本,從而推動降低價格,來幫助房地產打開需求市場。使企業能夠適應不同城市的市場特性,也使企業推出的產品滿足不同人群的需求。

結語:因此,從收集到的數據和資料來看,在人口、城市、市場等的因素作用下,我國的房地產市場逐漸出現了供大于求的形勢,這將導致已經處在高位的房地產市場價格出現趨于平穩的趨勢,在未來有逐步下降的可能。而在目前的市場狀況下,在需求端,為了符合我國人口老齡化的趨勢,房地產行業和養老健康產業結合,在供給端,形成“融資+代建”模式,都是我國房地產市場未來的發展趨勢。

參考文獻:

[1] 熊平.房地產價格影響因素研究——基于供給需求框架分析[J].科技風,2019(26).

[2] 李祖毅.住宅設計的發展趨勢及影響房地產價格因素的探討[J].住宅與房地產,2017(05).

[3] 申博,焦紅兵,張曌囡.房地產價格對我國居民消費影響因素的總結和展望[J].現代營銷(信息版),2020(03).

[4] 馬香品,姚慧琴.供需視角下的我國房地產價格波動的空間差異及成因分析[J].經濟問題探索,2020(02).

[5] 張可.中國房地產價格影響因素與發展趨勢研究[J].現代營銷(信息版),2019(06).

[6] 任凱.基于消費者購買力的房地產市場供需平衡分析[J].現代企業,2020(01).

[7] 宋澤敏.我國房地產經濟發展現狀及發展趨勢分析[J].現代商業,2019(25).

[8] 孔新樂.基于房地產市場供求視角下促進房地產經濟發展研究[J].建材與裝飾,2020(08).

[9] 包杰宗.淺談房地產市場的發展狀況和問題[J].綠色環保建材,2020(04).

[10] 何葉榮,陳瑞,方穎,等.房地產市場風險測度及可持續發展路徑研究[J].技術與創新管理,2020(02).

作者簡介:唐楷程(1999—),男,四川遂寧人,本科,研究方向:房地產市場分析。

(作者單位:四川農業大學商學院)