基于FPGA 的數字濾波器設計

周 鈞 樊 闖

(中車大連電力牽引研發中心有限公司,遼寧大連 116000)

0.引言

隨著國內需求和科技發展,軌道交通進入了高鐵時代,目前列車與基站之間無線通信需要靠無線基站通過載波進行通訊,一般采用特定的頻段(2.4GHz)。載波在傳輸的過程中容易受到干擾,比如噪聲干擾。為了實現通信需求,可在接收端設置數字濾波器,是一種可從受環境噪聲干擾的測試信號中分離出特定載波頻率信號的濾波器,可提取以參考頻率為中心的指定頻帶內的信號,有效濾除所有其他頻率分量(噪聲信號),完成載波數據的通信信號通信,進而實現更好的無線網絡通信[1]。

1.設計原理

本文設計的數字濾波器基于“通信信號是時間上相干的,而噪聲信號在時間上是不相干”的原理設計。已知通信信號的頻率,可生成具相同頻率的參考信號。將參考信號與測試信號(包含通信信號與噪聲信號)相乘,可將測試信號中的通信信號和噪聲信號相互分離,然后借助積分器消除噪聲來實現功能[2],如圖1 所示。

圖1 數字濾波設計原理

將測試信號(messsignal)與參考信號(referencesignal)進行相乘后,再積分運算,去除時間無關的干擾信號,獲得帶正弦與余弦的表達式:

同理,同樣的模塊,獲得帶正弦的表達式:

通過三角函數定理:

實現通信信號未知參數A(振幅)的計算,完成提取以參考頻率為中心的指定頻帶內的信號,有效濾除所有其他頻率分量,實現數字鎖相濾波。

2.開發環境概述

本文中環境由FPGA 開發板、示波器和信號發生器組成。Spartan 3E:XC35C500 芯片滿足需要的LUT 資源和I/O 資源,含一個LTC 1407A 模數轉換器和一個LCD 顯示器。示波器Tektronix TPS 2024:帶寬為200MHz,最高取樣速率:2.0GS/s,具有4 個通道。信號發生器HM-8030:頻率50MHz 至10MHz,具備高純度和幅度穩定性。

3.基于FPGA 的數字濾波器設計

3.1 設計框架

FPGA 設計框架如圖2 所示。

圖2 FPGA設計框架

3.2 信號處理流程

如圖2 所示,測試信號(messsignal:VinA)和參考信號(referencesignal:VinB)被ADC 芯片采集轉化,這部分由ADC 芯片完成;接下來,轉化的數據進入數據處理模塊(LIV)進行信號分離濾波,分離信號三角函數計算,積分濾波和其他處理;之后將處理完成的結果發送到LCD 控制模塊,最終在屏幕上進行結果打印[3]。

3.3 設計實現

本文設計根據在噪聲環境下的數字濾波需求,結合開發板資源,設定適當的采樣頻率范圍和輸入波形,通過由頂層到底層的設計思維,進行FPGA 的代碼編寫進行代碼設計。

(1)根據濾波技術要求,確定濾波器類型、算法、系統精度誤差、采樣頻率、輸入數據長度和輸出數據顯示方式;(2)根據確定的技術參數設計頂層架構和頂層邏輯結構;(3)在頂層架構里定義和描述全局代碼結構,各子模塊之間的關系。信號輸入和屏幕輸出參數同樣在頂層定義;(4)頂層模塊之下,由模數轉換模塊,信號處理模塊,濾波模塊和LCD 顯示模塊這些二級模塊組成;(5)各二級模塊根據功能劃分,將各自功能用VHDL 進行編碼設計。二級模塊經過仿真實現,在頂層模塊進行結合,實現一整套系統功能。

3.3.1 模數轉換設計

ADC 芯片將采集的模擬信號離散化為單個離散采樣值。再將采樣值轉為數字值,根據板卡搭載的ADC 芯片LTC 1407A,模擬信號被轉換為14 位的數字信號[4]。

3.3.2 信號分離設計

(1)參考信號作為已知的信號,進行三角分解,分解成sin 向量和cos 向量;(2)將模數轉換后的測試信號和分解后的參考信號相乘,獲得第一混合信號,并分離第一混合信號中的噪聲;(3)根據已知的參考信號對第一混合信號進行計算,獲得沒有噪聲的通信信號的sin 向量和cos 向量,即通信信號的sin 向量和cos 向量;(4)根據通信信號的sin 向量和cos 向量,計算測試信號不含噪聲的振幅、測試信號不含噪聲的初相。

3.3.3 濾波設計

本文中的低通濾波器為有限沖擊響應濾波器(FIR),積分運算通過該低通濾波器進行實現,經過低通濾波器后,噪聲信號將被過濾掉,通信信號將被保留并輸出。

3.4 simulation 仿真

本文設計需要實現模數轉換,所以simulation 仿真內容只能實現到靜態時序分析上,通過testbench 產生數字激勵并通過ISE14.7 自帶的仿真軟件進行仿真。

3.5 硬件協同仿真

硬件協同仿真即半實物仿真,本文設計中將編碼完成的“.bit”工程文件下載到開發板中進行仿真。本文用信號發生器生成兩路模擬信號,A 路測試信號,B 路參考信號,A 路上加載干擾信號(噪聲信號)。兩路輸出信號鏈接至ADC 芯片上,信號通過ADC 芯片后離散為數字信號,進入系統進行分離、濾波,最終的結果將顯示在LCD 屏幕上。

4.測試驗證

驗證數字濾波器除噪功能,測試是唯一的標準,因為simulation 仿真產生的模擬信號可以非常接近,但是始終無法完全代替真實的模擬信號。本文設計測試時,對不同的頻率和振幅進行了測試,并對實驗結果進行描述。

4.1 測試

通過采樣和邏輯運算后,在LCD 屏幕上將打印3 個信息:S:帶正弦(sin)的表達式,C:帶余弦(cos)的表達式和A:振幅(amplitude)。如圖3 所示,測試1通信信號振幅為1V(峰-峰值2V)。FPGA 處理后的數據比較精確地將振幅鎖定在1V(正負3.5%);同理,測試2 通信信號振幅為0.72V(峰-峰值1.44V)。處理后的數據的振幅鎖定在0.72V(正負1%)。

圖3 測試驗證

4.2 測試列表

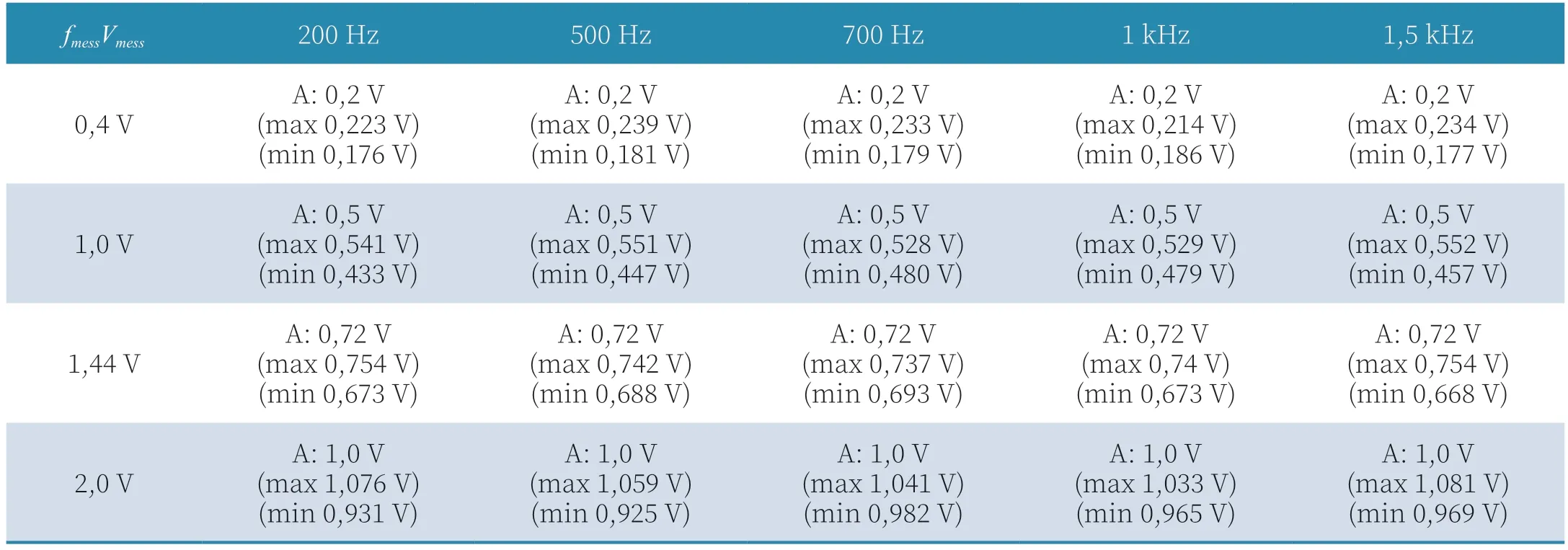

將不同頻率和振幅的測試數據進行匯總,得到的匯總表格如表1 所示。

表1 測試數據匯總

可以發現FPGA 處理后的數據比較精確和穩定,誤差范圍可控。證明了在噪聲環境中通過噪聲信號非時間相干特性原理設計的數字濾波器,可以較好地獲取通信信號。

5.結語

本文介紹了基于FPGA 的數字濾波器的原理,系統結構,以及核心算法模塊結構。在VHDL 語言環境下創建系統仿真模型,并在實驗室環境中通過在FPGA 硬件板卡上進行硬件協同仿真測試。硬件協同仿真測試結果表明,該數字濾波器的性能滿足從復雜環境中過濾干擾信號的濾波設計技術要求。在信號處理單元中,通常需要利用濾波器對電網電壓信號進行采樣濾波,采用上述模型進行數字波器設計,可以實現良好的消除噪聲特性。