一種高效的交錯并聯Boost PFC研究

閻昌國,敖邦乾,曲祥君,劉小雍(遵義師范學院工學院,貴州遵義,563002)

?

一種高效的交錯并聯Boost PFC研究

閻昌國,敖邦乾,曲祥君,劉小雍

(遵義師范學院工學院,貴州遵義,563002)

摘要:升壓電感作為交錯并聯BoostPFC系統的關鍵元件,其寄生電容的損耗會對系統的效率產生影響。作者針對傳統升壓電感存在寄生電容大、損耗高的問題,提出了一種具有寄生電容小、損耗低等優點的改進設計方法,設計了一個685W的帶交錯并聯Boost PFC的樣機系統。測試結果表明:較之傳統方法,作者所提改進方法搭建的系統具有更高的效率,更能適應交錯并聯Boost PFC的高效發展。

關鍵詞:升壓電感;交錯并聯Boost PFC;寄生電容;高效

急劇增加的電力電子裝置使得電網諧波污染日益嚴重,PFC電路是消除諧波污染的有效方法。傳統BoostPFC變換器因功率開關管存在較大的電壓、電流變化率會帶來嚴重的電磁干擾,難以適應系統功率等級增加的需要[1]。而交錯并聯Boost PFC變換器因具有功率因素高、輸入電流紋波小、轉換效率高以及控制能力強等優點,被廣泛應用在中大功率的電子設備中[2-6]。文獻[7-9]通過改善交錯并聯Boost PFC升壓電感的設計方法,有效地減小了電感的數量、體積及尺寸,有效地提高了系統的整體性能。但這些改進的方法仍然沒有脫離傳統電感設計方法的剛性基底模型,存在著較大的寄生電容,這些電容在功率管通斷間存在較大的損耗,會嚴重影響系統的效率。針對上述不足,本文提出了一種脫離傳統電感剛性基底模型的設計方法,并通過理論分析證實該方法設計的電感具有寄生電容小、損耗低等優點,最后用685W實驗樣機的測試結果驗證了本文理論分析的正確性與可行性。

1原理與電感的設計

1.1工作原理

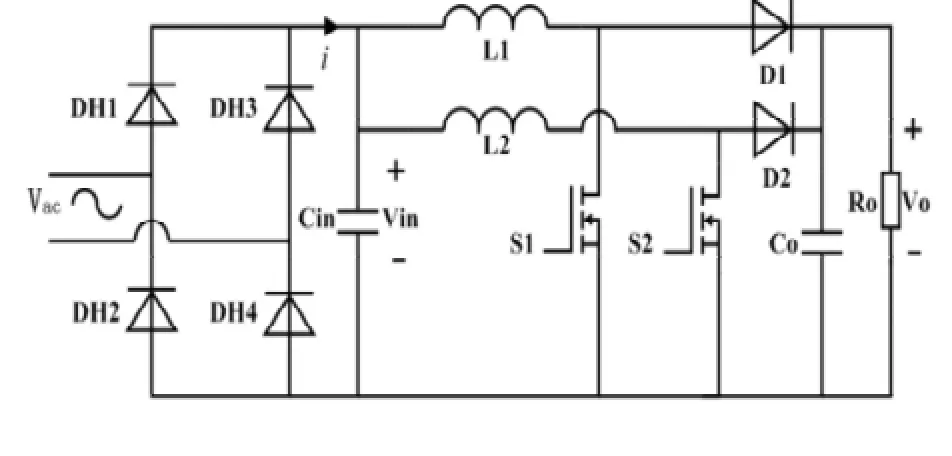

圖1為交錯并聯Boost PFC的工作原理圖,電路結構是兩個對稱并聯的Boost變換器。兩開關管導通時刻依次滯后一定時間,工作在自然交錯狀態,使得流過每個Boost變換器的電流也呈現交錯狀態。這種PFC電路能大大減小輸入電流紋波,提升系統的功率等級。升壓電感是系統輸入與輸出的連接紐帶,充當重要角色,其設計方法的優劣對系統的效率存在較大影響。傳統的電感設計方法存在較大的寄生電容,其對系統效率的影響在高大功率場合是不容忽視的。

圖1交錯并聯Boost PFC拓撲結構

1.2電感設計方法對比分析

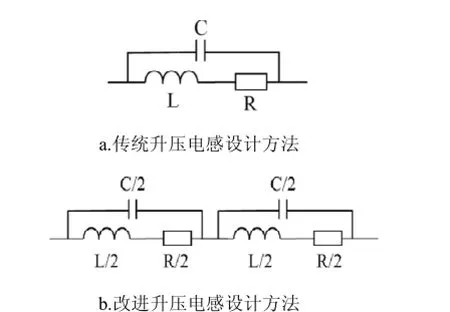

圖2為兩種設計方法的等效模型,可知傳統方法與改進方法所設計的電感總量與內阻均相等,但傳統方法所帶來的寄生電容總量卻是改進方法的4倍。假定輸入電容 Cin電感兩端電壓為 Vin,PFC輸出電壓為Vo,則對于每個Boost變換器有:

圖2兩種設計方法的等效模型

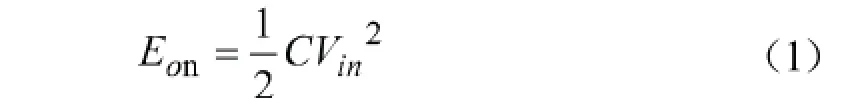

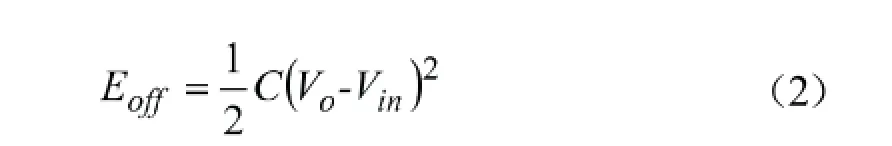

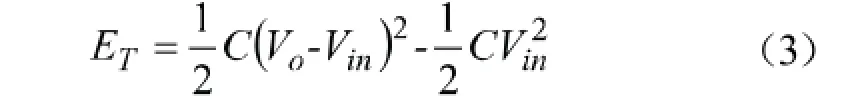

當功率開關管導通時,電感寄生電容C存儲的能量為:

當功率開關管斷開時,電感寄生電容C存儲的能量為:

則一個周期T內,寄生電容C的總損耗為:

由式(3)知傳統方法所帶來的寄生電容損耗是改進方法的4倍,且在輸入電壓越低時能量損耗越多。因此,與傳統方法相比,本文所提出的改進方法具有寄生電容小、損耗低等優點。

1.3電感設計方法

假定交流輸入底線電壓有效值為Vacmin,PFC輸出功率為Po,最低效率要求為,滿載最低開關頻率為Fsw,整流橋二極管正向電壓差為Vbrfd。則可按下式計算出滿足設計要求的最小電感量為:

實際電感的取值應大于(4)式的計算值,式中D為低線輸入電壓下電路的占空比,可按下式進行計算:

2實驗

為驗證上述理論分析與設計的正確性,搭建了一個685W的實驗樣機,前級采用交錯并聯Boost PFC,后級采用Boost升壓加半橋LLC電路,輸出為6路+12V和1路-12V。關鍵元件參數如下:PFC輸出電容Co為390uF;PFC電感取250uH;PFC滿載最低開關工作頻率為 65KHz;二級 Boost電感取160uF;輸出主變壓器原邊感量為1.3mH;諧振電感取8uH。

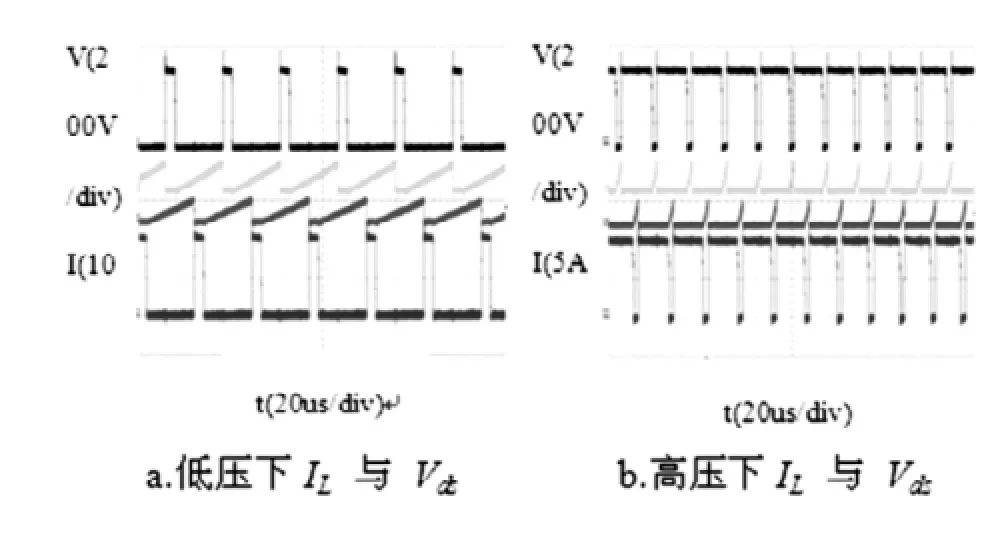

圖3為實驗波形。圖3a與圖3b分別為PFC電路在低壓和高壓下的電感電流與開關管漏源電壓波形。測試結果表明,開關管相互交錯導通,電感電流上升與下降趨勢正好交錯,PFC電路正常工作在自然交錯狀態。圖3c與圖3d為樣機系統在低壓與高壓下的交流輸入電壓、電流波形。測試結果表明,輸入電流能較好地跟蹤輸入電壓,實測低壓時PF值為0.9984,高壓時PF值為0.9736。

圖3實驗波形

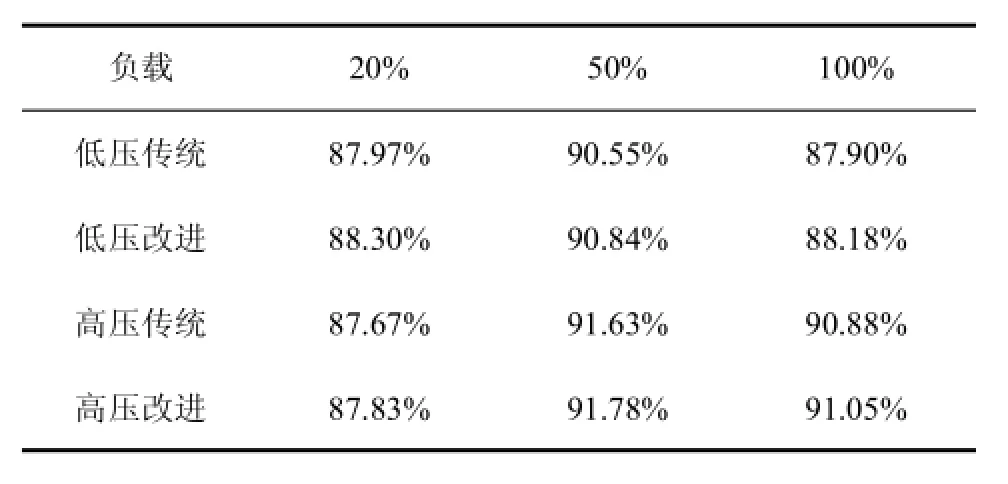

表1為樣機整體效率測試結果,數據是在相同硬件條件下,僅更換PFC電感的基礎上實測的。測試數據表明,低壓下,基于改進方法設計的樣機系統的效率較之傳統方法大約高出0.3個百分點,高壓下大約高出0.15個百分點。因此,本文提出的電感設計方法較之傳統設計方法有較好的效率。

表1樣機效率對比測試結果

3結論

研究了基于交錯并聯技術的BoostPFC變換器,提出了一種升壓電感的改進設計方法,該方法脫離傳統電感的剛性基底模型,理論分析證實該方法較之傳統電感設計方法寄生電容較小、損耗較低。最后制作了一臺685W的含交錯并聯Boost PFC電路的實驗樣機,并在相同硬件條件下進行了實驗測試,實驗證明本文提出的電感改進設計方法較之傳統方法有更高的效率。

參考文獻:

[1]張占松,蔡宣三.開關電源的原理與設計[M].北京:電子工業出版社,2007.

[2]Chan CH,Pong M H.Interleaved Boost Power Factor Corrector Operating in Discontinuous-inductor-Current Mode[A]. Proc of Power Conversion Conference[C].1997,1(8):405-410.

[3]楊玉剛,馬云巧,馬杰.交錯并聯Boost變換器DCM分析及電感設計[J].電力電子技術,2014,48(10):9-11.

[4]陳巍,王國富,張法全,等.一種新型高功率因素電源的設計[J].電源技術與應用,2014,40(11):60-63.

[5]梅寒杰,何樂年.一種新穎的高功率因素PFC的數字控制方法[J].電源技術,2015,39(2):360-362.

[6]OLAYIWOLAA,SOCKB,ZOLGHADRIMRA,etal.Digital controllerfor aBoostPFCconverterin continuous conduction mode[J].IEEE,2006,(5):1-8.

[7]Po-Wa Lee,Yim-Shu Lee,Cheng D K W,et al.Steady-state Analysis of an Interleaved Boost Converter with Coupled Inductors[J].IEEE Trans.on Industrial Electronics,2000,47(4): 787-795.

[8]趙相瑜,袁繼敏,王艷碩.交錯并聯BoostPFC電路的應用研究[J].電力電子技術,2010,44(1):65-67.

[9]楊飛.采用耦合電感的交錯并聯Boost PFC變換器[D].南京:南京航空航天大學,2013.

(責任編輯:朱彬)

A Research into An Interleaved Boost PFC with High Efficiency

YAN Chang-guo,AO Bang-qian,QU Xiang-Jun,LIU Xiao-yong

(Department of Engineering and Technology,Zunyi Normal College,Zunyi 563002,China)

Abstract:The boost inductance is the key components of the interleaved Boost PFC system,and its parasitic capacitance loss will influence the system’s efficiency.Due to the larger parasitic capacitance and the higher loss in traditional Boost inductance,this paper proposes an improved method which has the smaller parasitic capacitance and the lower loss,and designs a 685W prototype system with an interleaved Boost PFC.Compared with the traditional method,the experimental results show that the system with the proposed improved method has a higher efficiency.Thus,this method is more suitable than the traditional one in the high efficient development of the interleaved Boost PFC.

Key words:boost inductance;interleaved Boost PFC;parasitic capacitance;high efficiency

中圖分類號:TM46

文獻標識碼:A

文章編號:1009-3583(2016)-0106-03

收稿日期:2015-10-11

基金項目:貴州省科技廳基金資助項目(黔科合LH字[2015]7054號)

作者簡介:閻昌國,男,貴州遵義人,遵義師范學院工學院講師,碩士,主要從事電力電子技術的控制與應用研究。