社群經(jīng)濟(jì)下社交貨幣對(duì)品牌資產(chǎn)的影響研究

曾宥婕,曲洪建

(上海工程技術(shù)大學(xué) 紡織服裝學(xué)院,上海 201620)

一、引言

20 世紀(jì)末互聯(lián)網(wǎng)的發(fā)展給人類社交提供了層出不窮的平臺(tái)和渠道。基于消費(fèi)者在日常生活中通過互聯(lián)網(wǎng)與品牌之間的互動(dòng)體驗(yàn),Joachimsthaler 等率先提出了社交貨幣(social currency)的概念,指出社交貨幣代表了消費(fèi)者與品牌之間共享的資產(chǎn)[1]。消費(fèi)者可以通過各大媒體和社交平臺(tái)表達(dá)給品牌提建議、與他人分享信息,是公司和品牌相關(guān)信息的“接受者”,也充當(dāng)這些信息的“發(fā)送者”[2]。避免品牌單方宣傳使消費(fèi)者對(duì)品牌的感知形象和態(tài)度走向雙邊化的問題。如今,網(wǎng)絡(luò)社交平臺(tái)如微信、微博、小紅書、b 站等提供及時(shí)傳播和收集品牌信息,衍生了線上品牌社群。Alexander 等(2002)[3]認(rèn)為品牌社群以消費(fèi)者體驗(yàn)為中心,消費(fèi)者與產(chǎn)品、品牌、企業(yè)、其他消費(fèi)者之間存在多樣化關(guān)系。消費(fèi)者在社交平臺(tái)和互聯(lián)網(wǎng)上與企業(yè)進(jìn)行實(shí)時(shí)互動(dòng),參與創(chuàng)作,共同創(chuàng)造品牌價(jià)值。一個(gè)品牌社會(huì)價(jià)值的不同維度取決于社會(huì)資本理論的研究流。社會(huì)資本理論為一般的社會(huì)交往提供了社會(huì)學(xué)基礎(chǔ),涉及群體或個(gè)人之間合作所產(chǎn)生的集體利益。這一理論可以應(yīng)用到如今互聯(lián)網(wǎng)上日益頻繁的社交互動(dòng)中。本文采用Lara 等(2013)[4]人對(duì)社交貨幣的定義:消費(fèi)者與其他人共享品牌或品牌信息,并從與其他品牌用戶的互動(dòng)中獲得社會(huì)效益的程度和方式。

國(guó)內(nèi)外學(xué)者對(duì)于理解和衡量品牌的社會(huì)價(jià)值的相關(guān)研究較多關(guān)注口碑營(yíng)銷、用戶生成內(nèi)容或品牌社區(qū)。然而,這些方法忽視了一個(gè)品牌的社會(huì)價(jià)值的復(fù)雜性,并沒有完全抓住它的多維性。大多數(shù)研究都忽略了消費(fèi)者之間互動(dòng)的交互作用對(duì)品牌資產(chǎn)的促進(jìn)作用。目前的研究還沒有揭示出一個(gè)合適的衡量標(biāo)準(zhǔn)來測(cè)量一個(gè)品牌的社會(huì)價(jià)值及其維度,并將其與成熟的品牌資產(chǎn)衡量方法聯(lián)系起來。為探索消費(fèi)者與品牌的網(wǎng)絡(luò)互動(dòng)性能否與傳統(tǒng)品牌資產(chǎn)測(cè)量相整合,本文歸納社交貨幣維度,構(gòu)建社群經(jīng)濟(jì)下社交貨幣對(duì)品牌資產(chǎn)的影響模型,通過調(diào)查的數(shù)據(jù)實(shí)證社交貨幣的構(gòu)建對(duì)品牌資產(chǎn)的影響,突出其對(duì)品牌整體價(jià)值形成的影響和重要性。并加入品牌體驗(yàn)作為中介變量,檢查消費(fèi)者經(jīng)過線下體驗(yàn)后是否影響其對(duì)品牌原持有的態(tài)度。希望本文能對(duì)企業(yè)營(yíng)銷的制定和品牌資產(chǎn)的完善提供一定理論依據(jù)。

二、相關(guān)概念及維度劃分、研究假設(shè)及模型構(gòu)建

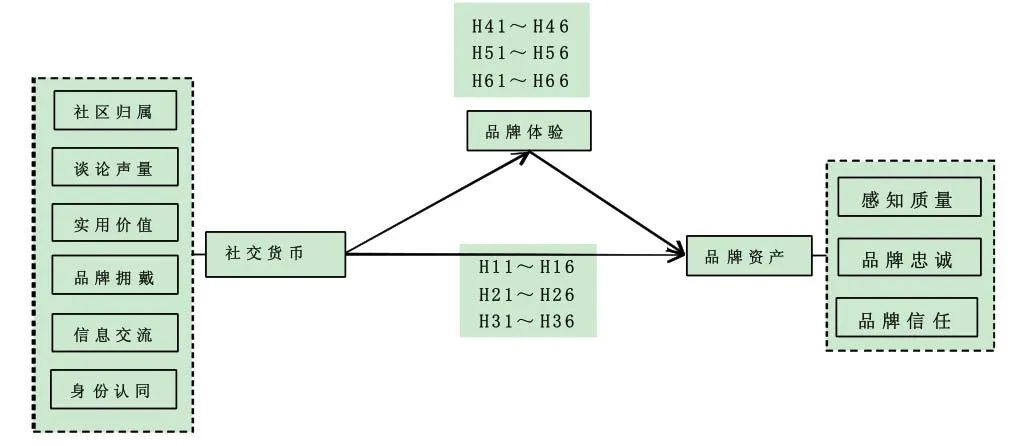

本研究的機(jī)理模型中,自變量和因變量分別為社交貨幣和品牌資產(chǎn),品牌體驗(yàn)為中介變量。目前國(guó)內(nèi)關(guān)于社交貨幣的文獻(xiàn)較少,在現(xiàn)有研究的基礎(chǔ)上,對(duì)品牌社會(huì)貨幣結(jié)構(gòu)進(jìn)行概念化并提出其維度。品牌體驗(yàn)和品牌資產(chǎn)概念較為成熟,在文獻(xiàn)梳理上,采用前人的概念。結(jié)果引出了一個(gè)概念框架,解釋社會(huì)貨幣的多維形成結(jié)構(gòu)、品牌體驗(yàn)與品牌資產(chǎn)的對(duì)應(yīng)關(guān)系。

(一)社交貨幣與品牌資產(chǎn)維度劃分

與其他品牌用戶的互動(dòng)可以創(chuàng)造一種社區(qū)感,這種情感上的依戀或歸屬稱之為社區(qū)歸屬。它可以源于品牌用戶之間不同類型的個(gè)人或非個(gè)人的互動(dòng),如同儕認(rèn)同、直接互動(dòng),甚至是在品牌社群情境下的共同消費(fèi)體驗(yàn)。它也可以起源于其他非結(jié)構(gòu)化的環(huán)境,如通過論壇或在線社交網(wǎng)絡(luò)進(jìn)行的匿名交流[5]。所以,社群歸屬表示消費(fèi)者與品牌其他用戶的情感聯(lián)系,作為品牌社交貨幣的一個(gè)維度;Chevalier和Mayzlin(2006)[6]發(fā)現(xiàn)在互聯(lián)網(wǎng)上客戶之間傳播品牌信息的數(shù)量會(huì)對(duì)客戶對(duì)該品牌的形象和感知產(chǎn)生重大影響。消費(fèi)者接受相關(guān)品牌內(nèi)容的好評(píng)次數(shù)越多,其購(gòu)買該品牌以及向別人推薦的意愿越強(qiáng)烈。因此,談?wù)撀暳孔鳛槠放粕缃回泿诺牡诙S度;將社會(huì)學(xué)研究應(yīng)用到與品牌相關(guān)的顧客互動(dòng)領(lǐng)域。考慮到某些客戶群體之間的互動(dòng)強(qiáng)度和深度,以及其成員之間強(qiáng)烈的歸屬感,本文假設(shè)客戶群體中與品牌相關(guān)的互動(dòng)可以激發(fā)類似的效果,消費(fèi)者可以從互動(dòng)中獲得信息,相關(guān)信息對(duì)消費(fèi)者個(gè)人發(fā)展所造成的影響(如增強(qiáng)自尊)表示為實(shí)用價(jià)值。則實(shí)用價(jià)值作為社會(huì)價(jià)值的一個(gè)維度,是推動(dòng)客戶與他人互動(dòng)的動(dòng)機(jī);如果客戶積極地向其朋友或通過博客、論壇等在線社交網(wǎng)站推廣品牌及其利益,則表明其信任該品牌,從而向他人發(fā)出有關(guān)該品牌品質(zhì)的正向信號(hào)[7]。與談?wù)撀暳浚纯蛻魪钠渌蛻裟抢铽@得的正面品牌信息的數(shù)量)相比,品牌擁戴代表了客戶對(duì)品牌的熱愛態(tài)度。所以將品牌擁戴確定為社會(huì)貨幣的另一維度。顧客之間關(guān)于品牌的交流,特別是各自所共享的內(nèi)容,可以為顧客帶來不同的利益[8]。這些利益包括顧客從分享信息和向他人學(xué)習(xí)中獲得的信息價(jià)值、獲得相關(guān)知識(shí)的容易程度、在解決產(chǎn)品或品牌相關(guān)問題時(shí)獲得相互支持的容易程度[9-10]。因此,把顧客對(duì)顧客交互的信息價(jià)值,作為社會(huì)貨幣的一個(gè)維度。最后,需要考慮的重要問題是客戶如何向一組其他品牌用戶介紹自己。在品牌社群中,品牌用戶可以表達(dá)自己的個(gè)性,并與品牌的其他用戶形成親密感[11]。即使產(chǎn)品處于相同的價(jià)格范圍內(nèi)并且具有相似的特性,由于每個(gè)品牌的用戶所使用的圖像不同,人們對(duì)產(chǎn)品的偏好也存在很大差異[12]。與其他品牌用戶群體或競(jìng)爭(zhēng)品牌的差異有助于加強(qiáng)和強(qiáng)化品牌用戶群體中的共同身份,甚至可能導(dǎo)致對(duì)其他品牌的“對(duì)立品牌忠誠(chéng)”[13]。為了捕捉社交環(huán)境中品牌認(rèn)知的這一重要組成部分,本文將身份認(rèn)同作為社交貨幣的一個(gè)維度。基于以上的分析與歸納,本文將社交貨幣的測(cè)量維度劃分為社區(qū)歸屬、談?wù)撀暳俊?shí)用價(jià)值、品牌擁戴、信息交流和身份認(rèn)同這6 個(gè)維度。

基于web 的客戶交互環(huán)境,Keller(1993)[14]將品牌資產(chǎn)定義為“消費(fèi)者對(duì)品牌信息的差異效應(yīng)所表現(xiàn)的營(yíng)銷反映”。Keller(2010)[15]擴(kuò)展了這一觀點(diǎn),他指出品牌資產(chǎn)不僅受到公司營(yíng)銷努力的影響,還取決于“顧客在一段時(shí)間的經(jīng)歷中對(duì)品牌的了解、感受、所見和所聞”。客戶從與其他客戶的富有成效的交流(即與品牌相關(guān)的互動(dòng))中獲得利益,會(huì)導(dǎo)致對(duì)該品牌的關(guān)系和忠誠(chéng)度的增加[16]。那么這些利益就直接影響顧客的決策。本文采用Lassar 等(1995)[17]對(duì)品牌資產(chǎn)的測(cè)量維度,即感知質(zhì)量、品牌忠誠(chéng)度和品牌信任。

(二)研究假設(shè)及模型構(gòu)建

1.社交貨幣與品牌資產(chǎn)的關(guān)系。感知質(zhì)量可以理解為“消費(fèi)者對(duì)產(chǎn)品或品牌整體卓越性或優(yōu)越性的判斷”[18]。消費(fèi)者在網(wǎng)絡(luò)互動(dòng)中可能直接談?wù)撈放飘a(chǎn)品的質(zhì)量問題,并向他人推薦這個(gè)品牌。Rust 等(1999)[19]認(rèn)為消費(fèi)者通過各種互動(dòng)增加與品牌的接觸,會(huì)積極影響其對(duì)相關(guān)品牌的評(píng)價(jià)。李莉等(2004)[20]發(fā)現(xiàn)質(zhì)量信息的交流和轉(zhuǎn)移方式影響消費(fèi)者對(duì)商品的感知質(zhì)量。因此,做出如下假設(shè):

H11:社區(qū)歸屬對(duì)感知質(zhì)量有正向影響;

H12:談?wù)撀暳繉?duì)感知質(zhì)量有正向影響;

H13:實(shí)用價(jià)值對(duì)感知質(zhì)量有正向影響;

H14:品牌擁戴對(duì)感知質(zhì)量有正向影響;

H15:信息價(jià)值對(duì)感知質(zhì)量有正向影響;

H16:身份認(rèn)同對(duì)感知質(zhì)量有正向影響。

Fournier 和Yao(1997)[21]認(rèn)為消費(fèi)者就相關(guān)品牌的信息和經(jīng)驗(yàn)共享,以及從這些互動(dòng)中獲得的社會(huì)利益,將會(huì)影響他們的品牌忠誠(chéng)度。Schau 等(2009)[22]認(rèn)為消費(fèi)者可能因?yàn)槠渌放朴脩舻耐扑]和交流而對(duì)某品牌產(chǎn)生好感,并與品牌之間的積極聯(lián)系得到確認(rèn)。金立印(2007)[23]經(jīng)過實(shí)證發(fā)現(xiàn)品牌社群的社交價(jià)值、信息價(jià)值能提升社群成員的忠誠(chéng)度,社群意識(shí)(即社區(qū)歸屬感)較強(qiáng)的成員對(duì)社群比較忠誠(chéng),具有保護(hù)品牌聲譽(yù)(即品牌擁戴)的積極意向,同時(shí)對(duì)于競(jìng)爭(zhēng)品牌也會(huì)表現(xiàn)出較高的抵制傾向。王新新和薛海波(2010)[24]認(rèn)社會(huì)資本存在于品牌社群中,它隨自愿、互惠、信任及內(nèi)部語言的增強(qiáng)而增強(qiáng);消費(fèi)者在品牌社群中可獲得信息價(jià)值和社會(huì)價(jià)值,這有助于其形成品牌社群承諾和品牌忠誠(chéng)。靳代平等(2016)[25]研究發(fā)現(xiàn),粉絲是通過和信息、產(chǎn)品、事件以及粉絲之間的互動(dòng)行為創(chuàng)造了價(jià)值(功能價(jià)值、享樂價(jià)值和心靈價(jià)值),進(jìn)而,他們通過功能價(jià)值和享樂價(jià)值的創(chuàng)造來獲取自我認(rèn)同,通過心靈價(jià)值的創(chuàng)造獲得了身份認(rèn)同,從而對(duì)品牌產(chǎn)生忠誠(chéng)和心靈上的歸屬感,因此,做出如下假設(shè):

H21:社區(qū)歸屬對(duì)品牌忠誠(chéng)有正向影響;

H22:談?wù)撀暳繉?duì)品牌忠誠(chéng)有正向影響;

H23:實(shí)用價(jià)值對(duì)品牌忠誠(chéng)有正向影響;

H24:品牌擁戴對(duì)品牌忠誠(chéng)有正向影響;

H25:信息交流對(duì)品牌忠誠(chéng)有正向影響;

H26:身份認(rèn)同對(duì)品牌忠誠(chéng)有正向影響。

顧客對(duì)品牌的信任程度,很大程度上取決于顧客與顧客的互動(dòng)中所接收到的與品牌相關(guān)的信息,以及顧客與相關(guān)品牌本身所建立的關(guān)系[26]。顧客將自己與相應(yīng)的品牌和其他品牌的用戶等同起來,消費(fèi)者會(huì)降低對(duì)品牌的風(fēng)險(xiǎn)感知,從而在更大程度上信任品牌[27]。金玉芳等(2006)[28]從關(guān)系營(yíng)銷角度出發(fā),研究發(fā)現(xiàn)消費(fèi)者所感知的經(jīng)濟(jì)價(jià)值越高,對(duì)品牌的表現(xiàn)能力和誠(chéng)信善良的信任程度越高,因此,做出如下假設(shè):

H31:社區(qū)歸屬對(duì)品牌信任有正向影響;

H32:談?wù)撀暳繉?duì)品牌信任有正向影響;

H33:實(shí)用價(jià)值對(duì)品牌信任有正向影響;

H34:品牌擁戴對(duì)品牌信任有正向影響;

H35:信息價(jià)值對(duì)品牌信任有正向影響;

H36:身份認(rèn)同對(duì)品牌信任有正向影響。

2.社交貨幣、品牌體驗(yàn)與品牌資產(chǎn)的關(guān)系。李啟庚和余明陽(2011)[29]將品牌體驗(yàn)價(jià)值劃分為感官體驗(yàn)價(jià)值和情感體驗(yàn)價(jià)值,實(shí)證發(fā)現(xiàn)品牌體驗(yàn)價(jià)值對(duì)品牌資產(chǎn)具有廣泛的、較強(qiáng)的影響力和較高的解釋力。感官體驗(yàn)價(jià)值是基于產(chǎn)品的外觀、功能和性能的感官和審美價(jià)值獲取,較高的感官體驗(yàn)價(jià)值依賴于產(chǎn)品的屬性,而感官體驗(yàn)價(jià)值的獲取也會(huì)增強(qiáng)消費(fèi)者對(duì)品牌產(chǎn)品質(zhì)量的評(píng)價(jià)[30]。消費(fèi)者對(duì)品牌產(chǎn)品進(jìn)行交流互動(dòng)時(shí),其情感與其喚醒水平具有很大的關(guān)系[31]。較高的喚醒水平下,消費(fèi)者思維清晰、對(duì)周圍事物感興趣,此時(shí)容易感知到品牌的相關(guān)特征。吳水龍等(2009)[32]發(fā)現(xiàn)品牌體驗(yàn)對(duì)品牌忠誠(chéng)有正向作用,并更多是通過品牌社區(qū)對(duì)其產(chǎn)生更大影響。楊德鋒等(2014)[33]發(fā)現(xiàn)參與性互動(dòng)、分享性互動(dòng)、知識(shí)性互動(dòng)和創(chuàng)造性互動(dòng)可以促進(jìn)個(gè)人修養(yǎng)、道德倫理和人際關(guān)系等代際文化價(jià)值觀念的傳遞,形成功能性體驗(yàn)、情感性體驗(yàn)和社會(huì)性體驗(yàn),進(jìn)而促進(jìn)顧客的品牌忠誠(chéng)。許正良和古安偉(2011)[34]基于關(guān)系視角發(fā)現(xiàn)設(shè)計(jì)優(yōu)異的品牌體驗(yàn),在直接驅(qū)動(dòng)品牌忠誠(chéng)的同時(shí),促使消費(fèi)者形成品牌信任和品牌依戀,產(chǎn)生忠誠(chéng)行為,提升品牌資產(chǎn)。由此,做出如下假設(shè):

H41:社區(qū)歸屬通過品牌體驗(yàn)對(duì)感知質(zhì)量有正向影響;

H42:談?wù)撀暳客ㄟ^品牌體驗(yàn)對(duì)感知質(zhì)量有正向影響;

H43:實(shí)用價(jià)值通過品牌體驗(yàn)對(duì)感知質(zhì)量有正向影響;

H44:品牌擁戴通過品牌體驗(yàn)對(duì)感知質(zhì)量有正向影響;

H45:信息價(jià)值通過品牌體驗(yàn)對(duì)感知質(zhì)量有正向影響;

H46:身份認(rèn)同通過品牌體驗(yàn)對(duì)感知質(zhì)量有正向影響。

H51:社區(qū)歸屬通過品牌體驗(yàn)對(duì)品牌忠誠(chéng)有正向影響;

H52:談?wù)撀暳客ㄟ^品牌體驗(yàn)對(duì)品牌忠誠(chéng)有正向影響;

H53:實(shí)用價(jià)值通過品牌體驗(yàn)對(duì)品牌忠誠(chéng)有正向影響;

H54:品牌擁戴通過品牌體驗(yàn)對(duì)品牌忠誠(chéng)有正向影響;

H55:信息交流通過品牌體驗(yàn)對(duì)品牌忠誠(chéng)有正向影響;

H56:身份認(rèn)同通過品牌體驗(yàn)對(duì)品牌忠誠(chéng)有正向影響。

H61:社區(qū)歸屬通過品牌體驗(yàn)對(duì)品牌信任有正向影響;

H62:談?wù)撀暳客ㄟ^品牌體驗(yàn)對(duì)品牌信任有正向影響;

H63:實(shí)用價(jià)值通過品牌體驗(yàn)對(duì)品牌信任有正向影響;

H64:品牌擁戴通過品牌體驗(yàn)對(duì)品牌信任有正向影響;

H65:信息價(jià)值通過品牌體驗(yàn)對(duì)品牌信任有正向影響;

H66:身份認(rèn)同通過品牌體驗(yàn)對(duì)品牌信任有正向影響。

(三)邏輯模型構(gòu)建

圖1 理論模型

三、研究方法

(一)變量的選擇和測(cè)度

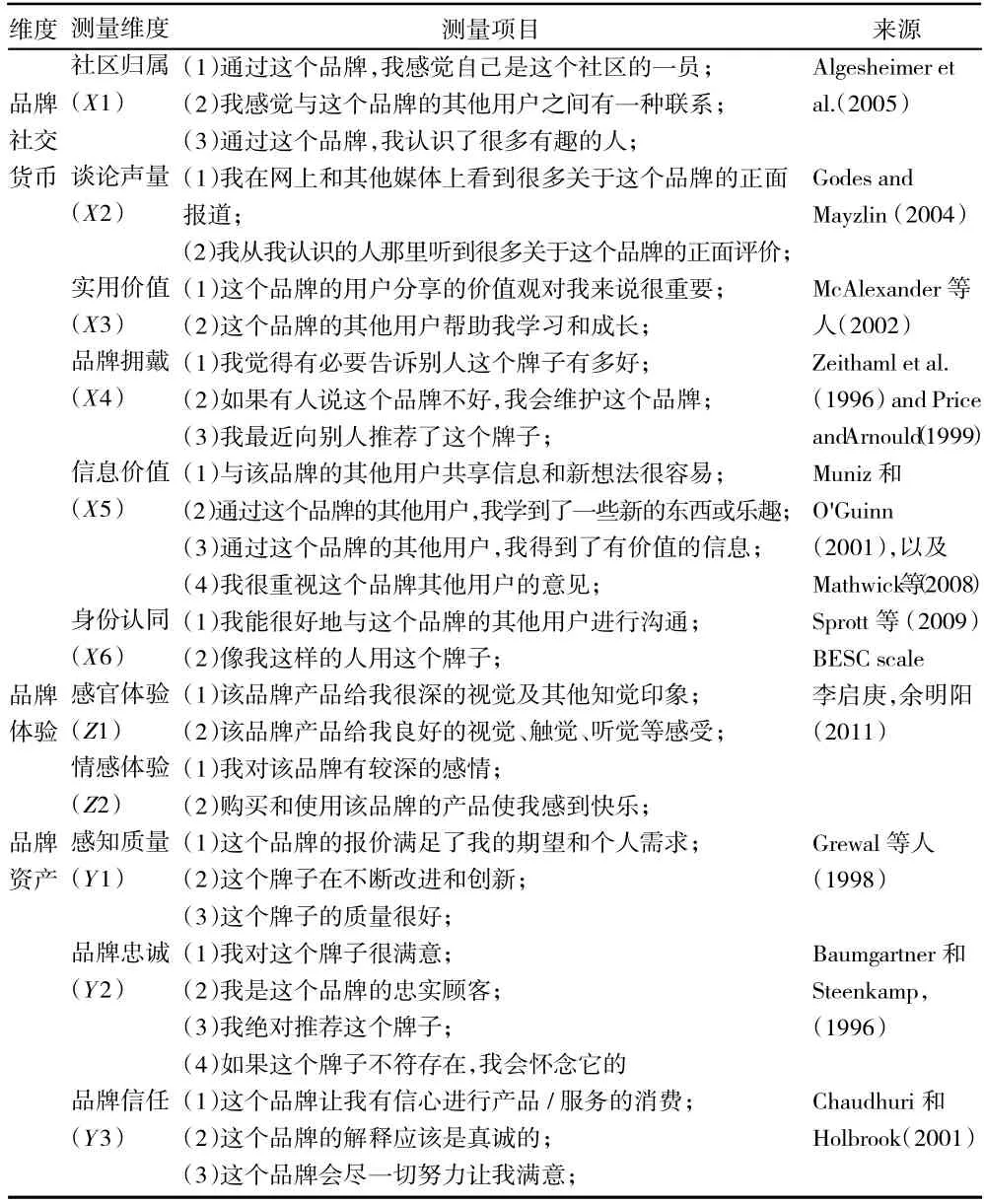

本文研究的關(guān)鍵變量共有11 個(gè),分別為:社區(qū)歸屬、談?wù)撀暳俊?shí)用價(jià)值、品牌擁戴、信息交流、身份認(rèn)同、感官體驗(yàn)、情感體驗(yàn)、感知質(zhì)量、品牌忠誠(chéng)、品牌信任。為了獲得良好的信度和效度,本文研究變量的測(cè)量指標(biāo)均來源于國(guó)內(nèi)外相關(guān)文獻(xiàn)。測(cè)量指標(biāo)和參照來源如表1 所示。

表1 測(cè)量指標(biāo)和參考來源

(二)研究取樣

本研究均采用李克特五級(jí)量表進(jìn)行變量測(cè)度,5 表示很同意,4 表示同意,3 表示一般,2 表示不同意,1 表示很不同意。本研究主要篩選活躍于各大社交平臺(tái)的消費(fèi)群體為調(diào)研對(duì)象,通過線上、線下發(fā)放調(diào)研問卷244 份,最終實(shí)際有效問卷232,達(dá)到95.1%問卷有效率。

(三)描述性統(tǒng)計(jì)分析

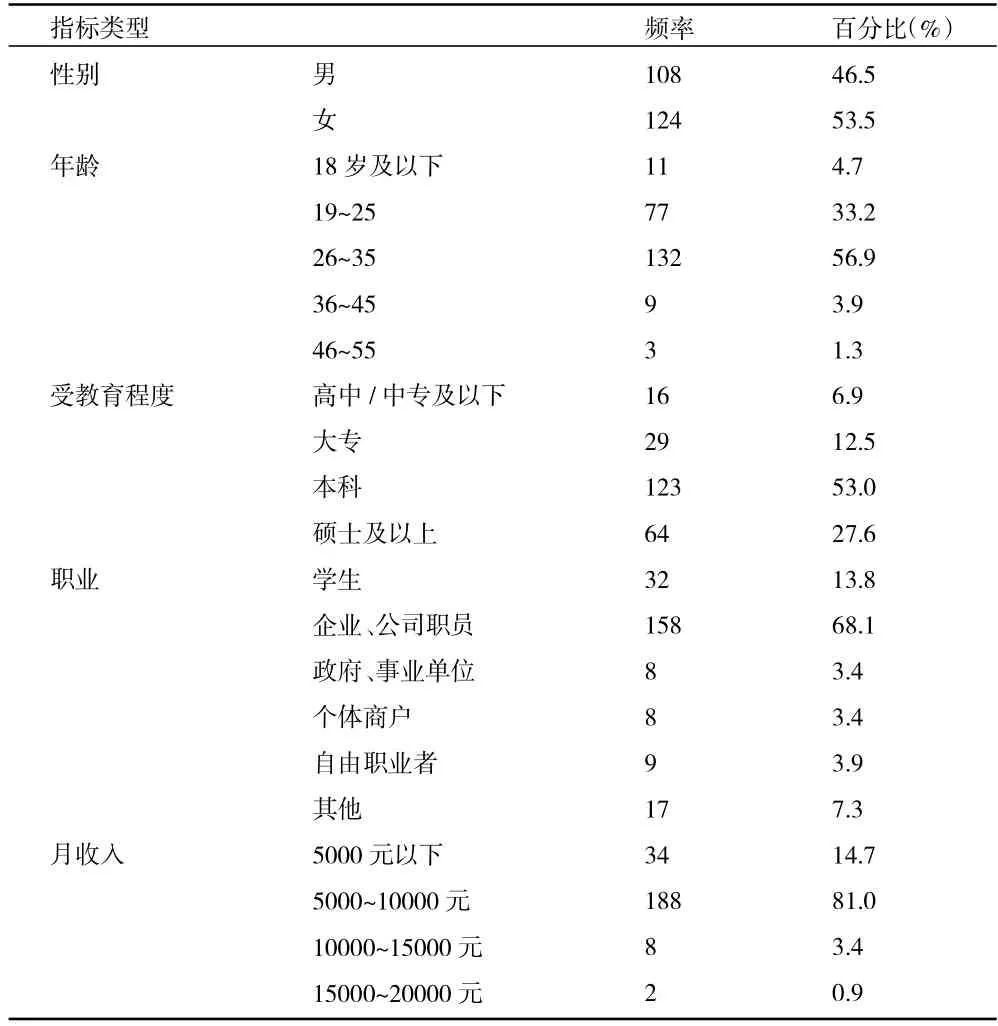

樣本性別、年齡分布、受教育程度和職業(yè)及月收入等統(tǒng)計(jì)指標(biāo)如表2 所示。

表2 樣本描述性統(tǒng)計(jì)

由表2 可知,在232 個(gè)被測(cè)樣本中,女性占人數(shù)的53.5%,男性占人數(shù)的46.5%,男女占比較為均衡;在年齡分布上,被測(cè)人數(shù)占比最大在26~35 歲,其次是19~25 歲,基本符合本調(diào)研活躍于社交平臺(tái)的年輕群體的樣本要求;在學(xué)歷方面,本科學(xué)歷在其中占比53.0%;在職業(yè)分布上,企業(yè)、公司職員占比最多,其次是學(xué)生;在月收入方面,5000~10000 元占比最多,其次是5 000 元以下,被調(diào)查群體的收入較高,且群體較為年輕,快速接受新興事物且快速習(xí)得能力較強(qiáng),消費(fèi)觀念較為開放,對(duì)商品消費(fèi)有自己的見解,可以真實(shí)客觀地反映調(diào)研需要。樣本整體較為符合預(yù)期,可以進(jìn)行后續(xù)的數(shù)據(jù)分析。

(四)信度和效度檢驗(yàn)

1.信度檢驗(yàn)

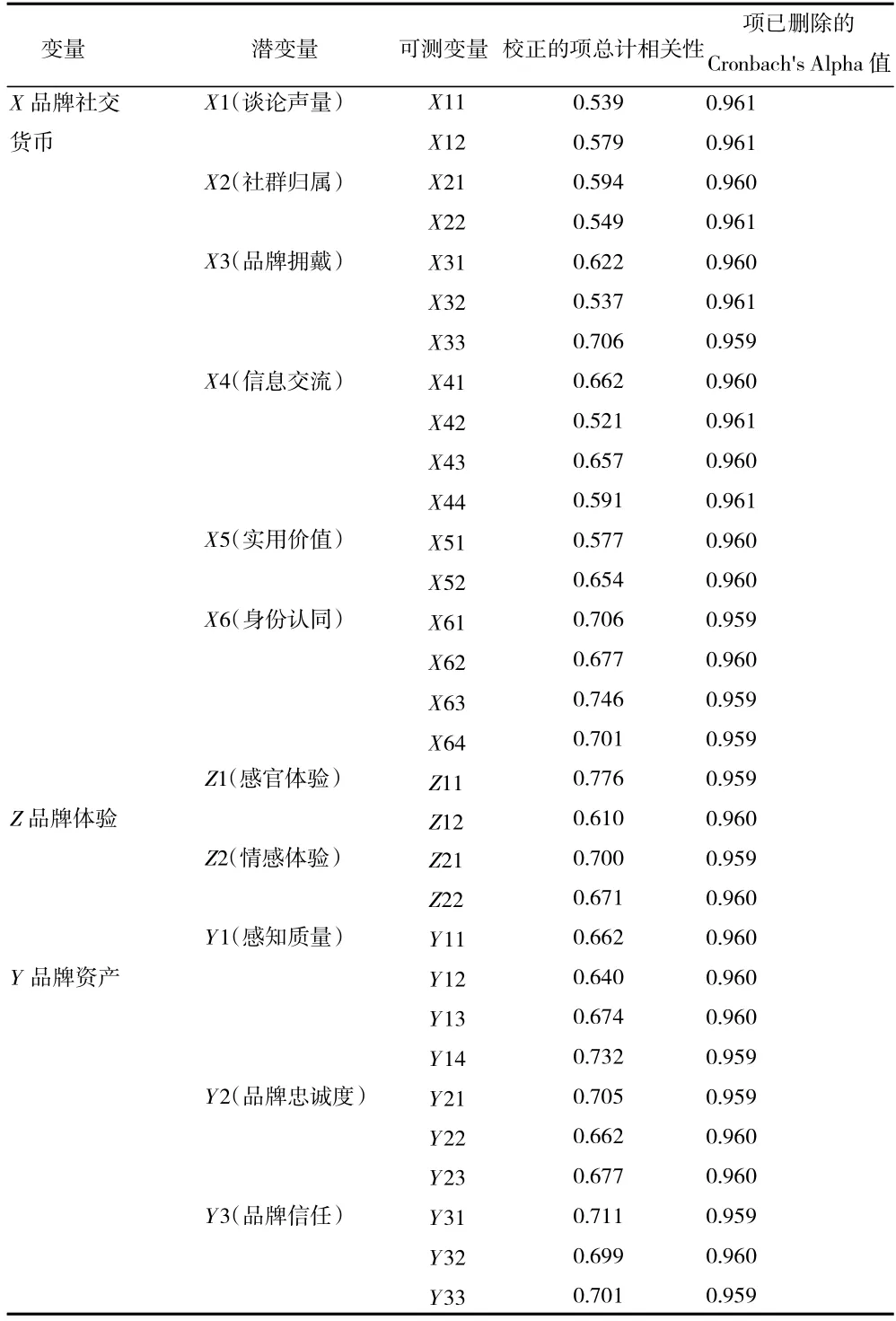

對(duì)量表進(jìn)行信度檢驗(yàn)后結(jié)果如表3 所示。由表3 可知,社區(qū)歸屬、談?wù)撀暳俊?shí)用價(jià)值、品牌擁戴、信息交流、身份認(rèn)同、感官體驗(yàn)、情感體驗(yàn)、感知質(zhì)量、品牌忠誠(chéng)和品牌信任的Alpha 值均達(dá)到大于0.900,表明研究數(shù)據(jù)信度質(zhì)量良好,且刪除某項(xiàng)后的Alpha 值沒有明顯的提升,“各項(xiàng)—總量修正系數(shù)”均大于標(biāo)準(zhǔn)值0.5,綜合說明數(shù)據(jù)信度質(zhì)量良好。

表3 信度分析

2.效度分析

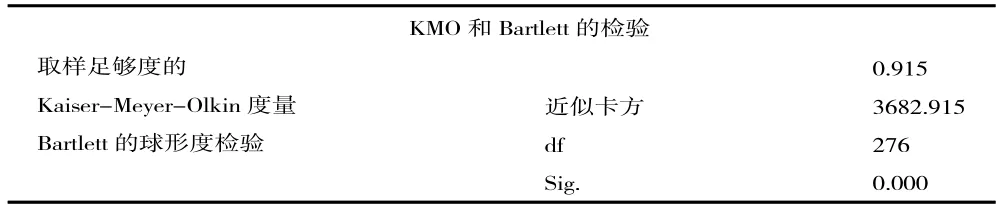

樣本數(shù)據(jù)采用探索性因子分析檢驗(yàn)問卷的結(jié)構(gòu)效度,由表4 可知KMO 度量值為0.915,大于0.8,說明社交貨幣量表數(shù)據(jù)非常適合做因子分析,Bartlett 的球形度檢驗(yàn)近似卡方值為3 682.915,自由度為276,P值為0.000,小于0.001,通過顯著水平為1%的顯著性檢驗(yàn),由此可知品牌社交貨幣量表數(shù)據(jù)非常適合做因子分析。

表4 效度分析

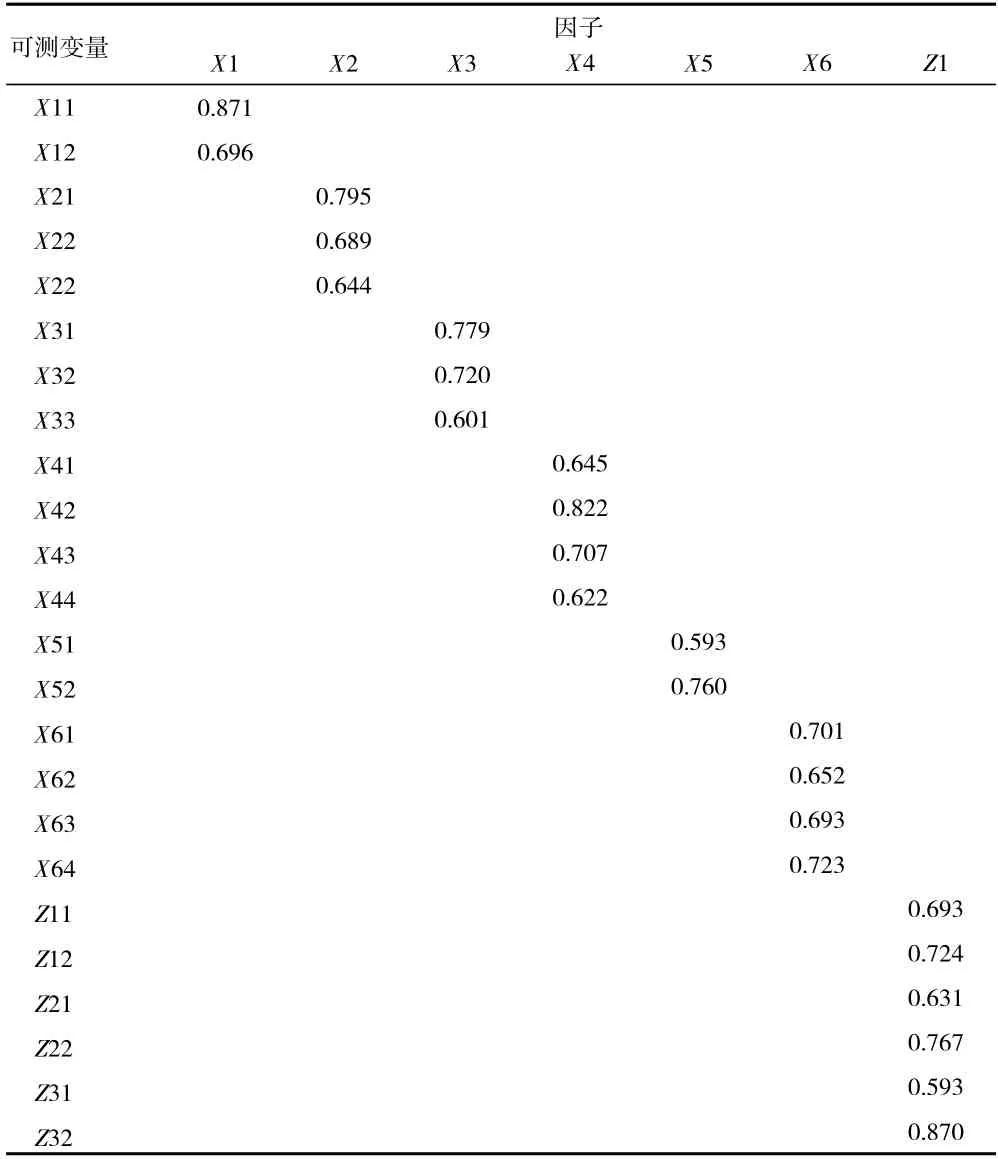

通過驗(yàn)證性因子分析方法獲取各量表?xiàng)l目的因子載荷范圍處在0.5~0.9,均大于最低要求0.500。分析結(jié)果表明,該問卷數(shù)據(jù)具有較好的結(jié)構(gòu)效度和收斂效度。因此,可以進(jìn)行后續(xù)的回歸分析,來驗(yàn)證社交貨幣影響因子與品牌體驗(yàn)、品牌資產(chǎn)的因果關(guān)系。

四、實(shí)證研究結(jié)果分析

(一)社交貨幣對(duì)感知質(zhì)量、品牌忠誠(chéng)、品牌信任的回歸分析

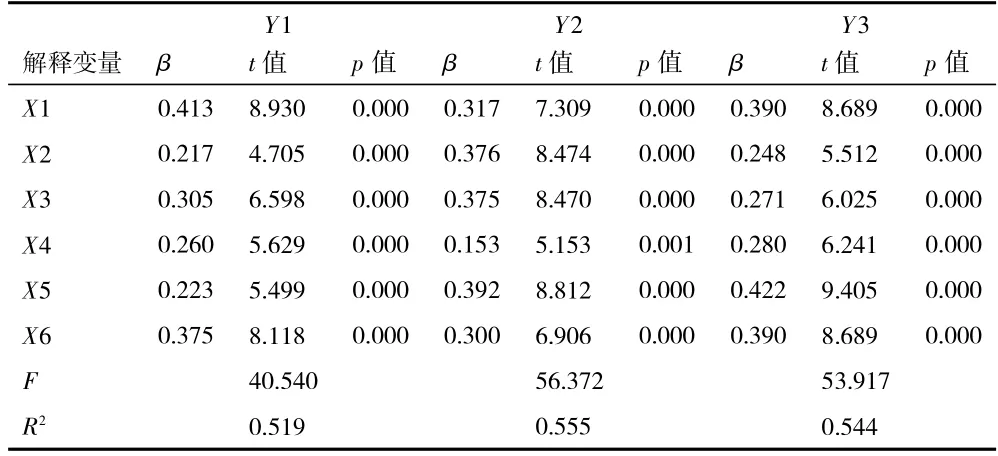

以談?wù)撀暳俊⑸缛簹w屬、品牌擁戴、信息交流、實(shí)用價(jià)值、身份認(rèn)同為自變量,分別以感知質(zhì)量、品牌忠誠(chéng)、品牌信任為因變量,通過多元回歸分析,結(jié)果如表5 所示。由表6 可知,P值均小于0.050,顯著性檢驗(yàn)通過;其中Γ值分別為40.540、56.372、53.917,表明回歸方程自變量和因變量之間存在良好的線性關(guān)系;Γ2的值為0.519、0.555、0.544,表明回歸方程具有較好的擬合優(yōu)度,社交貨幣分別與感知質(zhì)量、品牌忠誠(chéng)、品牌信任有相關(guān)性,且標(biāo)準(zhǔn)系數(shù)均為正,說明自變量與因變量之間存在正向相關(guān)關(guān)系。因此,假設(shè)H11、H12、H13、H14、H15、H16、H21、H22、H23、H24、H25、H26、H31、H32、H33、H34、35、36 得到驗(yàn)證。

表5 因子分析結(jié)果

表6 社交貨幣對(duì)感知質(zhì)量、品牌忠誠(chéng)、品牌信任的回歸分析結(jié)果

(二)品牌體驗(yàn)的中介效應(yīng)檢驗(yàn)

以品牌體驗(yàn)為中介變量的回歸分析可分為3步進(jìn)行:

(1)分別測(cè)量社交貨幣、品牌體驗(yàn)與感知質(zhì)量、品牌忠誠(chéng)度、品牌信任的關(guān)系,其結(jié)果都應(yīng)該顯著;

(2)測(cè)量品牌社交貨幣與品牌體驗(yàn)的關(guān)系,其結(jié)果應(yīng)該顯著;

(3)將品牌社交貨幣與品牌體驗(yàn)同時(shí)帶入回歸方程,測(cè)量二者與品牌感知質(zhì)量、品牌忠誠(chéng)度、品牌信任的關(guān)系,若測(cè)得的t值比(1)的值小,且不顯著,表示存在完全中介效應(yīng),顯著,則表示存在部分中介效應(yīng)。

1.社交貨幣對(duì)品牌體驗(yàn)、感知質(zhì)量、品牌忠誠(chéng)度、品牌信任的回歸分析。由表6 的數(shù)據(jù)可知,社交貨幣6 個(gè)維度對(duì)感知質(zhì)量、品牌忠誠(chéng)度、品牌信任存在顯著正向影響。以談?wù)撀暳俊⑸缛簹w屬、品牌擁戴、信息交流、實(shí)用價(jià)值、身份認(rèn)同為自變量,品牌體驗(yàn)為因變量,通過多元回歸分析。

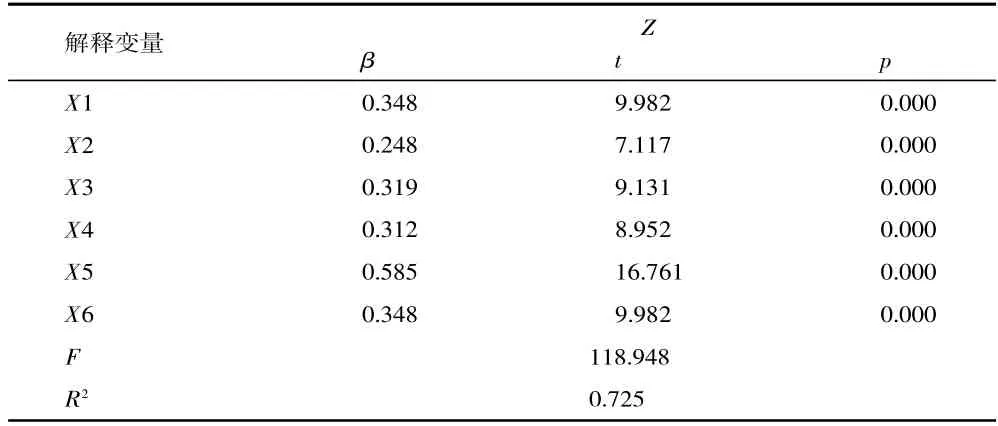

得到對(duì)比分析結(jié)果如表7 所示。P值均小于0.01,其中Γ值為118.948,說明回歸方程中自變量和因變量之間的線性關(guān)系顯著;且標(biāo)準(zhǔn)系數(shù)均為正,說明自變量與因變量之間存在顯著相關(guān)關(guān)系;Γ2的值為0.725,表明回歸方程具有較好的擬合優(yōu)度,自變量對(duì)因變量的解釋程度較高。因此,談?wù)撀暳俊⑸缛簹w屬、品牌擁戴、信息交流、實(shí)用價(jià)值、身份認(rèn)同均正向影響品牌體驗(yàn)。

表7 社交貨幣對(duì)品牌體驗(yàn)的回歸分析

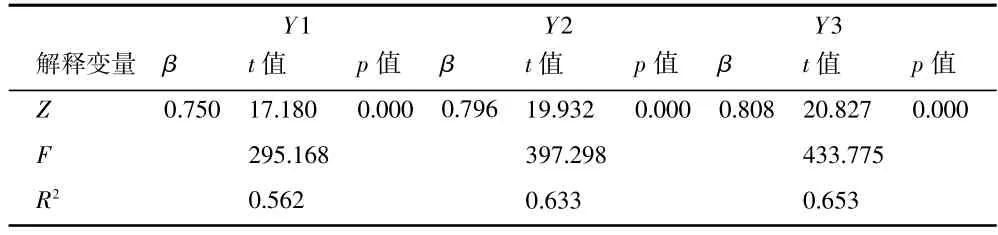

2.品牌體驗(yàn)對(duì)感知質(zhì)量、品牌忠誠(chéng)、品牌信任的回歸分析。由表7 可知,品牌體驗(yàn)對(duì)感知質(zhì)量正向影響顯著(β=0.750,Γ=0.000<0.05),即品牌體驗(yàn)正向影響品牌感知質(zhì)量;品牌體驗(yàn)對(duì)品牌忠誠(chéng)的影響系數(shù)為0.796,Γ值為0.000,說明品牌體驗(yàn)對(duì)品牌忠誠(chéng)正向影響顯著,即品牌體驗(yàn)正向影響奢侈品的購(gòu)買意愿品牌忠誠(chéng)度;品牌體驗(yàn)對(duì)品牌信任的影響系數(shù)為0.808,Γ值為0.000,說明品牌體驗(yàn)對(duì)品牌信任正向影響顯著,即品牌體驗(yàn)正向影響奢侈品的購(gòu)買意愿品牌信任。

表8 品牌體驗(yàn)對(duì)感知質(zhì)量、品牌忠誠(chéng)、品牌信任的回歸分析結(jié)果

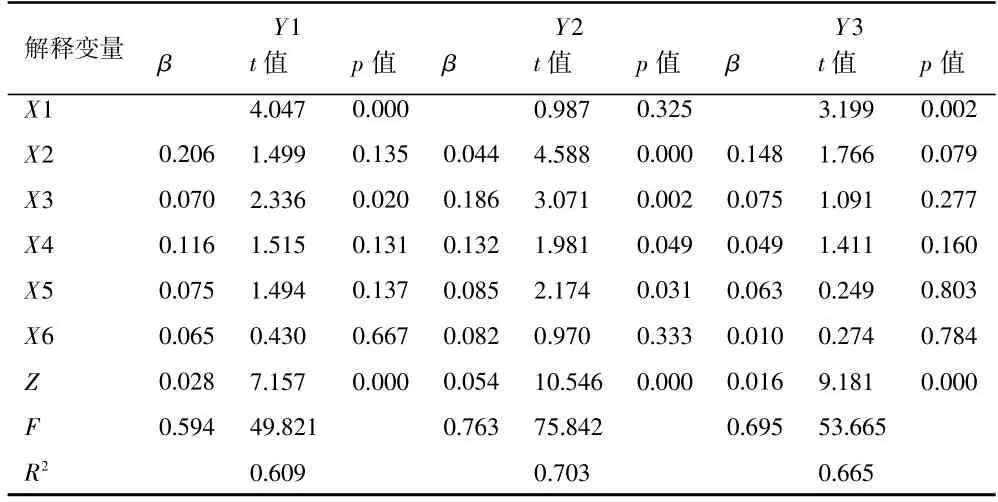

3.社交貨幣與品牌體驗(yàn)對(duì)感知質(zhì)量、品牌忠誠(chéng)度、品牌信任回歸分析。以談?wù)撀暳俊⑸缛簹w屬、品牌擁戴、信息價(jià)值、實(shí)用價(jià)值、身份認(rèn)同和品牌體驗(yàn)為自變量,分別以品牌感知質(zhì)量、品牌忠誠(chéng)度、品牌信任為因變量,通過多元回歸分析,得到對(duì)比分析結(jié)果如表9 所示。

表9 社交貨幣與品牌體驗(yàn)對(duì)感知質(zhì)量、品牌忠誠(chéng)度、品牌信任的回歸分析結(jié)果

談?wù)撀暳浚é?0.206,P=0.000<0.05)、品牌擁戴(β=0.116,P=0.020<0.05)與品牌體驗(yàn)對(duì)感知質(zhì)量有正向影響;社群歸屬、信息交流、實(shí)用價(jià)值、身份認(rèn)同與品牌體驗(yàn)的P值均>0.050,說明其對(duì)感知質(zhì)量的影響不顯著。

社群歸屬(β=0.186,P=0.000<0.05)、品牌擁戴(β=0.132,P=0.002<0.05)、信息價(jià)值(β=0.085,P=0.000<0.049)、實(shí)用價(jià)值(β=0.082,P=0.031<0.05)和品牌體驗(yàn)對(duì)品牌忠誠(chéng)存在正向影響;談?wù)撀暳俊⑸矸菡J(rèn)同和品牌體驗(yàn)的P值均>0.050,說明其對(duì)品牌忠誠(chéng)的影響不顯著。

談?wù)撀暳浚é?0.148,P=0.002<0.05)與品牌體驗(yàn)對(duì)品牌信任有正向影響;社群歸屬、品牌擁戴、信息價(jià)值、實(shí)用價(jià)值、身份認(rèn)同和品牌體驗(yàn)的P值均>0.050,說明其對(duì)品牌忠誠(chéng)的沒有顯著影響。

綜合表6~表9 的分析,談?wù)撀暳浚╔1)、品牌擁戴(X3)通過品牌體驗(yàn)對(duì)感知質(zhì)量有正向影響,假設(shè)H41、H43 得到驗(yàn)證。其中,品牌體驗(yàn)在談?wù)撀暳俊⑵放茡泶髋c感知質(zhì)量之間存在部分中介作用,品牌體驗(yàn)在社群歸屬、信息價(jià)值、實(shí)用價(jià)值、身份認(rèn)同與感知質(zhì)量之間起完全中介作用。

社群歸屬、品牌擁戴、信息價(jià)值、實(shí)用價(jià)值通過品牌體驗(yàn)對(duì)品牌忠誠(chéng)存在正向影響,假設(shè)H52、H53、H54、H55 得到驗(yàn)證。其中品牌體驗(yàn)在社群歸屬、品牌擁戴、信息價(jià)值、實(shí)用價(jià)值與品牌忠誠(chéng)有部分中介作用,品牌體驗(yàn)在談?wù)撀暳俊⑸矸菡J(rèn)同與品牌忠誠(chéng)之間起完全中介作用。

談?wù)撀暳客ㄟ^品牌體驗(yàn)對(duì)品牌信任存在正向影響,假設(shè)H61 得到驗(yàn)證。其中品牌體驗(yàn)在談?wù)撀暳颗c品牌信任之間有部分中介作用,品牌體驗(yàn)在社群歸屬、品牌擁戴、信息價(jià)值、實(shí)用價(jià)值、身份認(rèn)同與品牌忠誠(chéng)之間存在完全中介作用。

由表6 可知,社交貨幣各維度對(duì)消費(fèi)者感知質(zhì)量的影響大小排序如下:談?wù)撀暳浚é?0.413)>身份認(rèn)同(β=0.375)>品牌擁戴(β=0.305)>信息價(jià)值(β=0.260)>社群歸屬(β=0.217)>實(shí)用價(jià)值(β=0.023)。社交貨幣各維度對(duì)消費(fèi)者品牌忠誠(chéng)的影響大小排序如下:實(shí)用價(jià)值(β=0.392)>社群歸屬(β=0.376)>品牌擁戴(β=0.375)>談?wù)撀暳浚é?0.309)=身份認(rèn)同(β=0.309)>信息價(jià)值(β=0.153)。社交貨幣各維度對(duì)消費(fèi)者品牌信任的影響大小排序如下:實(shí)用價(jià)值(β=0.422)>談?wù)撀暳浚é?0.390)=身份認(rèn)同(β=0.390)>信息價(jià)值(β=0.280)>品牌擁戴(β=0.271)>社群歸屬(β=0.248)。

五、對(duì)策建議

本研究基于理論分析的基礎(chǔ)上,提出社交貨幣的概念,并從社會(huì)學(xué)、經(jīng)濟(jì)學(xué)、營(yíng)銷管理等領(lǐng)域總結(jié)出社交貨幣的6 個(gè)維度,總結(jié)運(yùn)用其他學(xué)者的量表開發(fā)出適合國(guó)內(nèi)消費(fèi)的社交貨幣測(cè)量量表。基于此,構(gòu)建社交貨幣與品牌體驗(yàn)對(duì)品牌資產(chǎn)的影響模型,通過因子分析和回歸分析法,得到主要結(jié)論和啟示如下:

(1)社交貨幣層面。社交貨幣對(duì)品牌資產(chǎn)具有廣泛的影響力和較高的解釋力,社交貨幣應(yīng)當(dāng)作為基于顧客的品牌資產(chǎn)研究的重要前因納入相關(guān)研究中,具體分析品牌體驗(yàn)價(jià)值各維度的影響作用。首先值得研究者和管理員注意的是,實(shí)用價(jià)值對(duì)品牌忠誠(chéng)和品牌信任有強(qiáng)勁的影響力,其對(duì)兩者的影響力居于其他影響因素之首,說明品牌用戶之間共享產(chǎn)品特征等信息有利于增強(qiáng)消費(fèi)者的品牌忠誠(chéng)和品牌信任。其次值得指出的是,談?wù)撀暳繉?duì)消費(fèi)者感知質(zhì)量的影響最大,同時(shí)對(duì)品牌忠誠(chéng)和品牌信任也有較高的影響力,品牌用戶就品牌相關(guān)問題在網(wǎng)絡(luò)上談?wù)撛蕉唷⑸⒉荚綇V,品牌用戶以及潛在用戶越容易獲取信息,關(guān)于品牌的正向評(píng)論越多,越能獲取消費(fèi)者的信賴。而且不難發(fā)現(xiàn),身份認(rèn)同與談?wù)撀暳繉?duì)品牌忠誠(chéng)和品牌信任影響力一致,對(duì)感知質(zhì)量的影響力僅次于談?wù)撀暳浚放葡M(fèi)者之間互動(dòng)越多,接收相關(guān)信息越多,用戶們的認(rèn)同感越強(qiáng)。由于社交貨幣各維度對(duì)品牌資產(chǎn)各維度的影響力具有差異,營(yíng)銷管理人員應(yīng)當(dāng)根據(jù)不同的影響目的,從消費(fèi)者的不同體驗(yàn)價(jià)值考慮如何有效地實(shí)現(xiàn)最佳的影響效果,提升品牌資產(chǎn)。

(2)商品層面。傳統(tǒng)的完整產(chǎn)品信息介紹必不可少,但在信息“速食”的互聯(lián)網(wǎng)時(shí)代,產(chǎn)品信息的易解讀性和趣味性至關(guān)重要。營(yíng)銷管理者需要選擇性突出產(chǎn)品的主要特征,讓消費(fèi)者或消費(fèi)者在互動(dòng)中更易獲取信息的實(shí)用價(jià)值,了解產(chǎn)品。信息的趣味性更能激發(fā)消費(fèi)者交流動(dòng)機(jī),利于信息的傳播,擴(kuò)大產(chǎn)品信息的影響力。

(3)口碑營(yíng)銷層面。首先需要確保參考群體的正面評(píng)價(jià)質(zhì)量,消費(fèi)者對(duì)產(chǎn)品的認(rèn)識(shí)和了解除了來自網(wǎng)站的信息描述以外,大部分來自參考群體或意見領(lǐng)袖,比如現(xiàn)在流行的主播、小紅書博主、b 站up主、知乎熱評(píng)者、抖音紅人等。參考群體的影響力可以吸引用戶關(guān)注、激發(fā)關(guān)于產(chǎn)品信息的交流互動(dòng),提高正面信息的討論聲量,同時(shí)其權(quán)威性能減少消費(fèi)者擔(dān)憂風(fēng)險(xiǎn)問題。參考群體表現(xiàn)出對(duì)某品牌的擁戴,更易獲得消費(fèi)者的信賴感和認(rèn)同感。其次,增大各社交平臺(tái)的正面談?wù)撀暳浚ヂ?lián)網(wǎng)信息傳播的滾動(dòng)式疊加效應(yīng)能夠擴(kuò)大信息影響力,有效創(chuàng)造良好的口碑。

(4)虛擬社群管理方面。首先鼓勵(lì)高質(zhì)量創(chuàng)作者的宣傳,完善獎(jiǎng)勵(lì)機(jī)制,保證他們持續(xù)多樣內(nèi)容生成和提高內(nèi)容質(zhì)量,留住原有用戶和吸引潛在用戶。其次,利用大數(shù)據(jù)分析等技術(shù)手段,精準(zhǔn)定位用戶需求,提供與需求匹配的個(gè)性化內(nèi)容,不斷提高用戶的使用體驗(yàn)感,從而吸引用戶更多地使用該品牌產(chǎn)品,帶來更強(qiáng)的用戶參與度、體驗(yàn)度與共鳴。最后,完善品牌用戶的會(huì)員機(jī)制,會(huì)員優(yōu)惠福利不僅吸引用戶消費(fèi),也能培養(yǎng)消費(fèi)者的品牌歸屬感。

(5)品牌體驗(yàn)方面。隨著現(xiàn)代社會(huì)逐步進(jìn)入體驗(yàn)經(jīng)濟(jì)時(shí)代,品牌體驗(yàn)對(duì)品牌資產(chǎn)具有重要的影響作用。雖然社交貨幣在網(wǎng)絡(luò)上直接影響品牌口碑和形象,但消費(fèi)者對(duì)品牌產(chǎn)品寄予了諸如感官、情感、社會(huì)等方面的不同線下體驗(yàn)要求,企業(yè)能否準(zhǔn)確、有效地識(shí)別消費(fèi)者不同的要求,最大化地傳遞消費(fèi)者體驗(yàn)價(jià)值,將直接關(guān)乎其品牌資產(chǎn)的增減,而進(jìn)一步帶給企業(yè)的則是市場(chǎng)占有率與企業(yè)收益。現(xiàn)代市場(chǎng)條件下,品牌體驗(yàn)的識(shí)別、塑造與傳遞將對(duì)品牌資產(chǎn)產(chǎn)生重要的作用,這值得研究者和管理者的關(guān)注。